Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

# ПРОЕКТИРОВАНИЕ НА ОСНОВЕ МИКРОКОНТРОЛЛЕРОВ

Рекомендовано УМО вузов Республики Беларусь по образованию в области информатики и радиоэлектроники в качестве учебно-методического пособия для студентов учреждений, обеспечивающих получение высшего образования по специальностям, закрепленным за УМО

УДК 004.3'12(076) ББК 32.973.26-02я73 П79

## Авторы:

М. В. Давыдов, А. Н. Осипов, С. В. Кракасевич, С. К. Дик, Н. С. Давыдова, М. М. Меженная, А. В. Смирнов, А. С. Терех

#### Рецензенты:

доцент кафедры конструирования и производства приборов учреждения образования «Белорусский национальный технический университет», кандидат технических наук Н. Т. Минченя;

доцент кафедры физики полупроводников и наноэлектроники учреждения образования «Белорусский государственный университет», кандидат физико-математических наук И. А. Карпович

П79

**Проектирование** на основе микроконтроллеров : учеб.-метод. пособие / М. В. Давыдов [и др.]. – Минск : БГУИР, 2012. – 92 с. : ил. ISBN 978-985-488-779-1.

Пособие предназначено для закрепления и углубления теоретических знаний, совершенствования практических навыков в области применения информационных технологий при разработке электронной аппаратуры на ПЭВМ с использованием микроконтроллеров.

Представляет собой руководство по курсовому проектированию электронной медицинской аппаратуры с использованием микроконтроллеров.

Для студентов специальностей информатики и радиоэлектроники.

Может быть использовано студентами, обучающимися по специальностям «Медицинская электроника», «Проектирование и производство РЭС», «Электронно-оптические системы и технологии».

УДК 004.3'12(076) ББК 32.973.26-02я73

ISBN 978-985-488-779-1

© УО «Белорусский государственный университет информатики и радиоэлектроники, 2012

# СОДЕРЖАНИЕ

| 1 Обзор литературы                                                      | 5  |

|-------------------------------------------------------------------------|----|

| 1.1 Разработка плана обзора литературы                                  | 5  |

| 1.2 Сбор литературы                                                     | 6  |

| 1.3 Написание обзора                                                    | 7  |

| 1.4 Проблемы, возникающие при выполнении обзора                         | 7  |

| 2 Анализ технического задания                                           | 8  |

| 3 Разработка структурной и функциональной схем устройства               | 9  |

| 3.1 Общие сведения                                                      | 10 |

| 3.2 Алгоритм создания схемы структурной                                 | 10 |

| 4 Разработка схемы электрической принципиальной                         | 12 |

| 4.1 Общие положения                                                     | 12 |

| 4.2 Примеры разработки электрических схем функциональных узлов          | 12 |

| 4.2.1 Программируемый генератор синусоидального сигнала с цифровым      |    |

| потенциометром                                                          | 12 |

| 4.2.2 Усилитель биоэлектрических потенциалов                            | 15 |

| 4.2.3 Аналоговые фильтры на основе модифицированной схемы Саллена-Кея   | 16 |

| 4.3 Выбор элементной базы                                               | 18 |

| 4.4 Оформление схемы электрической принципиальной                       | 20 |

| 4.4.1 Условные буквенно-цифровые обозначения в электрических схемах     | 23 |

| 5 Разработка алгоритма работы микроконтроллера                          | 27 |

| 5.1 Понятие алгоритма и его свойства                                    | 27 |

| 5.2 Представление алгоритма в виде блок-схем. Правила оформления        | 28 |

| 5.3 Поток управления действиями алгоритма и способы его организации     | 31 |

| 5.4 Концептуальный и функциональный алгоритмы                           | 33 |

| 6 Разработка программы для микроконтроллеров Cygnal                     | 37 |

| 6.1 Краткий обзор микроконтроллера Cygnal семейства C8051F320           | 37 |

| 6.1.1 Процессорное ядро СІР-51                                          | 37 |

| 6.1.2 Программируемые цифровые порты ввода/вывода и матрица соединений  | 38 |

| 6.1.3 Последовательные порты                                            | 39 |

| 6.1.4 10-разрядный аналого-цифровой преобразователь                     | 39 |

| 6.1.5 Предельно допустимые параметры                                    | 40 |

| 6.2 Система команд микроконтроллеров с ядром CIP-51                     | 41 |

| 6.3 Обработка прерываний в микроконтроллерах Cygnal семейства C8051F320 | 49 |

| 6.3.1 Задержка обработки прерывания                                     | 49 |

| 6.4 Порты ввода/вывода в микроконтроллерах Cygnal семейства C8051F320   | 51 |

| 6.4.1 Приоритетный декодер матрицы                                      | 52 |

| 6.4.2 Порт ввода/вывода общего назначения                               | 55 |

| 6.4.3 Пример программы для работы с портами ввода-вывода                | 56 |

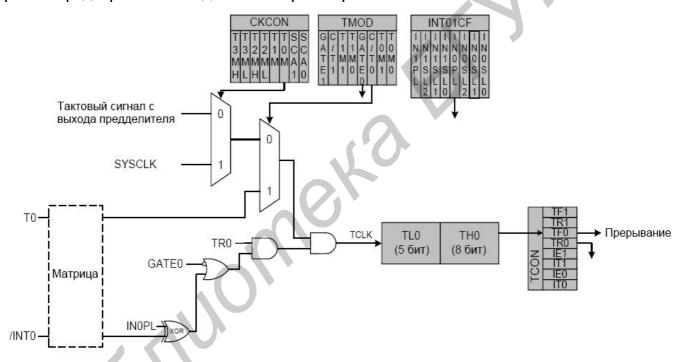

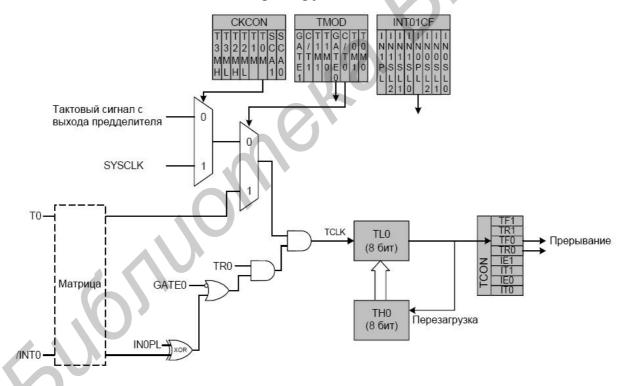

| 6.5 Таймер/счетчики в микроконтроллерах Cygnal семейства C8051F320      | 58 |

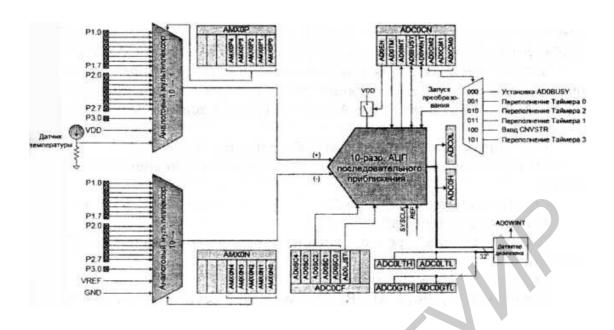

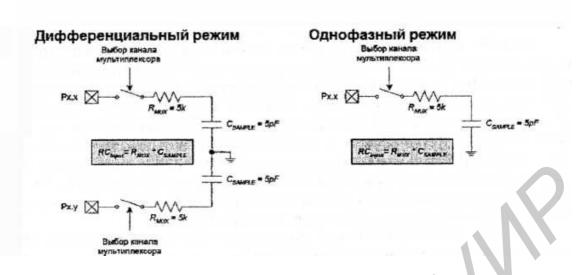

| 6.6 10-разрядный АЦП (АЦП0).                                            | 63 |

| 6.7 Универсальный асинхронный приемопередатчик                          | 68 |

| 6.7.1 Усовершенствованный режим генерации скорости передачи данных | 69 |

|--------------------------------------------------------------------|----|

| 6.7.2 Режимы работы UART0                                          | 71 |

| 6.7.3 9-разрядный UART                                             | 72 |

| ПРИЛОЖЕНИЕ А Описание регистров прерываний                         |    |

## 1 Обзор литературы

Прежде чем писать обзор литературы, необходимо четко сформулировать тему и цель курсового проекта. Назначение обзора, в первую очередь, заключается в описании того, что уже сделано по заданной теме, в нашем случае, по теме медицинской электроники, диагностических методов исследований или методов терапевтического воздействия, а также путей их технической реализации. Более того, в обзоре литературы по возможности должна быть обоснована необходимость проведения технической разработки. То есть нужно показать, что разработка данного медицинского аппарата актуальна и перспективна, поскольку до настоящего момента не проводилась или проводилась в недостаточном объеме.

### 1.1 Разработка плана обзора литературы

Исходя из темы и цели курсового проекта необходимо составить план литературного обзора. Составление плана позволяет четко представить себе, какую именно литературу нужно собрать. Благодаря этому впоследствии удобно будет работать над каждым пунктом обзора отдельно. План должен быть изложен максимально подробно. В соответствии с планом в дальнейшем можно разбить обзор на параграфы, что, вопервых, упростит его восприятие, во-вторых, позволит создать некую внутреннюю логику обзора, в которой отразится его идея. Наличие плана значительно улучшит впечатление от работы.

Прежде чем составлять план обзора, помимо выработки основной идеи необходимо хотя бы в общих чертах представлять, какая литература имеется в наличии, т. е. необходимо учесть реальность выполнения плана. Зачастую этому способствует чтение других обзоров по изучаемой теме. Нередко в процессе работы план может видоизменяться в результате добавления новых частей или удаления тех, что не несут смысловой нагрузки или не выполнены из-за отсутствия нужной литературы. Однако все время необходимо помнить, что план должен отражать основную идею литературного обзора.

План обзора литературы обсуждается с руководителем курсового проектирования. Это позволяет не только выработать лучший вариант плана, но и значительно уменьшить объем исправлений в процессе сдачи курсового проекта. Если руководитель хочет внести в план дополнительный пункт, литературу по которому вы не можете найти, необходимо уточнить, к каким источникам следует для этого обратиться.

В общем виде план обзора будет включать три основных пункта.

- 1 Общая характеристика заболевания и патологических процессов, протекающих в организме человека, для лечения или диагностики которых производится разработка прибора или аппарата.

- 2 Конкретные медицинские методики (последовательность действий, режимы и параметры стимулирующих воздействий, методики диагностики и контроля), используемые при указанном заболевании.

- 3 Технические характеристики и режимы работы уже выпускаемых приборов и аппаратов для диагностики или лечения указанного заболевания. По возможности следует рассмотреть структурные и электрические принципиальные схемы, интерфейсы взаи-

модействия с пользователем, сравнить преимущества и недостатки существующих устройств.

В конце обзора делается заключение, в котором указывается методика, которая будет реализована в приборе, а также основные технические характеристики или режимы работы прибора. На основании этой информации производится анализ технического задания.

## 1.2 Сбор литературы

Сбор литературы — это важнейший этап выполнения литературного обзора, который равен по своей значимости половине всей работы. Однако в отличие от написания обзора, которое требует значительной затраты времени, основная работа по сбору литературы, как правило, выполняется в короткие сроки. Особенно это актуально для иногородних студентов, не имеющих возможности долго находиться в Минске. Приведенный ниже алгоритм действий поможет сократить время выполнения этой части работы без потери качества ее исполнения.

Поиск литературы в электронном каталоге

Сформулируйте термины, по которым вы хотите найти литературу. Помните, что при формулировании слишком узких понятий вы рискуете не найти достаточного количества литературы. Это часто случается при поиске информации о конкретных схемах устройств или малоизвестных методах лечения заболеваний. В этом случае необходимо попытаться найти информацию о группе, к которой относится это устройство или метод. Укажите все известные синонимы интересующего вас термина.

Например, необходимо собрать литературу по теме «Многоканальная программируемая электростимуляция мышц». Для поиска информации можно использовать Интернет поисковики Google.com, yandex.ru, rambler.ru и т. д. Поиск в Интернете будет включать следующий примерный перечень терминов:

«электростимуляция»,

«электростимуляция мышц»,

«многоканальная электростимуляция»,

«методики многоканальной электростимуляции»,

«аппарат электростимуляции»,

«аппарат для многоканальной электростимуляции» и т. д., так как при поиске, как правило, дополнительно используются термины из найденных источников.

Кроме того, информацию по заданной теме можно найти в Национальной библиотеке Беларуси (г. Минск, пр-т Независимости, 116), Республиканской научной медицинской библиотеке (г. Минск, ул. Фабрициуса, 28), Республиканской научно-технической библиотеке, (г. Минск, пр-т Победителей, 7) и т. д.

Реальность такова, что почти все обзоры литературы создаются с использованием чужих литературных обзоров по заданной теме. Однако далеко не всегда находятся обзоры, в точности соответствующие теме, поэтому приходится использовать несколько исходных литературных обзоров. Кроме того, отдельные вопросы в этих обзорах могут быть не освещены вообще. Наконец, с момента написания предшествующих обзоров до момента выполнения вами обзора литературы проходит значительное время, за которое выпускается новая литература, которая также может быть использована при создании обзора. Писать обзор литературы исключительно путем синтеза предшествующих обзоров — это mauvais ton («плохой тон», франц.). Чем больше в работе самостоятельно до-

бытых данных, тем выше ее качество.

Чем больше исходных литературных обзоров будет использовано, тем полнее будет изложен материал и тем легче будет добиться того, чтобы литературный обзор не походил на предшествовавшие ему обзоры. Однако отбирать необходимо только те обзоры, в которых действительно содержится полезная информация. Кроме того, предпочтение нужно отдавать обзорам, содержащим более свежие ссылки. Особое внимание следует обращать на то, что новые литературные обзоры пишутся с использованием старых и значительная доля информации в них может дублироваться.

### 1.3 Написание обзора

Написание – наиболее сложный и длительный этап подготовки обзора.

Ниже изложен алгоритм действий, позволяющий выполнить эту работу с минимальными затратами времени.

Создайте файл Word, в котором будет в дальнейшем создаваться обзор. В этом файле напишите крупным шрифтом заголовки и подзаголовки, соответствующие плану обзора.

Скопируйте все отсканированные вами обзоры в отдельные файлы и внимательно перечитайте их, разбейте на части таким образом, чтобы в каждой из них содержалась отдельная идея. Желательно, чтобы они соответствовали плану вашего обзора. При этом весь ненужный материал следует удалить, а материал, который может хоть как-нибудь пригодиться, необходимо сохранить и озаглавить.

Если ссылки на источники в тексте обзоров представлены в виде цифр, необходимо либо поменять их на фамилии, либо, выделив весь текст, изменить его цвет (кнопки «цвет шрифта») так, чтобы каждому обзору соответствовал свой цвет. Это делается для того, чтобы в дальнейшем можно было составить список литературы и расставить ссылки по ходу текста. Если ссылки представлены в виде «фамилия+год», проверьте, чтобы по ним можно было в дальнейшем найти источники в списке литературы.

Скопируйте из получившихся файлов литературу в файл с обзором и рассортируйте ее в соответствии с планом вашего обзора. Скопируйте также дополнительный материал, собранный вами из журналов и сборников, и распределите по тексту обзора. Не забудьте, что каждый абзац должен содержать ссылку на источник.

В дальнейшем работа ведется отдельно с каждым параграфом обзора. Необходимо разбить каждый параграф на максимальное количество пунктов. При этом нужно следить, чтобы текст был связным и логичным как внутри параграфов, так и между ними и соответствовал общей идейной линии обзора. Для этого необходимо изменять формулировки, использовавшиеся во взятых Вами за основу обзорах. Кроме того, это необходимо сделать для того, чтобы Ваш обзор не создавал такого впечатления, что он списан с чужих обзоров. Также следует учитывать, что разные обзоры пишутся в разных стилях, тогда как ваш итоговый обзор должен быть написан в одном.

## 1.4 Проблемы, возникающие при выполнении обзора

При поиске как отечественной, так и зарубежной литературы обращайте внимание на используемые вами поисковые слова: проблемы с поиском литературы могут быть обусловлены употреблением неправильных терминов.

По целому ряду направлений российскими разработчиками сделано гораздо меньше исследований, чем иностранными. Поэтому, если вы не нашли отечественной литературы по теме, возможно, вам удастся обнаружить иностранную литературу.

Если вам все-таки не удалось обнаружить литературу по вашей теме, необходимо скорректировать план обора исходя из реальных возможностей. При этом сложившаяся ситуация должна быть своевременно обсуждена с руководителем.

### 2 Анализ технического задания

В пункте «Анализ технического задания» производится постановка задачи, выполняемой в курсовом проекте, выбор методов решения поставленной задачи. Содержание этого раздела должно быть достаточным для принятия конкретных технических решений и разработки структурной схемы.

Анализ технического задания (ТЗ) на проведение курсового проектирования (КП) включает следующие разделы.

- 1 Вводные данные.

- 1.1 Наименование КП.

- 1.2 Срок выполнения КП.

- 2 Цель выполнения КП.

- 3 Технические требования к изделию.

- 3.1 Состав изделия. Необходимо указать, из каких составных частей будет состоять разрабатываемый прибор. Данный пункт можно выполнить с разной глубиной детализации. Например для терапевтического прибора можно указать комплектность поставки: блок электростимулятора, система электродов, блок питания (при внешнем блоке питания). Можно сделать более детальный анализ составных частей, рассмотрев отдельные составные части блока электростимуляции. Например, в данной ситуации могут быть добавлены: блок управления, блок генерации стимулирующего сигнала, блок усиления, блок индикации, клавиатура.

- 3.2 Назначение прибора. Необходимо четко сформулировать, для чего будет применяться прибор. Назначение устройства непосредственно влияет на его технические особенности. При анализе этого пункта необходимо указать диапазоны значений рабочих характеристик устройства, учесть условия эксплуатации, обосновать эксплуатационно-технические требования к проектируемому устройству. К таким требованиям относятся:

- диапазон рабочих частот;

- характер передаваемой информации;

- мощность передающих устройств;

- чувствительность приемных устройств.

- 3.3 Функции прибора. В данном разделе необходимо рассмотреть последовательность действий, выполняемых прибором. Например, для диагностического прибора можно выделить следующие функции:

- выполнение пользовательских настроек (выбор количества каналов регистрации данных, выбор длительности регистрируемых данных, выбор алгоритмов обработки данных и т. д.);

- выполнение диагностической процедуры, оцифровка и сохранение данных в па-

### мяти прибора;

- расчет выбранных диагностических показателей;

- отображение диагностических показателей;

- вывод информации на внешние носители или на персональный компьютер.

- 3.4 Метрологические характеристики (точность измерений, погрешности задания амплитуд стимулирующих сигналов и т. д.)

- 3.5 Требования к электропитанию (стационарный прибор питание от сети 220 В; переносной возможность питания от батарей; бортовой или автомобильный прибор питание от аккумулятора автомобиля 12 13 В).

### 4 Этапы выполнения КП.

Все требования технического задания тщательно обосновываются (желательны ссылки на соответствующие ГОСТы, ТУ и другие нормативные документы, а также стандарты ISO, IEC, ETSI, CENELEC, EBU, рекомендации и отчеты ITU-R, ITU-T). При необходимости производится разработка дополнительных требований, которые в ряде случаев подтверждаются расчетами и ссылками на литературные источники. Приводятся характеристики входных и выходных сигналов, рассматривается возможность использования унифицированных узлов и блоков, применения интегральных схем и т. д.

### 3 Разработка структурной и функциональной схем устройства

#### 3.1 Общие сведения

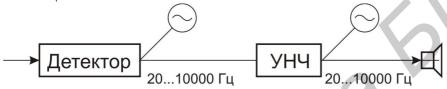

Электрическая структурная схема отражает основные функциональные части изделия (элементы, устройства, функциональные группы), их назначение и связи. Все функциональные части на схеме изображают в виде прямоугольников или условных графических обозначений (УГО). Если функциональных частей много, вместо наименований, типов и обозначений допускается проставлять порядковые номера справа от изображения или над ним, как правило, сверху вниз в направлении слева направо с их расшифровкой в таблице, помещаемой на схеме. На схеме даются поясняющие надписи, диаграммы, таблицы, указания параметров в характерных точках (величины токов, напряжений, формы и величины импульсов) (рисунок 3.1), математические зависимости и т. п.

На функциональной схеме изображают функциональные части изделия (элементы устройства и функциональные группы) и связи между ними с разъяснением последовательности процессов, протекающих в отдельных функциональных цепях изделия или в изделии в целом.

Рисунок 3.1 – Пример расположения параметров в характерных точках

Функциональные части схемы принято изображать в виде условных обозначений либо прямоугольников с указанием:

- позиционных обозначений функциональных групп, устройств, элементов, присвоенных им на принципиальной схеме, и их наименований;

- типов;

- обозначений документов, на основании которых функциональные части применены;

- технических характеристик функциональных частей;

- поясняющих надписей, диаграмм, таблиц, параметров в характерных точках.

Эти сведения приводятся выборочно в объеме, необходимом для наиболее полного и наглядного представления о последовательности процессов, иллюстрируемых схемой. Наименования, типы и обозначения рекомендуется вписывать в прямоугольники.

## 3.2 Алгоритм создания схемы структурной

Разработка схемы структурной ведется в соответствии с пунктами 3.1-3.2. На основании выделенных составных частей и функций прибора определяются его структурные блоки.

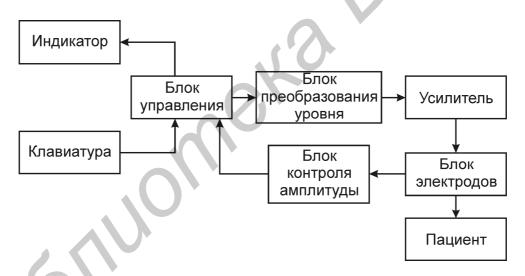

Например, рассмотрим функции миостимулятора и выделим структурные блоки для их реализации:

| N₂ | Структурный блок прибора    | Функция прибора             |

|----|-----------------------------|-----------------------------|

| 1  | Блок управления             | Управление работой аппарата |

| 2  | Клавиатура аппарата         | Ввод параметров             |

|    |                             | стимулирующих токов         |

| 3  | Дисплей аппарата            | Отображение текущего        |

|    |                             | режима                      |

| 4  | Блок управления на основе   | Генерация стимулирующего    |

|    | микроконтроллера, или       | сигнала                     |

|    | специальный блок генератора |                             |

| 5  | Блок преобразования уровня  | Преобразование сигнала      |

| 6  | Усилитель                   | Усиление сигнала            |

| 7  | Электроды                   | Подача стимулирующего тока  |

|    |                             | на пациента                 |

| 8  | Блок контроля амплитуды     | Контроль амплитуды          |

|    |                             | стимулирующего тока         |

Далее необходимо проанализировать направление связей в структурной схеме прибора, проанализировать уровни и частотные характеристики сигналов и начертить схему (рисунок 3.2).

Рисунок 3.2 – Структурная схема

Дополнительно на схему можно нанести надписи, поясняющие работу схемы, в виде технических характеристик функциональных частей, диаграмм, таблиц, параметров сигналов в характерных точках и другой дополнительной информации, которая может помочь при защите курсового проекта.

### 4 Разработка схемы электрической принципиальной

#### 4.1 Общие положения

Схема электрическая принципиальная — схема, определяющая полный состав элементов и связей между ними и, как правило, дающая детальное представление о принципах работы изделия. Данная схема отражает взаимные связи между отдельными электрическими компонентами, устройствами, аппаратами или приборами с учетом принципа действия и последовательности работы отдельных ее элементов. Схема электрическая принципиальная разрабатывается на основе технического задания, структурной или функциональной схемы устройства следующим образом.

- 1 Определяются отдельные функциональные узлы устройств (блок питания, генератор сигнала, усилитель сигнала, АЦП, ЦАП, датчик, устройство индикации, контроля и т. д.) и технические требования к ним.

- 2 Для каждого функционального узла выбирается электрическая схема и производится расчет последней в соответствии с техническими требованиями (напряжение питания, потребляемая мощность, форма и вид сигнала, частота сигнала, нагрузочная способность и т. д.).

- 3 Осуществляется согласование электрических характеристик (по уровню питания, амплитуде и частоте сигнала, входному и выходному сопротивлению и т. д.) рассчитанных схем функциональных узлов устройства.

- 4 В соответствии с параметрами полученной электрической схемы устройства выбирается подходящая элементная база (аналоговые и цифровые компоненты, устройства, элементы индикации, коммутации и т. д.).

- 5 В соответствии со стандартами ЕСКД оформляется графический материал схемы электрической принципиальной и перечень элементов.

# 4.2 Примеры разработки электрических схем функциональных узлов

# 4.2.1 Программируемый генератор синусоидального сигнала с цифровым потенциометром

При необходимости разработки генератора синусоидального сигнала часто встает вопрос о программном управлении частотой сигнала посредством цифрового интерфейса. Для этого могут использоваться схемы на основе цифровых потенциометров (ЦП), положение подвижного контакта которых определяется цифровым кодом, записанным в специализированные регистры последнего. Чаще всего используются три типа шин управления ЦП: SPI, I2C и UDC.

Цифровые потенциометры являются довольно универсальными устройствами и могут применяться в фильтрах и генераторах. В таких случаях разработчик должен всегда иметь в виду, что цифровые потенциометры работают в ограниченном частотном диапазоне и этот диапазон зависит от установленной величины сопротивления, поэтому необходимо внимательно сверяться с данными, опубликованными в техническом описании. Если требования по частоте удовлетворяются, то такой потенциометр может быть с успехом использован для реализации генератора с установкой частоты посредством цифрового интерфейса.

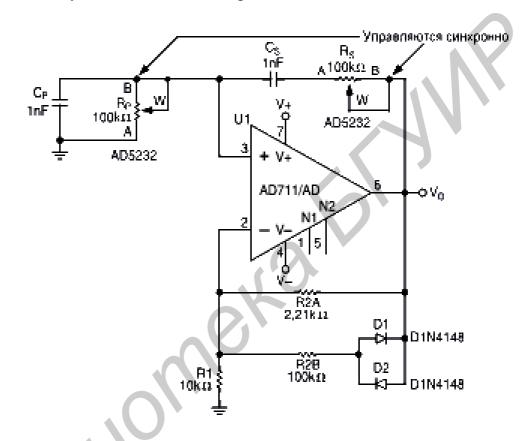

На рисунке 4.1 показана схема генератора на основе моста Вина с цепью стабилизации амплитуды и с ЦП в цепи частотно-зависимой обратной связи. Для аналоговых генераторов гармонических колебаний важной проблемой является автоматическая стабилизация амплитуды выходного напряжения. Если в схеме не предусмотрены устройства автоматической стабилизации, устойчивая работа генератора окажется невозможной. В этом случае после возникновения колебаний амплитуда выходного напряжения начнет постоянно увеличиваться, и это приведет к тому, что активный элемент генератора (например операционный усилитель) войдет в режим насыщения. В результате напряжение на выходе будет отличаться от гармонического.

Рисунок 4.1 – Пример программируемого генератора с цифровым потенциометром

В представленной схеме самовозбуждение генератора (т.е. выполнение условия баланса амплитуд операционного усилителя) возможно только при выполнении следующего условия: операционный усилитель по неинвертирующему входу должен иметь коэффициент усиления K=3 на частоте резонанса моста Вина. Элементы R1 и R2 предназначены для получения требуемого коэффициента усиления усилительного звена. Амплитуда стабилизируется за счет диодов D1 и D2, которые открываются при росте амплитуды выходного сигнала.

Частота генерируемого сигнала равна

$$f = \frac{1}{2\pi \cdot R \cdot C},$$

где

$$R=R_p=R_s$$

,  $C=C_p=C_s$ .

Сопротивление цифрового потенциометра, в регистр которого записана величина D, составляет

$$R_{AW} = \frac{2^{N} - D}{2^{N}} \cdot R_{AB} + 50,$$

где  $R_{AB}$  — полное сопротивление ЦП, т. е. сопротивление между выводами A и B; N — разрядность регистра ЦП;

$R_{AW}$  — сопротивление введенной части потенциометра между выводами A и W, 50 Ом — сопротивление подвижного контакта, т. е. приблизительное значение сопротивления открытого транзисторного ключа ЦП.

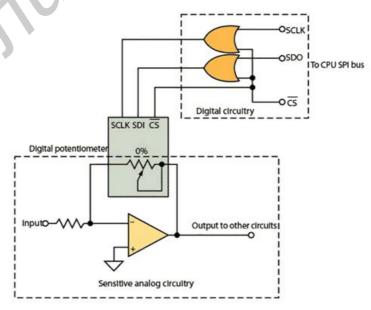

Одна из возможных проблем, связанных с использованием цифровых потенциометров, заключается в проникновении шумов цифровых линий управления в аналоговые цепи. Такое может произойти при неудачной трассировке печатной платы, если дорожки цифровых сигналов расположены слишком близко к аналоговым. Поскольку обмен данными по цифровым шинам происходит, как правило, весьма активно, чувствительные аналоговые цепи будут испытывать постоянное воздействие шумов.

На рисунке 4.2 представлена схема, в которой ЦП используется для изменения коэффициента усиления операционного усилителя и в которой демонстрирует простое решение указанной проблемы. В данном примере потенциометр управляется по последовательному интерфейсу SPI, но не меньшее распространение имеет интерфейс I<sup>2</sup>C. Идущие от контроллера сигналы SCLK и SDO шины SPI пропускают через логические элементы «2ИЛИ», благодаря которым цифровой потенциометр «видит» сигналы SCLK и SDO только при наличии низкого уровня на входе разрешения потенциометра (CS), т.е. тогда, когда выполняется перенастройка потенциометра.

Такое решение позволяет оградить аналоговые цепи от воздействия высокочастотных сигналов шины управления в течение всего времени, пока не требуется перенастройка цифрового потенциометра.

Таким образом, шумы перестают быть проблемой для схем, которые не нуждаются в частом перепрограммировании параметров, например, для схем начальной инициализации.

# Рисунок 4.2 — Пример организации защиты от проникновения шумов цифровых линий управления в аналоговые цепи

### 4.2.2 Усилитель биоэлектрических потенциалов

Качество электронной системы съема, усиления и регистрации биопотенциалов во многом определяется параметрами входной цепи, образованной электродами отведений и резистивными суммирующими схемами, а также параметрами входных каскадов усиления.

Свойства входной цепи определяют степень подавления синфазных помех, вызванных наводками от силовой и осветительной сети и электрических установок. Неодинаковое для разных электродов изменение во времени сопротивления кожа—электрод совместно с нестабильностями электрических параметров электродов приводит к изменению коэффициента передачи входной цепи по постоянному току и искажению АЧХ системы электрод—вход усилителя биопотенциалов. При этом может происходить преобразование синфазной помехи в разностную, которая, складываясь с полезным сигналом, имеет аддитивный характер.

На входные цепи усилителей биоэлектрических сигналов наряду с воздействием синфазных и разностных помех от физических источников (сети питания, электросиловых приборов) воздействуют синфазные и разностные помехи биологического происхождения (артефакты). Снижение влияния синфазных биологических и физических помех достигается применением усилителей с достаточно большим коэффициентом подавления этих помех. Устранение влияния противофазных физических помех и наводок достигается уменьшением площади замкнутого контура, образованного проводами отведений, и применением методов экранирования.

Проблема подавления противофазных помех биологического происхождения, вызванных работой других органов и систем биообъекта, кроме интересующих исследователя, более сложна и требует применения систем фильтрации и специальных методик регистрации сигналов.

В качестве усилителей биоэлектрических сигналов широко используются усилители постоянного тока с непосредственными связями. Входные каскады усилителей выполняются по симметричным дифференциальным схемам, обеспечивающим высокий уровень подавления синфазных помех.

Для уменьшения влияния синфазных помех применяются специальные компенсационные схемы. Ввиду сравнительно малого сопротивления тканей биообъекта величина синфазной помехи на всей его поверхности практически одинакова. Напряжение синфазной помехи снимается с одного или нескольких активных электродов и подается на инвертирующий усилитель, выход которого подключается через индифферентный электрод между биообъектом и общим проводом.

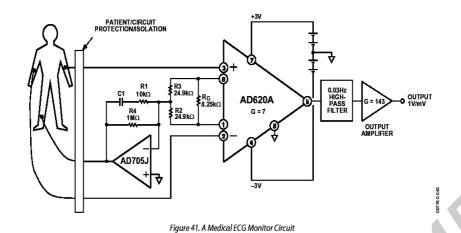

На рисунке 4.3 показана типовая схема усилителя биопотенциалов со схемой компенсации синфазной помехи на базе инструментального усилителя AD620 (схема рекомендована производителем Analog Devices).

Рисунок 4.3 — Усилитель биопотенциалов со схемой компенсации синфазной помехи

В качестве инструментального усилителя применен AD620 — недорогой усилитель с высокой точностью и превосходными характеристиками на постоянном токе: коэффициент ослабления синфазного сигнала CMR >> 100 дБ на частотах вплоть до 1 кГц, смещение на входе не более 50 мкВ, малый входной ток (1 нА макс.) и низкое напряжение шума (0,28 мкВ в полосе 0,1...10 Гц). Для AD620 требуется единственный внешний резистор  $R_G$ , задающий коэффициент усиления (при условии, что  $R_2$  и  $R_3$  равны 24,9 кОм):

$$G = \frac{49.4}{R_G} + 1 \text{ (кOм)}.$$

В схеме обратной связи, предназначенной для компенсации синфазного сигнала, может быть применен операционный усилитель типа ОР97 — малопотребляющий прецизионный ОУ с чрезвычайно высоким коэффициентом ослабления синфазного сигнала (мин. значение 114 дБ). Эта схема подает на пациента напряжение, компенсирующее синфазную составляющую сигнала с целью устранить влияние синфазного сигнала.

Далее в усилительный тракт необходимо включить ФВЧ для устранения постоянной составляющей в спектре полезного сигнала и схему основного усиления на базе операционного усилителя.

# 4.2.3 Аналоговые фильтры на основе модифицированной схемы Саллена–Кея

Распространенной задачей при разработке электронных систем является задача выделения или подавления сигнала заданного частотного диапазона из сигнала более широкого спектрального состава. С этой целью используются фильтры, которые делятся на аналоговые и цифровые. Наиболее распространенными типами аналоговых фильтров являются: Чебышева, Баттервофа и Бесселя (также называемый фильтр Томпсона). Каждый из них оптимизирован по различным параметрам. Сложность каждого фильтра определяется выбранным числом полюсов. Чем больше полюсов в фильтре, тем сложнее электроника и лучше характеристики.

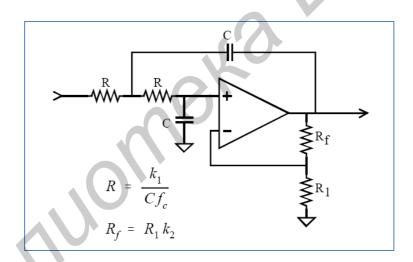

На рисунке 4.4 показано типичное построение аналогового фильтра, выполненного по модернизированной схеме Саллена—Кея. На схеме представлен двухполюсный низкочастотный (low-pass) фильтр, который может быть сконфигурирован под любой базовый тип фильтра. В таблице 4.1 представлена необходимая информация для выбора коэффициентов  $k_1$  и  $k_2$ , далее выбираются параметры соответствующих резисторов и емкостей ( $R_I$  и C) и рассчитываются параметры резисторов R и  $R_f$  для частоты отсечки  $f_c$  в  $\Gamma$ ц:

$$R = \frac{k_1}{c * f_c}, \qquad R_f = R_1 k_2,$$

где  $k_1$  и  $k_2$  — коэффициенты (выбираются из таблицы 4.1);  $R_1$  и C — номиналы емкостей и резисторов (задаются произвольно);  $f_c$  — частота отсечки фильтра.

Например, для создания 1 кГц 2-полюсного фильтра Баттервофа из таблицы 4.1 выбираем коэффициенты  $k_1 = 0,1592$  и  $k_2 = 0,586$ . Произвольно выбираем  $R_1 = 10$  К и C = 0,01 µF (обычные величины для схем с операционным усилителем), R и  $R_f$  вычисляются как величины, равные 15,95 К и 5,86 К соответственно. Округляем их до ближайшего значения 1 %-ную стандартных резисторов и получаем R = 15,8 К и  $R_f = 5,90$  К. Все компоненты должны иметь 1 % точность или выше.

Рисунок 4.4 — Схема активного фильтра на основе модифицированной схемы Саллена—Кея

На рисунке 4.4 показана схема 2-полюсного низкочастотного фильтра. Фильтры с большим числом полюсов получаются последовательным соединением каскадов. Коэффициенты  $k_1$  и  $k_2$  определяются из таблицы 4.1, произвольно выбираются  $R_1$  и C (10 К и 0,01 µF), а затем вычисляются R и  $R_f$  по формулам на рисунке 4.4, где  $f_c$  — частота отсечки в  $\Gamma$ ц.

| Таблица 4 1 – | Коэффициенты | ппя созлания   | фильтров  |

|---------------|--------------|----------------|-----------|

| тиолици т.т   | тоэффициситы | . дли создании | ψημησιρου |

|   |                                          |                                      |                                  |                                      | •                                | /                                    |                                  |  |

|---|------------------------------------------|--------------------------------------|----------------------------------|--------------------------------------|----------------------------------|--------------------------------------|----------------------------------|--|

| # | poles                                    | Besse                                |                                  | Butter                               | -                                | Cheby                                | •                                |  |

| π | pores                                    | $\mathbf{k_1}$                       | $\mathbf{K_2}$                   | $\mathbf{k_1}$                       | $\mathbf{k_2}$                   | <b>K</b> <sub>1</sub>                | K <sub>2</sub>                   |  |

| 2 | stage 1                                  | 0.1251                               | 0.268                            | 0.1592                               | 0.586                            | 0.1293                               | 0.842                            |  |

| 4 | stage 1<br>stage 2                       | $0.1111 \\ 0.0991$                   | 0.084<br>0.759                   | 0.1592<br>0.1592                     | 0.152<br>1.235                   | 0.2666<br>0.1544                     | 0.582<br>1.660                   |  |

| 6 | stage 1<br>stage 2<br>stage 3            | 0.0990<br>0.0941<br>0.0834           | 0.040<br>0.364<br>1.023          | 0.1592<br>0.1592<br>0.1592           | 0.068<br>0.586<br>1.483          | 0.4019<br>0.2072<br>0.1574           | 0.537<br>1.448<br>1.846          |  |

| 8 | stage 1<br>stage 2<br>stage 3<br>stage 4 | 0.0894<br>0.0867<br>0.0814<br>0.0726 | 0.024<br>0.213<br>0.593<br>1.184 | 0.1592<br>0.1592<br>0.1592<br>0.1592 | 0.038<br>0.337<br>0.889<br>1.610 | 0.5359<br>0.2657<br>0.1848<br>0.1582 | 0.522<br>1.379<br>1.711<br>1.913 |  |

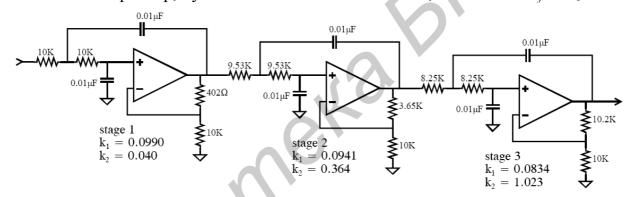

Четырех-, шести-, восьмиполюсные фильтры формируются последовательным включением двух, трех и четырех каскадов соответственно. Например, на рисунке 4.5 показана схема 6-полюсного фильтра Бесселя, выполненного последовательным включением 3-х каскадов. Каждый каскад имеет различные коэффициенты  $k_1$  и  $k_2$  согласно таблице 4.1, и, соответственно, различные конденсаторы и емкости. Если необходим высокочастотный фильтр, нужно поменять местами R и C, не изменяя  $R_f$  и  $R_1$ .

Рисунок 4.5 – Каскадное выполнение 6-полюсного фильтра Бесселя из 3 схем Саллена–Кея (низкочастотный фильтр с частотой отсечки 1 кГц)

# 4.3 Выбор элементной базы

В процессе разработки технического устройства необходимо учитывать не только технические, но и экономические показатели будущего прибора: в конструируемом устройстве необходимо сочетание минимальных затрат на производство прибора (а в них входит и стоимость элементной базы), максимальных показателей производительности (функциональности) и качества. Для этого подходить к проектированию следует так, как к разработке прибора, который будет в дальнейшем изготовлен.

Выбор элементной базы проводится на основе схемы электрической принципиальной с учетом изложенных в техническом задании условий и требований. Эксплуатационная надежность элементной базы в основном определяется правильным выбором типа элементов при проектировании и при использовании в режимах, которые не превышают предельно допустимых.

Для правильного выбора типа электронных компонентов необходимо на основе требований по установке, в частности климатических, механических и др. влияний, проанализировать условия работы каждого элемента и определить:

- эксплуатационные факторы (интервал рабочих температур, относительную влажность окружающей среды, атмосферное давление, механические нагрузки и др.);

- значения параметров и их разрешенные изменения в процессе эксплуатации (номинальное значение, допуск, сопротивление изоляции, шумы, вид функциональной характеристики и др.);

- разрешенные режимы и рабочие электрические нагрузки (мощность, напряжение, частота, параметры импульсного режима и др.);

- показатели надежности, долговечности и срока сохранения.

Критерием выбора в устройстве элементной базы является соответствие технологических и эксплуатационных характеристик электронных компонентов заданным условиями работы и эксплуатации.

Основными параметрами при выборе элементной базы являются:

- 1) технические параметры:

- номинальное значение параметров электронных компонентов согласно принципиальной электрической схеме прибора;

- допустимые отклонения величины электронных компонентов от их номинального значения;

- допустимое рабочее напряжение электронных компонентов;

- допустимая мощность рассеивания электронных компонентов;

- диапазон рабочих частот электронных компонентов;

- коэффициент электрической нагрузки электронных компонентов;

- 2) эксплуатационные параметры:

- диапазон рабочих температур;

- относительная влажность воздуха;

- атмосферное давление;

- вибрационные нагрузки;

- другие показатели.

Дополнительными критериями при выборе элементной базы являются:

- унификация электронных компонентов;

- масса и габариты электронных компонентов;

- наименьшая стоимость.

Выбор элементной базы по вышеназванным критериям позволяет обеспечить надежную работу изделия.

Следует отметить, что электронная промышленность является одной из самых динамичных отраслей в мировой экономике, и информация о новых выпускаемых компонентах появляется буквально каждую неделю. Поэтому разработчик должен отслеживать такие изменения, чтобы не пропустить важную новую информацию.

Традиционными источниками информации для разработчиков являются технические справочники, научно-технические журналы, документация фирм-производителей. В последние годы документация стала появляться не только в виде книг, но и на компакт-дисках. Перечисленные источники обладают как достоинствами, так и недостатками.

Справочники общего характера обычно предоставляют лишь краткую информацию о компонентах. Этих сведений обычно недостаточно и требуется дополнительная документация.

Журналы обычно содержат краткие обзоры конкретных типов электронных компонентов, в том числе и новых. Эту информацию следует рассматривать как сигнальную.

Документация фирм-производителей является наиболее полной и достоверной. Документация делится в основном на сигнальную информацию (Short Form), технические данные (Data Sheet) и рекомендации по применению (Application Note). Часто имеются дополнительные издания с примерами применения.

Основным недостатком всех перечисленных типов информации является отсутствие сведений о последних разработках.

В связи с вышесказанным, для разработчика электронного оборудования необходим такой источник информации, который сочетал бы в себе возможность поиска и сравнения различных электронных компонентов (справочник), при необходимости получение подробных сведений о конкретных электронных компонентах (документация фирм-производителей) и кроме этого обеспечивал бы возможность получения сведений о любых появляющихся новых компонентах. Единственным источником технической информации, удовлетворяющим вышеперечисленным требованиям, является мировая компьютерная сеть Internet. В настоящее время практически все производители электронных компонентов имеют электронные базы данных компонентов, которые регулярно обновляются по мере поступления на рынок новых компонентов. Имеется также информация о таких изделиях, которые только планируются к выпуску или находятся на этапе тестирования. Кроме этого, такие базы данных имеют средства быстрого поиска по названию или типу компонента. При необходимости можно воспользоваться службой технической поддержки фирм.

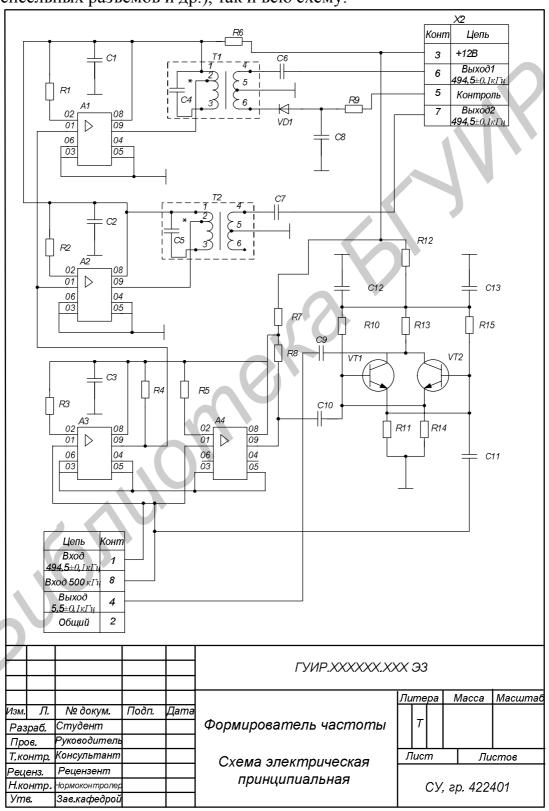

## 4.4 Оформление схемы электрической принципиальной

Принципиальная схема является наиболее полной электрической схемой изделия, на которой изображают все электрические элементы и устройства, необходимые для осуществления и контроля в изделии заданных электрических процессов, все связи между ними, а также элементы подключения (разъемы, зажимы), которыми заканчиваются входные и выходные цепи. На схеме могут быть изображены соединительные и монтажные элементы, устанавливаемые в изделии по конструктивным соображениям.

Электрические элементы на схеме изображают условными графическими обозначениями, начертание и размеры которых установлены в стандартах ЕСКД [СТП 01–2010]. Элементы, используемые в изделии частично, допускается изображать не полностью, а только используемые части.

Двоичные логические элементы на схеме изображают в виде УГО, построенных по правилам, установленным ГОСТ 2.743–82. Номера контактов устройств указываются над линиями связи рядом с соответствующими УГО логических элементов.

Схемы выполняют для изделий, находящихся в отключенном положении, в соответствии с рисунком 4.6. В технически обоснованных случаях допускается отдельные элементы схемы изображать в выбранном рабочем положении с указанием поля режима этих элементов.

В состав схемы кроме изображения входят надписи, характеризующие входные и выходные цепи, позиционные обозначения элементов и перечень элементов.

Условные графические обозначения элементов и устройств выполняют совмещенным или разнесенным способом. При совмещенном способе составные части элементов 20

или устройств изображают на схеме так, как они расположены в изделии, т. е. в непосредственной близости друг к другу. При разнесенном способе условные графические обозначения составных частей элементов располагают в разных местах схемы с учетом порядка прохождения по ним тока (т. е. последовательно), так, чтобы отдельные цепи были изображены наиболее наглядно. Разнесенным способом можно вычерчивать как отдельные элементы или устройства (например, обмотки и контакты группы реле, контакты штепсельных разъемов и др.), так и всю схему.

Рисунок 4.6 – Пример оформления схемы Э3 на листе графического материала

Позиционные обозначения элементов. Всем изображенным на схеме элементам и устройствам присваиваются условные буквенно-цифровые позиционные обозначения в соответствии с ГОСТ 2.710–81.

Позиционные обозначения элементов (устройств) в пределах изделия. Порядковые номера элементам (устройствам) начиная с единицы присваивают в пределах группы элементов (устройств) с одинаковым буквенным позиционным обозначением одной группы или одного типа в соответствии с последовательностью их расположения на схеме сверху вниз в направлении слева направо, например, *R*1, *R*2,...,*C*1, *C*2 (см. рисунок 4.6). Буквы и цифры позиционного обозначения выполняют чертежным шрифтом одного размера.

Последовательность присвоения порядковых номеров может быть нарушена в зависимости от размещения элементов изделия, направления прохождения сигналов или функциональной последовательности процесса, а также при внесении в схему изменений.

Позиционные обозначения проставляют на схеме рядом с условными графическими обозначениями элементов и устройств с правой стороны или над ними.

На схеме изделия, в состав которого входят устройства, позиционные обозначения элементам присваивают в пределах каждого устройства, а при наличии нескольких одинаковых устройств — в пределах этих устройств по правилам, изложенным выше.

|       | 701(                                                            |              |

|-------|-----------------------------------------------------------------|--------------|

| Конт. | Цепь                                                            | Адрес        |

| 1     | $\Delta f = 10100 \Gamma$ ц                                     | =A1-X1:5     |

| 2     | $U_{\text{вых}} = 2 \text{ B}; R_{\text{H}} = 600 \text{ Om}$   | = A5 - X4:7  |

| 3     | $I_{\text{вых}} = 100 \text{ мA}; R_{\text{H}} = 10 \text{ Ом}$ | =A1-X1:6     |

| 4     | <i>f</i> гти = 1 МГц                                            | = A3 - X1:20 |

Примечание —  $\ll = A5 - X4$ : 7» означает, что выходной контакт изделия должен быть соединён с седьмым контактом четвёртого соединителя устройства A5.

Рисунок 4.7 – Пример оформления таблицы с характеристиками выходных цепей и адресата внешних соединений

Если в состав изделия входят функциональные группы, то вначале присваивают позиционные обозначения элементам, не входящим в функциональные группы, а затем элементам, входящим в функциональные группы. Для одинаковых функциональных групп позиционные обозначения элементов, присвоенные одной из них, повторяют во

всех последующих группах.

Обозначения устройства указывают сверху или справа от изображения. При разнесенном способе изображения позиционные обозначения проставляют около каждой составной части.

На принципиальной электрической схеме изображают клеммы, разъемы и другие элементы и указывают характеристики входных и выходных цепей изделия (величину напряжения, силу тока, частоту и т. д.), а также указывают адреса внешних соединений (рисунок 4.7).

Рекомендуется взамен условных графических обозначений соединительных элементов помещать таблицы с характеристиками входных и выходных цепей изделия и адресами их внешних подключений. Над таблицей допускается указывать графическое или буквенное обозначение гнезда или штыря.

# 4.4.1 Условные буквенно-цифровые обозначения в электрических схемах

1 Элементы (устройства, функциональные группы), входящие в изделие, на схеме должны иметь буквенные или буквенно-цифровые обозначения.

Буквенно-цифровые обозначения предназначены для записи в сокращенной форме сведений об элементах, устройствах и функциональных группах в документации на изделие или для нанесения непосредственно на изделие.

Типы условных буквенно-цифровых обозначений и правила их построения устанавливает ГОСТ 2.710–81.

2 Буквенные коды видов элементов приведены в таблице 4.2. Элементы разбиваются по видам на группы, имеющие обозначения из одной буквы. Для уточнения вида элементов применяют двухбуквенные и многобуквенные коды. При применении двухбуквенных и многобуквенных кодов первая буква должна соответствовать группе видов, к которой принадлежит элемент. Дополнительные обозначения должны быть пояснены на поле схемы.

Таблица 4.2 – Буквенные коды видов элементов

| 1-я буква кода<br>(обязательная) | Группа видов элементов      | Примеры видов элементов           | Двухбуквенный<br>код |

|----------------------------------|-----------------------------|-----------------------------------|----------------------|

| 1                                | 2                           | 3                                 | 4                    |

| A                                | Устройства (общее обозначе- | Усилители, приборы регулирования, |                      |

|                                  | ние)                        | телеуправления, лазеры, мазеры    |                      |

# Продолжение таблицы 4.2

| 1              | 2                             | 3                                  | 4   |

|----------------|-------------------------------|------------------------------------|-----|

| В              | Преобразователи неэлектриче-  | Громкоговоритель                   | BA  |

|                | ских величин в электрические  | Магнитострикционный элемент        | BB  |

|                | (кроме генераторов и источни- | Детектор ионизирующих излучений    | BD  |

|                | ков питания) или наоборот,    | Сельсин-приемник                   | BE  |

|                | аналоговые или многоразряд-   | Телефон (капсюль)                  | BF  |

|                | ные преобразователи или дат-  | Сельсин-датчик                     | BC  |

|                | чики для указания или измере- | Тепловой датчик                    | BK  |

|                | ния                           | Фотоэлемент                        | BL  |

|                |                               | Микрофон                           | BM  |

|                |                               | Датчик давления                    | BP  |

|                |                               | Пьезоэлемент                       | BQ  |

|                |                               | Датчик частоты вращения (тахогене- | 2.2 |

|                |                               | ратор)                             | BR  |

|                |                               | Звукосниматель                     | BS  |

|                |                               | Датчик скорости                    | BV  |

| C              | Конденсаторы                  |                                    |     |

| D              | Схемы интегральные, микро-    | Схема интегральная аналоговая      | DA  |

|                | сборки                        | Схема интегральная цифровая, логи- |     |

|                |                               | ческий элемент                     | DD  |

|                |                               | Устройства хранения информации     | DS  |

|                |                               | Устройства задержки                | DT  |

| E              | Элементы разные (осветитель-  | Нагревательный элемент             | EK  |

|                | ные устройства, нагреватель-  | Лампа осветительная                | EL  |

|                | ные элементы)                 | Пиропатрон                         | ET  |

| $\overline{F}$ | Разрядники, предохранители,   | Дискретный элемент защиты по току  | FA  |

|                | устройства защитные           | мгновенного действия               |     |

|                |                               | Дискретный элемент защиты по току  |     |

|                |                               | инерционного действия              | FP  |

|                |                               | Предохранитель плавкий             | FU  |

|                |                               | Дискретный элемент защиты по на-   | _   |

|                |                               | пряжению, разрядник                | FV  |

| G              | Генераторы, источники пита-   | Батарея                            | GB  |

|                | ния, кварцевые осцилляторы    |                                    |     |

| H              | Устройства индикационные и    | Прибор звуковой сигнализации       | HA  |

|                | сигнальные                    | Индикатор символьный               | HG  |

|                |                               | Прибор световой сигнализации       | HL  |

| K              | Реле, контакторы, пускатели   | Реле токовое                       | KA  |

|                |                               | Реле указательное                  | KH  |

|                |                               | Реле электротепловое               | KK  |

|                |                               | Контактор, магнитный пускатель     | KM  |

|                |                               | Реле времени                       | KT  |

|                |                               | Реле напряжения                    | KV  |

# Продолжение таблицы 4.2

| 1 | 2                                                                                                                                                                        | 3                                                                                                                                                                                                    | 4                                            |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| L | Катушки индуктивности, дроссели                                                                                                                                          | Дроссель люминесцентного освещения                                                                                                                                                                   | LL                                           |

| M | Двигатели постоянного и переменного тока                                                                                                                                 |                                                                                                                                                                                                      |                                              |

| P | менного тока Приборы, измерительное оборудование Примечание — Сочетание РЕ применять не допускается                                                                      | Амперметр Счетчик импульсов Частотомер Счетчик активной энергии Счетчик реактивной энергии Омметр Регистрирующий прибор Часы, измеритель времени действия Вольтметр Ваттметр                         | PA<br>PC<br>PF<br>PI<br>PK<br>PR<br>PS       |

| Q | Выключатели и разъединители в силовых цепях (энергоснабжение, питание оборудования и т. д.)                                                                              | Выключатель автоматический<br>Короткозамыкатель<br>Разъединитель                                                                                                                                     | QF<br>QK<br>QS                               |

| R | Резисторы                                                                                                                                                                | Терморезистор<br>Потенциометр<br>Шунт измерительный<br>Варистор                                                                                                                                      | RK<br>RP<br>RS<br>RU                         |

| S | Устройства коммутационные в цепях управления, сигнализации и измерительных цепях Примечание — Обозначение SF применяют для аппаратов, не имеющих контактов силовых цепей | Выключатель или переключатель Выключатель кнопочный Выключатель автоматический Выключатели, срабатывающие от следующих воздействий: уровня давления положения (путевой) частоты вращения температуры | SA<br>SB<br>SF<br>SL<br>SP<br>SQ<br>SR<br>SK |

| T | Трансформаторы, автотранс-<br>форматоры                                                                                                                                  | Трансформатор тока Электромагнитный стабилизатор Трансформатор напряжения                                                                                                                            | TA<br>TS<br>TV                               |

| U | Устройства связи<br>Преобразователи одного вида<br>электрических величин в дру-<br>гой вид                                                                               | Модулятор<br>Демодулятор<br>Дискриминатор<br>Преобразователь частотный, инвертор,<br>генератор частоты, выпрямитель                                                                                  | UB<br>UR<br>UI                               |

# Продолжение таблицы 4.2

| 1 | 2                             | 3                                    | 4    |

|---|-------------------------------|--------------------------------------|------|

| V | Приборы электровакуумные и    | Диод, стабилитрон                    | VD   |

|   | полупроводниковые             | Прибор электровакуумный              | VL   |

|   |                               | Транзистор                           | VT   |

|   |                               | Тиристор                             | VS   |

| W | Линии и элементы СВЧ          | Ответвитель                          | WE   |

|   |                               | Короткозамыкатель                    | WK   |

|   |                               | Вентиль                              | WS   |

|   | Антенны                       | Трансформатор, неоднородность, фа-   |      |

|   |                               | зовращатель                          | WT   |

|   |                               | Аттенюатор                           | WU   |

|   |                               | Антенна                              | WA   |

| X | Соединения контактные         | Токосъемник, контакт скользящий      | XA   |

| Λ | сосдинения контактные         | Штырь                                | XP   |

|   |                               | Гнездо                               | XS   |

|   |                               | Соединение разборное                 | XT   |

|   |                               | Соединитель высокочастотный          | XW   |

|   |                               | Coognimited by blocked the confident | 11,, |

| Y | Устройства механические с     | Электромагнит                        | YA   |

|   | электромагнитным приводом     | Тормоз с электромагнитным приводом   | YB   |

|   | •                             | Муфта с электромагнитным приводом    | YC   |

|   |                               | Электромагнитный патрон или плита    | ΥH   |

|   |                               |                                      |      |

| Z | Устройства оконечные, фильтры | Ограничитель                         | ZL   |

|   |                               | Фильтр кварцевый                     | ZQ   |

Буквенные коды применяются для обозначения элементов на структурных, функциональных и принципиальных схемах.

# 5 Разработка алгоритма работы микроконтроллера

### 5.1 Понятие алгоритма и его свойства

Проектирование устройств на базе микроконтроллеров предусматривает разработку алгоритма их работы как обязательного этапа, предшествующего аппаратнопрограммной реализации проектируемой системы.

В общем случае разработка алгоритма решает задачу создания точного набора инструкций, описывающих порядок действий исполнителя для достижения результата решения задачи за конечное время. Применительно к системам с микроконтроллерами разработка алгоритма состоит в создании набора инструкций и порядка их следования, при выполнении которого с помощью микроконтроллера достигаются цели функционирования проектируемой системы. При этом «порядок» следования инструкций в отличие от «последовательности» предполагает возможность параллельности в работе.

Алгоритм считается правильным, если он отвечает требованиям задачи. Алгоритм содержит ошибки, если для некоторых исходных данных он даёт неправильные результаты, сбои или не дает результатов вообще.

Основными характеристиками алгоритмов являются:

- дискретность алгоритма: деление алгоритма на отдельные шаги (действия);

- элементарность шагов: закон получения последующей системы величин из предыдущей должен быть простым и локальным. Какой шаг (действие) можно считать элементарным, определяется особенностями исполнителя алгоритма;

- массовость алгоритма: начальная система величин может выбираться из некоторого множества. Данное свойство означает, что один алгоритм, т.е. один и тот же порядок действий, может применяться для решения некоторого класса задач;

- детерминированность: совокупность промежуточных величин на любом шаге алгоритма однозначно определяется системой величин, имевшихся на предыдущем шаге. Данное свойство означает, что результат выполнения алгоритма определяется только входными данными и последовательностью действий алгоритма, а при применении алгоритма к одним и тем же исходным данным должен получаться всегда один и тот же результат;

- результативность: выполнение алгоритма должно обязательно приводить к его завершению. Однако существуют примеры формально бесконечных алгоритмов, применяемых на практике. Так, алгоритм работы системы сбора метеорологических данных состоит в непрерывном повторении последовательности действий («измерить температуру воздуха», «определить атмосферное давление»), выполняемых с определенной частотой (через минуту, час) во все время всего существования данной системы.

### 5.2 Представление алгоритма в виде блок-схем. Правила оформления

Наиболее удобным способом записи алгоритма является запись на языке блок-схем – набора символов (блоков различной формы), краткого пояснительного текста и соединяющих линий (линий потока данных или потока управления). Каждый элемент является шагом алгоритма. Основное достоинство такой формы представления — наглядность: блок-схема позволяет охватить весь алгоритм сразу, отследить различные варианты его выполнения. Однако в блок-схеме, как правило, отсутствует подробное описание конкретных действий — их существование лишь обозначено.

Правила выполнения блок-схем определяются следующими документами:

- ГОСТ 19.002-80. Схемы алгоритмов и программ. Правила выполнения;

- ГОСТ 19.003-80. Схемы алгоритмов и программ. Обозначения условные графические;

- ГОСТ 19.701-90. Схемы алгоритмов, программ, данных и систем. Условные обозначения и правила выполнения;

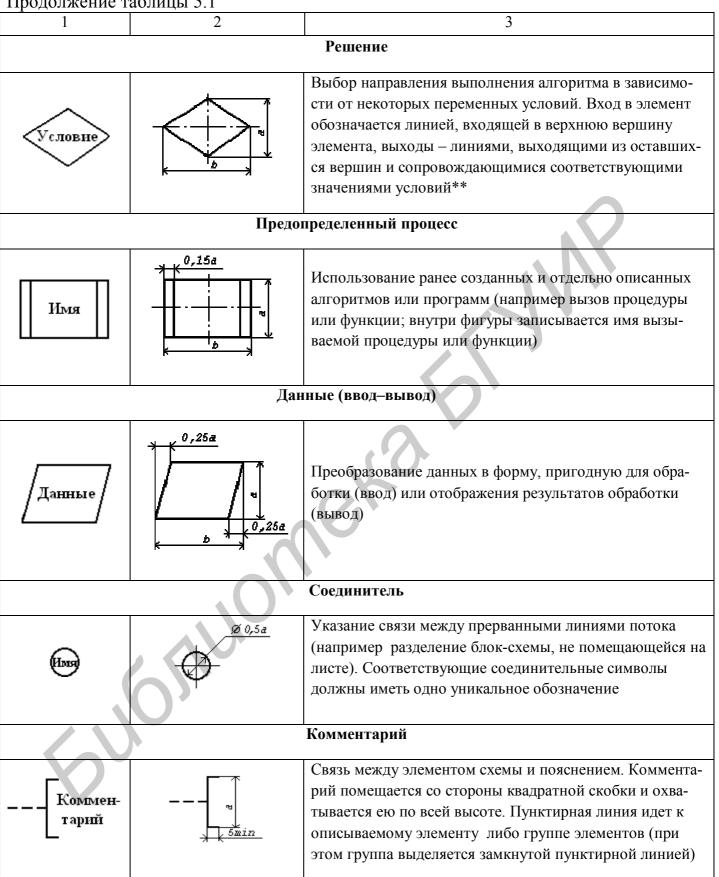

Обозначение, размеры обязательных символов и отображаемые ими функции в алгоритме и программе должны соответствовать указанным в таблице 5.1.

Таблица 5.1 – Основные символы блок-схемы алгоритма

| Обозначение символа на схеме | Размеры*<br>2                                                                                | Функция                                                                                                    |

|------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1                            |                                                                                              |                                                                                                            |

|                              | терминатор                                                                                   | (пуск-остановка)                                                                                           |

| Действие                     | Действие<br>В 25 а Начало, конец, прерывание процесса обрабо данных или выполнения программы |                                                                                                            |

|                              | П                                                                                            | роцесс                                                                                                     |

| Действие                     | Ps                                                                                           | Выполнение операций, в результате которых изменяется значение, форма представления или расположение данных |

<sup>\*</sup> Рекомендуется размер a выбирать из ряда 10, 15, 20 мм, а также увеличивать размер a на число, кратное 5. Размер b определяется как 1,5a (ГОСТ 19.003-80. Схемы алгоритмов и программ. Обозначения условные графические).

\*\* Если выходов больше трех, то их следует показывать одной линией, выходящей из вершины (чаще нижней) элемента, которая затем разветвляется в соответствующее число линий.

Правила применения символов:

- 1 Символ предназначен для графической идентификации функции, которую он отображает, независимо от текста внутри этого символа.

- 2 Символы в схеме должны быть расположены равномерно. Следует придерживаться разумной длины соединений и минимального числа длинных линий.

- 3 Большинство символов задумано так, чтобы дать возможность включения текста внутри символа. Формы символов, установленные настоящим стандартом, должны служить руководством для фактически используемых символов. Не должны изменяться углы и другие параметры, влияющие на соответствующую форму символов. Символы должны быть, по возможности, одного размера.

- 4 Символы могут быть вычерчены в любой ориентации, но предпочтительной является горизонтальная ориентация. Зеркальное изображение формы символа обозначает одну и ту же функцию, но не является предпочтительным.

- 5 Минимальное количество текста, необходимого для понимания функции данного символа, следует помещать внутри символа. Текст для чтения должен записываться слева направо и сверху вниз независимо от направления потока.

- 6 Если объем текста, помещаемого внутри символа, превышает его размеры, следует использовать символ комментария.

- 7 Если использование символов комментария может запутать или разрушить ход схемы, текст следует помещать на отдельном листе и давать перекрестную ссылку на символ.

Обозначение соединений между символами и отображаемые ими функции в алгоритме и программе должны соответствовать указанным в таблице 5.2.

Таблица 5.2 – Обозначение соединений между символами блок-схемы алгоритма

| Наименование                 | Обозначение<br>на схеме | Функция                                                                                                                                              |

|------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Линии потока                 | <del></del>  †          | Указание направления линии потока:  – допускается без стрелки, если линия направлена слева направо и сверху вниз;  – со стрелкой в остальных случаях |

| Излом линии<br>под углом 90° |                         | Изменение направление потока                                                                                                                         |

| Пересечение линий<br>потока  | + +                     | Пересечение двух несвязанных потоков                                                                                                                 |

Правила выполнения соединений:

- 1 Потоки данных или потоки управления в схемах показываются линиями. Направление потока слева направо и сверху вниз считается стандартным. В случае когда необходимо внести большую ясность в схему (например при соединениях), на линиях используются стрелки. Если поток имеет направление, отличное от стандартного, стрелки должны указывать это направление.

- 2 Расстояния между параллельными линиями потока должно быть не менее 3 мм, между символами схемы не менее 5 мм.

- 3 В схемах следует избегать пересечения линий. Пересекающиеся линии не имеют логической связи между собой, поэтому изменения направления в точках пересечения не допускаются.

- 4 Линии в схемах должны подходить к символу либо слева, либо сверху, а исходить либо справа, либо снизу. Линии должны быть направлены к центру символа.

- 5 При необходимости линии в схемах следует разрывать для избежания излишних пересечений или слишком длинных линий, а также если схема состоит из нескольких страниц. Соединитель в начале разрыва называется внешним соединителем, а соединитель в конце разрыва внутренним соединителем. В случае размещения алгоритма на нескольких страницах ссылки с указанием номера новой страницы могут быть приведены в символе комментария для их соединителей.

# 5.3 Поток управления действиями алгоритма и способы его организации

Поскольку алгоритм определяет порядок обработки информации, он должен содержать, с одной стороны, действия по обработке, а с другой стороны, порядок их следования, называемый потоком управления.

Рассмотренные выше блоки, связанные с обработкой данных, делятся на простые и условные. Особенность простого действия в том, что оно имеет один вход и один выход в отличие от условного, обладающего двумя выходами в зависимости от того, истинным ли окажется условие.

Часть алгоритма, организованная как простое действие, т.е. имеющая один вход (выполнение начинается всегда с одного и того же действия) и один выход (т.е. после завершения данного блока всегда начинает выполняться одно и то же действие), называется функциональным блоком. Из этого следует, что любое простое действие является функциональным блоком, а условное – нет.

Выделяют три различных варианта организации потока управления действиями алгоритма в зависимости от выполнения следующих свойств:

- 1 Все блоки алгоритма выполняются.

- 2 Каждый из выполняемых блоков выполняется только один раз.

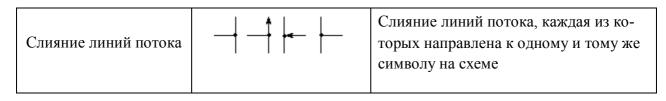

Поток управления, в котором выполняются оба эти свойства, называется линейным: в нем несколько функциональных блоков выполняются последовательно. Линейному потоку на языке блок-схем соответствует структура, приведенная на рисунке 5.1.

Рисунок 5.1 – Пример линейного потока управления алгоритма

Несколько блоков, связанных линейным потоком управления, могут быть объединены в один функциональный блок (рисунок 5.2).

Рисунок. 5.2 – Пример объединения нескольких блоков, связанных линейным потоком управления, в один функциональный блок

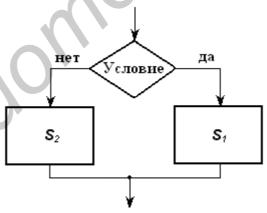

Второй тип потока управления называется ветвлением: он организует выполнение одного из двух функциональных блоков в зависимости от значения проверяемого логического условия (рисунок 5.3). В этом типе выполняется свойство 2, но не выполняется свойство 1. Если структура содержит два функциональных блока (S1 и S2), ветвление называется полным; возможно существование неполного ветвления — при этом один из блоков пуст (обычно S2).

Рисунок 5.3 – Пример потока управления алгоритма по типу ветвления

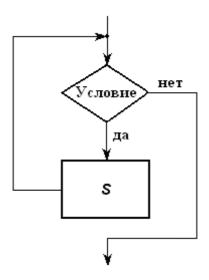

Третий тип потока управления называется циклическим: он организует многократное повторение функционального блока до тех пор, пока логическое условие его выполнения является истинным (рисунок 5.4). Для циклического потока выполняется свойство 1, но не выполняется свойство 2.

Рисунок 5.4 – Пример циклического потока управления алгоритма

Процессы циклической структуры делятся на три подтипа:

- 1 Счетный цикл циклический процесс, при котором количество повторений определено.

- 2 Итерационный цикл циклический процесс, который завершается при достижении либо нарушении определенных условий.

- 3 Поисковый цикл циклический процесс, который завершается по окончании другого процесса либо предусмотрено досрочное завершается при достижении определенных условий.

### 5.4 Концептуальный и функциональный алгоритмы

Схемы алгоритмов могут использоваться на различных уровнях детализации, причем число уровней зависит от размеров и сложности задачи обработки данных. Уровень детализации должен быть таким, чтобы различные части и взаимосвязь между ними были понятны в целом.

Обобщенный алгоритм работы проектируемого на базе микроконтроллеров устройства называется концептуальным. Такой алгоритм характеризуется низким уровнем детализации и укрупнено отражает принципиальные этапы работы устройства, соответствующие основным подзадачам разрабатываемой системы. Концептуальный алгоритм работы проектируемого устройства отличается понятностью и простотой восприятия, поскольку невелико число исходных структур, которыми он образован.

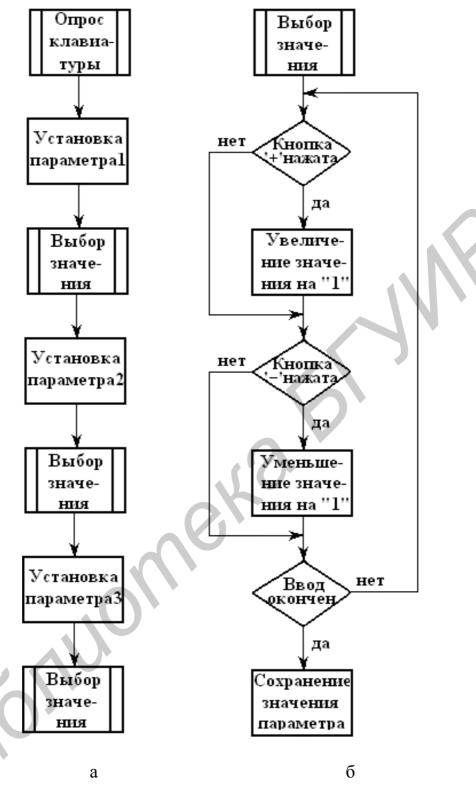

Так, например, концептуальный алгоритм работы микроконтроллера любого терапевтического аппарата можно представить в виде следующих функциональных блоков: инициализация, опрос клавиатуры, выбор режима работы, рабочая часть — заключенных между стандартными блоками «Начало» и «Конец» (рисунок 5.5). Блок «Инициализация» предусматривает выполнение микроконтроллером базового набора подготовительных операций после включения устройства. Блок «Опрос клавиатуры» решает задачу ввода пользователем требуемых параметров терапевтической процедуры (например, длительность процедуры, амплитуда и частота воздействия, непрерывный или прерывистый характер воздействия и т. д.). Блок «Выбор режима работы» выполняет выбор подпрограммы, обеспечивающей требуемый режим работы, а следующий далее блок «Рабочая часть» реализует работу подпрограммы требуемого режима в течение заданного промежутка времени.

Детальный алгоритм работы проектируемого на базе микроконтроллеров устройства называется функциональным. Такой алгоритм предусматривает организацию каждого программного модуля в виде стандартного функционального блока (одного из трех базовых структур), выполняющего только одну функцию. Модули обладают определенной автономностью, что позволяет вести поиск и устранение ошибок независимо от остальной части алгоритма (на последующих этапах программы), а также обеспечивает относительно простую модифицируемость как отдельного модуля, так и алгоритма (программы) в целом. Разработка функционального алгоритма особенно важна при создании сложных программ: модульный принцип позволяет разбить общую задачу на составные и относительно автономные части, каждая из которых может создаваться и отлаживаться независимо.

Рисунок 5.5 — Пример концептуального алгоритма работы микроконтроллера в терапевтическом устройстве

Примером фрагмента функционального алгоритма может служить подпрограмма опроса клавиатуры (рисунок 5.6, а), представляющая собой установку требуемого числа параметров с помощью многократного вызова вложенной подпрограммы выбора значения конкретного параметра (рисунок 5.6, б).

а – подпрограмма опроса клавиатуры;

б – вложенная подпрограмма выбора значения конкретного параметра

Рисунок 5.6 — Фрагмент функционального алгоритма работы микроконтроллера

#### 6 Разработка программы для микроконтроллеров Cygnal

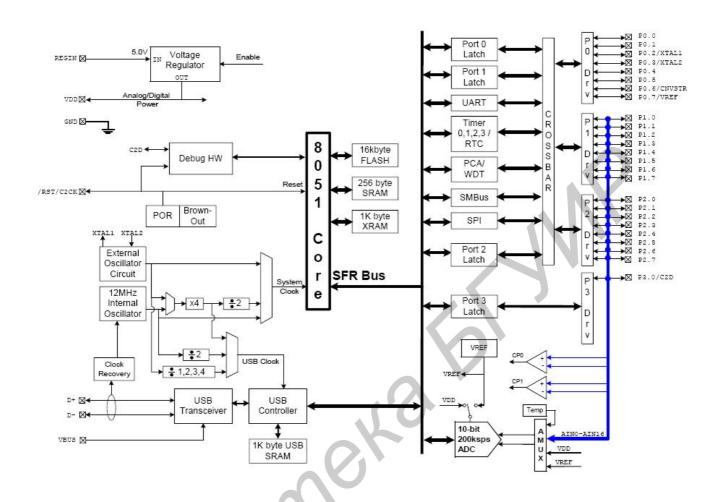

#### 6.1 Краткий обзор микроконтроллера Cygnal семейства C8051F320

МК С8051F320 имеет встроенную схему сброса по включению питания, схему слежения за напряжением питания, регулятор напряжения, сторожевой таймер, тактовый генератор и представляет собой, таким образом, функционально законченную систему на кристалле. Имеется возможность внутрисхемного программирования Flash-памяти, что обеспечивает долговременное (энергонезависимое) хранение данных, а также позволяет осуществлять обновление программного обеспечения в готовых изделиях. Программа пользователя может полностью управлять всеми периферийными модулями, а также может индивидуально отключить любой из них с целью уменьшения энергопотребления.

Встроенный двухпроводный Silicon Labs Development Interface (интерфейс C2) позволяет производить «неразрушающую» (не используются внутренние ресурсы) внутрисхемную отладку в режиме реального времени, используя МК, установленный в конечное изделие. Средства отладки обеспечивают проверку и модификацию памяти и регистров, расстановку точек остановок, пошаговое выполнение программы, а также поддерживают команды запуска и остановки. В процессе отладки с использованием интерфейса C2 все аналоговые и цифровые периферийные модули полностью сохраняют свою работоспособность. Два вывода интерфейса C2 могут использоваться для других пользовательских функций, что позволяет осуществлять внутрисистемную отладку, не занимая для этого отдельные выводы корпуса. Структурная схема МК C8051F320 изображена на рисунке 6.1.

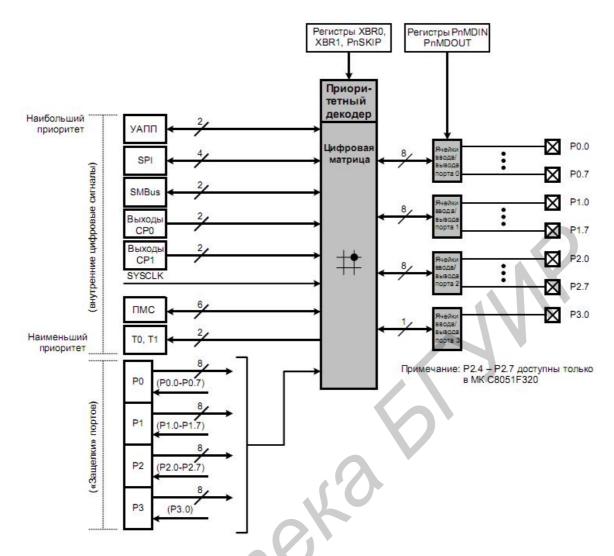

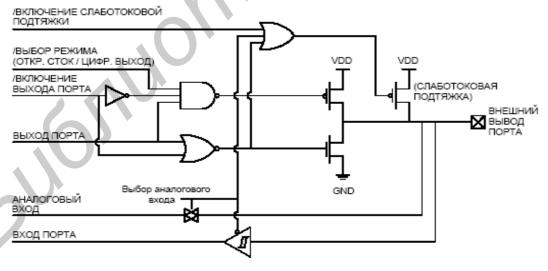

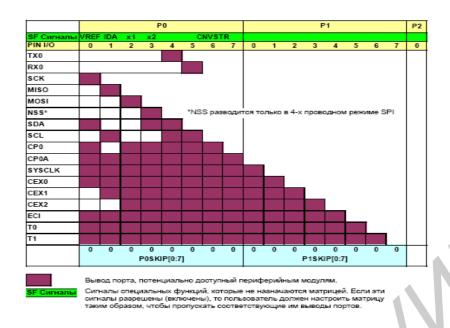

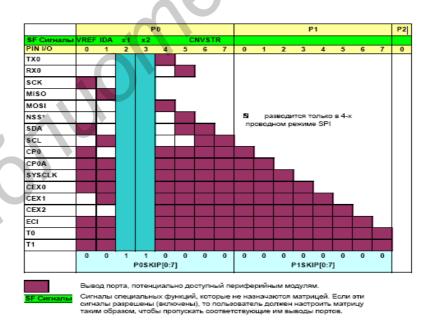

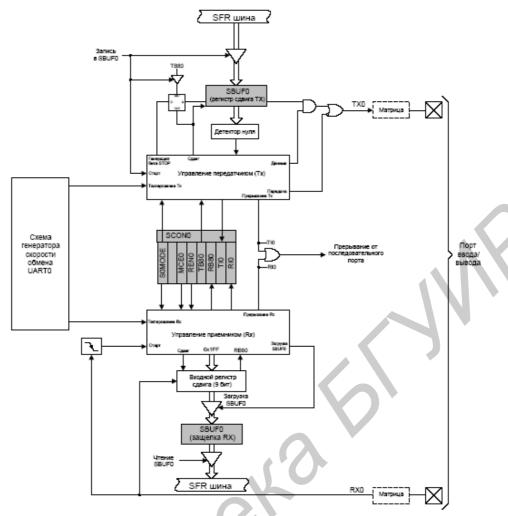

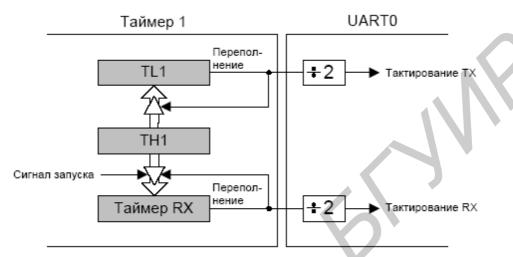

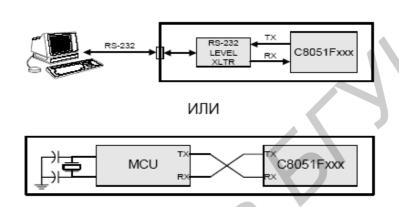

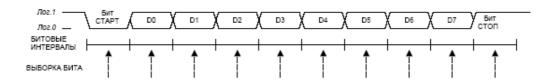

Каждый МК предназначен для работы в промышленном температурном диапазоне (–40°С...+85°С) при напряжении питания 2,7 В...3,6 В. (Примечание – для взаимодействия по шине USB требуется напряжение 3,0 В...3,6 В). На порты ввода/вывода и вывод /RST могут быть поданы входные сигналы напряжением до 5В. МК С8051F320/1 выпускаются в 32-выводных корпусах типа LQFP и 28-выводных корпусах типа MLP.