# Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

Кафедра систем телекоммуникаций

## П. А. Капуро

# ЦИФРОВЫЕ ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА В ТЕЛЕКОММУНИКАЦИЯХ

В 2-х частях

Часть 1

# БАЗОВЫЕ ЦИФРОВЫЕ ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА

Рекомендовано УМО по образованию в области информатики и радиоэлектроники в качестве учебно-методического пособия для специальностей 1-45 01 01 «Многоканальные системы телекоммуникаций», 1-45 01 02 «Системы радиосвязи, радиовещания и телевидения» и направлений специальности 1-45 01 01-01 «Инфокоммуникационные технологии (системы телекоммуникаций)», 1-45 01 01-03 «Инфокоммуникационные технологии (системы телекоммуникаций специального назначения)», 1-45 01 01-04 «Инфокоммуникационные технологии (цифровое теле- и радиовещание)»

УДК 004.312:621.391(076) ББК 32.973я73+32.811я73 К20

#### Репензенты:

кафедра связи учреждения образования «Военная академия Республики Беларусь» (протокол №89 от 31.03.2014);

заведующий кафедрой телекоммуникационных систем учреждения образования «Высший государственный колледж связи», кандидат технических наук, доцент К. И. Пирогов

### Капуро, П. А.

K20

Цифровые функциональные устройства в телекоммуникациях. В 2 ч. Ч. 1 : Базовые цифровые функциональные устройства : учеб.-метод. пособие / П. А. Капуро. – Минск : БГУИР, 2014. – 64 с. : ил.

ISBN 978-985-543-022-4.

Изложены основы теории алгебры логики, логических функций и цифровых автоматов, позволяющие простейшими методами решать задачи аналитического описания работы цифровых устройств и их проектирования.

Рассматриваются варианты схемной реализации типовых цифровых функциональных устройств. Приведены методики проектирования схем комбинационного и последовательностного типов.

УДК 004.312:621.391(076) ББК 32.973я73+32.811я73

ISBN 978-985-543-022-4 (ч. 1) ISBN 978-985-543-021-7

- © Капуро П. А., 2014

- © УО «Белорусский государственный университет информатики и радиоэлектроники», 2014

#### 1 ОСНОВЫ АЛГЕБРЫ ЛОГИКИ

## 1.1 Аксиомы, законы и правила алгебры логики

Основы алгебры логики были заложены в середине XIX века трудами английского математика Дж. Буля, по имени которого она называется также булевой алгеброй. Понимание принципов, лежащих в ее основе, важно для овладения методами описания и проектирования цифровых устройств. Начало использованию алгебры логики для синтеза переключательных (релейных) схем было положено в 1938 г. работами американского ученого К. Шеннона.

В алгебре логики рассматриваются переменные, которые могут принимать только два значения — 0 и 1. В дальнейшем переменные будем обозначать латинскими буквами (при необходимости с цифровыми индексами): x, y, B, A2.

Отношение эквивалентности удовлетворяет следующим свойствам:

$X = X - pe\phi$ лексивность;

если X = Y, то Y = X - симметричность;

если X = Y и Y = Z, то X = Z - mpaнзитивность.

Из отношения эквивалентности следует принцип подстановки: если X = Y, то в любой формуле, содержащей X, вместо X можно подставить Y, и в результате будет получена эквивалентная формула.

Алгебра логики определяется следующей системой аксиом:

$$X = 0$$

, если  $X \neq 1$

$X = 1$ , если  $X \neq 0$  (1.1)

$$\begin{array}{c|c}

0 \lor 0 = 0 \\

0 \lor 1 = 1 \\

1 \lor 0 = 1 \\

1 \lor 1 = 1

\end{array}$$

$$\begin{array}{c}

0 \cdot 0 = 0 \\

0 \cdot 1 = 0 \\

1 \cdot 0 = 0 \\

1 \cdot 1 = 1

\end{array}$$

$$\begin{array}{c}

\overline{0} = 1 \\

\overline{1} = 0

\end{array}$$

$$\overline{1} = 0$$

$$\overline{1} = 0$$

Аксиома (1.1) является утверждением того, что в алгебре логики рассматриваются только двоичные переменные, аксиомы (1.2), (1.3) определяют свойства операций дизъюнкции и конъюнкции, а аксиома (1.4) – операции отрицания.

С помощью аксиом алгебры логики можно доказать целый ряд тождеств и теорем. Одним из эффективных методов доказательства теорем является *методо перебора* всех значений переменных: если теорема истинна, то с учетом (1.2)...(1.4) уравнение, формулирующее утверждение теоремы, должно быть истинно при подстановке любых значений переменных в обе его части. Метод перебора не слишком трудоемок, т. к. переменные могут иметь только два значения: 0 и 1.

Если в логическое выражение входят операции дизъюнкции и конъюнкции, то следует соблюдать следующий порядок выполнения операций: сначала выполняется операция конъюнкции (она имеет приоритет), затем операция дизъюнкции. В сложных логических выражениях для задания иного порядка выполнения операций используются скобки.

Операции логического сложения (дизъюнкции) и логического умножения (конъюнкции) для случая одной переменной x обладают следующими свойствами:

Для случая двух и более переменных справедливы следующие законы:

- переместительные (коммутативные):

$$\begin{cases}

x \cdot y = y \cdot x \\

x \vee y = y \vee x

\end{cases};$$

(1.7)

- сочетательные (ассоциативные):

$$x \cdot (y \cdot z) = (x \cdot y) \cdot z = (x \cdot z) \cdot y$$

$$x \vee (y \vee z) = (x \vee y) \vee z = (x \vee z) \vee y$$

$$; \tag{1.8}$$

- распределительные (дистрибутивные):

$$x \cdot (y \lor z) = x \cdot y \lor x \cdot z x \lor y \cdot z = (x \lor y)(x \lor z) ;$$

(1.9)

- двойственности (теоремы де Моргана):

$$\frac{\overline{x \cdot y} = \overline{x} \vee \overline{y}}{\overline{x \vee y} = \overline{x} \cdot \overline{y}};$$

(1.10)

- двойного отрицания:

$$\overline{(\overline{x})} = \overline{x} = x; \tag{1.11}$$

- поглощения:

$$x \lor x \cdot y = x x \cdot (x \lor y) = x$$

; (1.12)

- операции склеивания:

$$x \cdot y \vee x \cdot \overline{y} = x (x \vee y) \cdot (x \vee \overline{y}) = x$$

(1.13)

- операции обобщенного склеивания:

$$\left\{

\begin{array}{l}

x \cdot y \vee \overline{x} \cdot z \vee y \cdot z = x \cdot y \vee \overline{x} \cdot z \\

(x \vee y) \cdot (\overline{x} \vee z) \cdot (y \vee z) = (x \vee y) \cdot (\overline{x} \vee z)

\end{array}

\right\};$$

(1.14)

$$\begin{cases}

x \lor \overline{x} \cdot y = x \lor y \\

x \cdot (\overline{x} \lor y) = x \cdot y

\end{cases}$$

(1.15)

Некоторые законы и тождества алгебры логики имеют особое значение, т. к. позволяют упрощать логические выражения. Например, в выражениях (1.5), (1.6), (1.11)...(1.15) правая часть выражения проще левой, поэтому, проведя в логических выражениях соответствующие преобразования, можно добиться существенного их упрощения. Наиболее часто для преобразования логических выражений с целью их упрощения используются тождества (1.12)...(1.15).

Операция сложения по модулю 2 (исключающее ИЛИ, логическая неравнозначность) обозначается символом  $\oplus$  и определяется соотношением

$$x \oplus y = \overline{x} \cdot y \vee x \cdot \overline{y} = (\overline{x} \vee \overline{y}) \cdot (x \vee y). \tag{1.16}$$

Используя аксиомы алгебры логики, легко убедиться, что

$$0 \oplus 0 = 1 \oplus 1 = 0; \ 1 \oplus 0 = 0 \oplus 1 = 1.$$

(1.17)

Из этих соотношений следует, что значение  $x \oplus y$ :

- совпадает со значением младшего разряда суммы двух одноразрядных двоичных чисел x и y;

- совпадает с результатом дизъюнкции переменных x и y, за исключением случая, когда две переменные равны 1;

- равно 1, когда значения переменных не равны друг другу.

Перечисленные свойства операции  $x \oplus y$  и определяют ее названия. Операция суммирования по модулю 2 коммутативна, ассоциативна и дистрибутивна относительно операции конъюнкции:

$$x \oplus y = y \oplus x$$

$$x \oplus (y \oplus z) = (x \oplus y) \oplus z = (x \oplus z) \oplus y$$

$$x \cdot (y \oplus z) = x \cdot y \oplus x \cdot z$$

$$(1.18)$$

Для операции сложения по модулю 2 также справедливы следующие тождества:

$$x \oplus 0 = x$$

$$x \oplus 1 = \overline{x}$$

$$x \oplus x = 0$$

$$x \oplus \overline{x} = 1$$

$$\overline{x \oplus y} = \overline{x} \cdot \overline{y} \lor x \cdot y = (\overline{x} \lor y) \cdot (x \lor \overline{y}) = \overline{x} \oplus y = x \oplus \overline{y}$$

$$(1.19)$$

## 1.2 Логические функции

#### 1.2.1 Общие понятия

Любое логическое выражение, составленное из n переменных  $x_n$ , ...,  $x_1$  с помощью конечного числа операций алгебры логики, можно рассматривать как некоторую функцию n переменных. В соответствии с аксиомами (1.1)...(1.4) функция может принимать в зависимости от значений переменных только два значения: 0 и 1. Такие функции являются весьма удобным инструментом для описания, анализа и синтеза логических схем, выходные сигналы которых характеризуются лишь двумя уровнями напряжения: высоким (1) и низким (0). В связи с этим логические функции называются переключательными.

Для функций n переменных  $x_n$ , ...,  $x_1$  используется общее обозначение  $F(v) = F(x_n, ..., x_1)$ , где  $v = (x_n, ..., x_1)$ , т. е. совокупность переменных  $x_n$ , ...,  $x_1$  можно рассматривать как n-мерный вектор. Так как каждая переменная  $x_p$  (p = 1, 2, ..., n) может принимать только два значения (0 и 1), то число всех возможных комбинаций значений  $x_n$ , ...,  $x_1$  конечно. В общем виде конкретное значение переменной  $x_p$  (0 или 1) будем обозначать через  $e_p$ .

Областью определения функции n переменных  $x_n$ , ...,  $x_1$  является совокупность точек n-мерного пространства, причем каждая из точек задается определенной комбинацией значений этих переменных:

$$x_n = e_n, ..., x_p = e_p, ..., x_1 = e_1,$$

где  $e_p = 0$  или 1 (p = 1, 2, ..., n).

Обозначим точки, задающие область определения функции F(v), через

$$v_i = (e_n, ..., e_p, ...e_1).$$

Если представить эту комбинацию значений переменных  $(e_n, ..., e_p, ...e_1)$  как число, записанное в двоичном коде, то оказывается возможным пронумеровать все точки области определения логической функции с помощью n-разрядных двоичных чисел  $(e_n ...e_p ...e_1)_2$  или с помощью эквивалентных им десятичных чисел i. Так как имеется  $2^n$  различных n-разрядных двоичных чисел, то область определения функции n переменных будет содержать  $2^n$  точек:

$$v \in \{v_0, v_1, ..., v_{2^n-1}\}.$$

Для задания функции F(v) следует указать ее значения во всех точках области определения, т. е. следует задать значения  $F(v_i) = 0$  или 1, где  $i = 0, 1, ..., 2^n - 1$ . Каждой конкретной функции n переменных можно поставить в соответствие  $2^n$ -разрядное число, составленное из значений  $F(v_i) = 0$  или 1, которые она принимает в  $2^n$  точках области определения. Так как имеется всего  $2^{2^n}$  различных  $2^n$ -разрядных двоичных чисел, то и число различных функций n переменных равно  $2^{2^n}$ .

Функции n переменных могут зависеть не от всех переменных  $x_n$ , ...,  $x_1$ . Такие функции называются вырожденными. В частности, функция  $F_0(v)$ , равная нулю, и функция  $F_1(v)$ , равная единице во всех точках  $v_i$  ( $i=0,1,...,2^n-1$ ) области определения, не зависят ни от одной переменной. Эти функции называются константой ноль и константой единица соответственно.

Функция n переменных F(v) называется  $nonhocmью onpedenehhoй, если ее значения <math>F(v_i) = a_i = 0$  или 1 заданы во всех  $2^n$  точках  $v_i$  области определения. Если же значение функции не задано хотя бы в одной точке  $v_i$ , то она называется nonhocmью onpedenehhoй. Не определенное в точке  $v_i$  значение функции описывается символом  $c_i = *$  или  $\Phi$  ( $\Phi$  – совмещенные символы 0 и 1, что указывает на неопределенность значения функции), т. е., если в точке  $v_i$  значение функции не задано, то  $F(v_i) = c_i$ .

Не полностью определенные функции можно доопределять произвольным способом, полагая  $c_i = 0$  или 1. Если значения функции не заданы в m точках, то функцию можно доопределить  $2^m$  способами, т. к. имеется  $2^m$  различных m-разрядных двоичных чисел, соответствующих различным способам доопределения функции в m точках. Таким образом, не определенной в m точках функции соответствует группа из  $2^m$  полностью определенных функций.

Так как область определения любой функции n переменных конечна ( $2^n$  точек), она может быть задана таблицей значений  $F(v_i) = a_i = 0$  или 1 (или  $c_i$ ), которые она принимает в точках  $v_i$ , где  $i = 0, 1, ..., 2^n - 1$ . Такие таблицы называются mаблицами истинности.

Второй способ задания логической функции – аналитический, при котором функция задается в виде логического выражения, получаемого путем логических преобразований с помощью законов и правил булевой алгебры.

## **1.2.2** Функции двух переменных $F(x_2, x_1)$

Область определения таких функций состоит из четырех точек ( $2^n = 2^2 = 4$ ):  $v_0 = (0, 0)$ ,  $v_1 = (0, 1)$ ,  $v_2 = (1, 0)$ ,  $v_3 = (1, 1)$ . Общее количество функций двух переменных равно  $16 (2^{2^n} = 2^{2^2} = 2^4 = 16)$ . Значения всех возможных функций  $F(x_2, x_1)$  представлены в таблице 1.1, которая является совмещенной таблицей истинности функций  $F_0...F_{15}$  двух переменных. В левой части таблицы перечислены все возможные сочетания значений переменных  $x_1$  и  $x_2$ , в правой части приведены значения функций  $F_0...F_{15}$  при этих сочетаниях переменных.

| i | $x_2$ | $x_1$ | $F_0$ | $F_1$ | $F_2$ | $F_3$ | $F_4$ | $F_5$ | $F_6$ | $F_7$ | $F_8$ | $F_9$ | $F_{10}$ | $F_{11}$ | $F_{12}$ | $F_{13}$ | $F_{14}$ | $F_{15}$ |

|---|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------|----------|----------|----------|----------|----------|

| 0 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1        | 1        | 1        | 1        | 1        | 1        |

| 1 | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0     | 0     | 0        | 0        | 1        | 1        | 1        | 1        |

| 2 | 1     | 0     | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1     | 0     | 0     | 1        | 1        | 0        | 0        | 1        | 1        |

| 3 | 1     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0        | 1        | 0        | 1        | 0        | 1        |

Таблица 1.1 – Таблицы истинности функций двух переменных

Каждая функция  $F_0...F_{15}$  обозначает одну из 16 возможных логических операций над двумя переменными  $x_1$  и  $x_2$ , имеет собственное название и аналитическое описание:

$$F_0 = 0 \ (F_{15} = 1)$$

– константа ноль (единица);

$$F_1 = x_1 \cdot x_2$$

– конъюнкция, логическое умножение, И;

$$F_2 = \overline{x_1} \cdot x_2 \ (F_4 = x_1 \cdot \overline{x_2}) - \text{запрет } x_1 (x_2);$$

$$F_3 = x_2 (F_5 = x_1)$$

– повторение  $x_2 (x_1)$ ;

$F_6 = \overline{x_1} \cdot x_2 \vee x_1 \cdot \overline{x_2} = x_1 \oplus x_2$  — неэквивалентность, сложение по модулю 2, исключающее ИЛИ;

$$F_7 = x_1 \lor x_2$$

– дизъюнкция, логическое сложение, ИЛИ;

$$F_8 = \overline{x_1 \lor x_2}$$

– функция Пирса, ИЛИ-НЕ;

$$F_9 = \overline{x_1} \cdot \overline{x_2} \vee x_1 \cdot x_2 = \overline{x_1 \oplus x_2}$$

– эквивалентность, исключающее ИЛИ-НЕ;

$$F_{10} = \overline{x_1}$$

( $F_{12} = \overline{x_2}$ ) – отрицание  $x_1(x_2)$ , инверсия  $x_1(x_2)$ , НЕ;

$$F_{11} = \overline{x_1} \vee x_2 \ (F_{13} = \overline{x_2} \vee x_1)$$

– импликация  $x_1(x_2)$ ;

$$F_{14} = \overline{x_1 \cdot x_2}$$

– функция Шеффера, И-НЕ.

Функции двух переменных исключительно важны в силу того, что любая функция n переменных может быть получена из них методом суперпозиции — подстановкой этих функций вместо переменных в другие функции. Такая подстановка возможна на основании того, что области значений функций и переменных совпадают (0 и 1). Наибольшее применение получили следующие невырожденные функции двух переменных  $x_2$  и  $x_1$ :  $F_1$  (конъюнкция, И),  $F_6$  (сумма по модулю два, исключающее ИЛИ),  $F_7$  (дизъюнкция, ИЛИ),  $F_8$  (ИЛИ-НЕ) и  $F_{14}$  (И-НЕ).

#### 1.2.3 Принцип и закон двойственности

Алгебра логики обладает замечательным свойством, которое называется принципом двойственности: если имеет место тождество  $F(v, 0, 1/\&, \lor) = G(v, 0, 1/\&, \lor)$ , где  $v = (x_n, ..., x_1)$ , то справедливо также тождество  $F(v, 1, 0/\lor, \&) = G(v, 1, 0/\lor, \&)$ , т. е., если в каком-либо тождестве произвести взаимную замену символов 0 и 1 (при их наличии) и операций дизьюнкции и конъюнкции, то в результате также будет получено тождество. Два тождества, связанные между собой таким образом, называются *двойственными*. Истинность самого принципа двойственности не доказывается, т. к. данный принцип является внутренним свойством алгебры логики (заключен в ее аксиомах).

Законы двойственности (теоремы де Моргана (1.10)) определяют способ отыскания инверсных функций, представляющих собой дизъюнкцию и конъюнкцию двух переменных. К. Шеннон предложил обобщение этих теорем, позволяющее отыскивать инверсию любой функции F(v). Закон двойственности имеет вид

$$\overline{F(v/\&,\vee)} = F(\overline{v}/\vee,\&), \tag{1.20}$$

где  $v = (x_n, ..., x_1)$ ,  $\overline{v} = (\overline{x}_n, ..., \overline{x}_1)$ , т. е. инверсию любой функции F(v) можно получить взаимной заменой переменных  $x_p$  и их инверсий  $\overline{x}_p$  (p = 1, 2, ..., n) и операций дизъюнкции и конъюнкции.

#### 1.2.4 Теоремы разложения

В теории логических функций важное значение имеет теорема разложения: любую функцию F(v) можно разложить по переменной  $x_p$  в форме

$$F(x_n, ..., x_n, ...x_1) = x_n \cdot F(x_n, ..., 1, ...x_1) \vee \overline{x}_n \cdot F(x_n, ..., 0, ...x_1). \tag{1.21}$$

Теорема легко доказывается методом перебора.

Используя принцип двойственности, можно также записать

$$F(x_n, ..., x_p, ...x_1) = (x_p \lor F(x_n, ..., 0, ...x_1)) \cdot (\overline{x}_p \lor F(x_n, ..., 1, ...x_1)).$$

(1.22)

С теоремами разложения связаны тождества:

$$\begin{vmatrix}

x_p \cdot F(x_n, ..., x_p, ... x_1) = x_p \cdot F(x_n, ..., 1, ... x_1) \\

\overline{x}_p \cdot F(x_n, ..., x_p, ... x_1) = \overline{x}_p \cdot F(x_n, ..., 0, ... x_1)

\end{vmatrix}, (1.23)$$

$$x_{p} \vee F(x_{n},...,x_{p},...x_{1}) = x_{p} \vee F(x_{n},...,0,...x_{1})$$

$$\overline{x}_{p} \vee F(x_{n},...,x_{p},...x_{1}) = \overline{x}_{p} \vee F(x_{n},...,1,...x_{1})$$

$$(1.24)$$

Теоремы разложения и связанные с ними тождества являются удобным инструментом для преобразования и упрощения логических выражений. В частности, разложив логическую функцию, выполняемую каким-либо цифровым устройством, по переменной, описывающей состояние какого-либо сигнала управления, можно определить реакции этого устройства на наличие и отсутствие этого сигнала.

# 1.2.5 Первичные термы, минтермы и макстермы

Переменные  $x_p$  и их инверсии  $\overline{x_p}$  в теории алгебры логики называются первичными термами, для которых используется символическое обозначение:

$$x_p^{e_p} = \overline{e_p} \cdot \overline{x_p} \vee e_p x_p = \overline{e_p \oplus x_p}, \qquad (1.25)$$

где  $e_p=0$  или 1. Данное символическое обозначение объединяет в одном символе  $x_p^{e_p}$  оба первичных терма  $x_p$  и  $\overline{x_p}$ . Действительно, при подстановке в (1.25) значений  $e_p=0$  и 1 получаем

$$x_p^{e_p} = \begin{cases} \overline{x_p}, ecnu \ e_p = 0, \\ x_p, ecnu \ e_p = 1. \end{cases}$$

Mинимальным термом (минтермом, конституентой единицы) называется функция n переменных (конъюнкция первичных термов):

$$K_i(\mathbf{v}) = x_n^{e_n} \cdot x_{n-1}^{e_{n-1}} \cdot \dots \cdot x_1^{e_1} = \prod_{p=1}^n x_p^{e_p},$$

(1.26)

где  $v = (x_n, ..., x_1)$ ,  $e_p = 0$  или 1,  $i = (e_n ... e_1)_2$ . Из данного определения следует, что существует  $2^n$  различных минтермов n переменных, т. к. имеется  $2^n$  различных n-разрядных двоичных чисел  $i = 0, 1, ..., 2^n - 1$ .

Минтермы обладают следующими свойствами:

$$K_i(v) = \begin{cases} 1, ecnu \ v = v_i, \\ 0, ecnu \ v = v_j \neq v_i; \end{cases}$$

(1.27)

$$K_i(v) \cdot K_j(v) \equiv 0$$

, если  $i \neq j$ ; (1.28)

$$\sum_{i=0}^{2^n - 1} K_i(v) \equiv 1. \tag{1.29}$$

Свойство (1.27) соответствует тому, что любой минтерм  $K_i(v)$  равен 1 только в одной точке  $v_i$  области определения.

Все минтермы двух переменных  $x_1$  и  $x_2$ :

$$K_{0}(v) = x_{2}^{0} \cdot x_{1}^{0} = \overline{x}_{2} \cdot \overline{x}_{1};$$

$$K_{1}(v) = x_{2}^{0} \cdot x_{1}^{1} = \overline{x}_{2} \cdot x_{1};$$

$$K_{2}(v) = x_{2}^{1} \cdot x_{1}^{0} = x_{2} \cdot \overline{x}_{1};$$

$$K_{3}(v) = x_{2}^{1} \cdot x_{1}^{1} = x_{2} \cdot x_{1}.$$

Аналогично можно записать минтерм большего числа переменных. Например, пусть  $n=4,\,i=5=(0101)_2,\,$  тогда

$$K_5(v) = x_4^0 \cdot x_3^1 \cdot x_2^0 \cdot x_1^1 = \overline{x}_4 \cdot x_3 \cdot \overline{x}_2 \cdot x_1.$$

Mаксимальным термом (макстермом, конституентой ноля) называется функция n переменных (дизъюнкция инверсий первичных термов):

$$M_{i}(v) = \overline{K_{i}(v)} = \prod_{p=1}^{n} x_{p}^{e_{p}} = \sum_{p=1}^{n} \overline{x_{p}^{e_{p}}} = \overline{x_{n}^{e_{n}}} \vee \overline{x_{n-1}^{e_{n-1}}} \vee \dots \vee \overline{x_{1}^{e_{1}}},$$

(1.30)

где  $v = (x_n, ..., x_1), e_p = 0$  или  $1, i = (e_n ... e_1)_2$ .

Макстермы обладают следующими свойствами:

$$M_{i}(v) = \begin{cases} 0, ecnu \ v = v_{i}, \\ 1, ecnu \ v = v_{j} \neq v_{i}; \end{cases}$$

$$(1.31)$$

$$M_i(v) \lor M_j(v) \equiv 1, ecnu \ i \neq j; \tag{1.32}$$

$$\prod_{i=0}^{2^n - 1} M_i(v) \equiv 0. \tag{1.33}$$

Свойства макстермов могут быть получены из свойств минтермов на основании (1.30). Макстермы — функции, равные нулю только в одной точке  $v_i$  области определения, состоящей из  $2^n$  точек.

Все макстермы двух переменных  $x_1$  и  $x_2$ :

$$\begin{split} &M_0(\mathbf{v}) = \overline{x_2^0} \vee \overline{x_1^0} = \overline{\overline{x_2}} \vee \overline{\overline{x_1}} = x_2 \vee x_1; \\ &M_1(\mathbf{v}) = \overline{x_2^0} \vee \overline{x_1^1} = \overline{\overline{x_2}} \vee \overline{x_1} = x_2 \vee \overline{x_1}; \\ &M_2(\mathbf{v}) = \overline{x_2^1} \vee \overline{x_1^0} = \overline{x_2} \vee \overline{\overline{x_1}} = \overline{x_2} \vee x_1; \\ &M_3(\mathbf{v}) = \overline{x_2^1} \vee \overline{x_1^1} = \overline{x_2} \vee \overline{x_1}. \end{split}$$

Запишем макстерм  $M_5(v)$  для n = 4:

$$M_5(v) = \overline{x_4^0} \vee \overline{x_3^1} \vee \overline{x_2^0} \vee \overline{x_1^1} = \overline{\overline{x_4}} \vee \overline{x_3} \vee \overline{\overline{x_2}} \vee \overline{x_1} = x_4 \vee \overline{x_3} \vee x_2 \vee x_1.$$

Минтермы (макстермы) представляют собой функции, принимающие минимальное (максимальное) значение из значений своих первичных термов  $x_p^{e_p}$ , т. е. если хотя бы один из первичных термов  $x_p^{e_p}$  равен 0 (1), то и минтерм (макстерм) равен 0 (1).

# 1.2.6 Формы аналитического представления логических функций

Логические функции, которые считаются полностью определенными, при аналитической записи могут быть представлены различными формами.

$C\mathcal{L}H\Phi$  — совершенная дизъюнктивная нормальная форма. Теорему разложения (1.20) для функции n переменных можно использовать n раз, т. е. функцию можно разложить по всем n переменным  $x_p$ , где  $p=1,\,2,\,...,\,n$ . В качестве примера разложим функцию  $F(v)=F(x_2,\,x_1)$  двух переменных  $x_2$  и  $x_1$ . По теореме разложения получим

$$F(x_{2}, x_{1}) = x_{2} \cdot F(1, x_{1}) \vee \overline{x}_{2} \cdot F(0, x_{1}) =$$

$$= x_{1} \left[ x_{2} \cdot F(1, 1) \vee \overline{x}_{2} \cdot F(0, 1) \right] \vee \overline{x}_{1} \left[ x_{2} \cdot F(1, 0) \vee \overline{x}_{2} \cdot F(0, 0) \right] =$$

$$= \overline{x}_{2} \cdot \overline{x}_{1} \cdot F(0, 0) \vee \overline{x}_{2} \cdot x_{1} \cdot F(0, 1) \vee x_{2} \cdot \overline{x}_{1} \cdot F(1, 0) \vee x_{2} \cdot x_{1} \cdot F(1, 1) =$$

$$= x_{2}^{0} \cdot x_{1}^{0} \cdot F(0, 0) \vee x_{2}^{0} \cdot x_{1}^{1} \cdot F(0, 1) \vee x_{2}^{1} \cdot x_{1}^{0} \cdot F(1, 0) \vee x_{2}^{1} \cdot x_{1}^{1} \cdot F(1, 1) =$$

$$= \sum_{i=0}^{3} x_{2}^{e_{2}} \cdot x_{1}^{e_{1}} \cdot F(e_{2}, e_{1}) = \sum_{i=0}^{3} K_{i}(v) \cdot F(v_{i}) = \sum_{i=0}^{3} a_{i} \cdot K_{i}(v),$$

где  $v_i = (e_2, e_1) - i$ -я точка области определения,  $i = (e_2 e_1)_2$ ;

$K_i(v) = x_2^{e_2} \cdot x_1^{e_1}$  – минтерм двух переменных  $x_2$  и  $x_1$ ;

$F(v_i) = a_i = 0$  или 1 — значение функции в *i*-й точке области определения.

Такая форма представления функции двух переменных и называется СДНФ. Разложение функции n переменных будет представлять собой дизьюнкцию  $2^n$  членов вида  $x_n^{e_n} \cdot \ldots \cdot x_1^{e_1} \cdot F(e_n, \ldots, e_1) = K_i(v) \cdot F(v_i) = a_i \cdot K_i(v)_i$ :

$$F(v) = \sum_{i=0}^{2^{n}-1} a_{i} \cdot K_{i}(v).$$

(1.34)

Выражение (1.34) представляет собой СДН $\Phi$  функции n переменных.

Так как значения функции  $a_i=0$  или 1, то  $a_i\cdot K_i(\nu)=0$ , если  $a_i=0$ , и  $a_i\cdot K_i(\nu)=K_i(\nu)$ , если  $a_i=1$ . Поэтому СДНФ можно представить в виде

$$F(v) = \sum_{i1} K_{i1}(v), \qquad (1.35)$$

где i1 – номера точек области определения, в которых функция F(v) равна 1.

СДНФ записи функции легко получить по ее таблице истинности. В качестве примера рассмотрим функцию трех переменных  $x_3$ ,  $x_2$  и  $x_1$ , заданную таблицей истинности (таблица 1.2). Из нее следует, что  $a_0 = a_1 = a_4 = a_6 = 0$ ,  $a_2 = a_3 = a_5 = a_7 = 1$ , поэтому

$$F(\mathbf{v}) = K_2(\mathbf{v}) \vee K_3(\mathbf{v}) \vee K_5(\mathbf{v}) \vee K_7(\mathbf{v}) =$$

$$= \overline{x}_3 \cdot x_2 \cdot \overline{x}_1 \vee \overline{x}_3 \cdot x_2 \cdot x_1 \vee x_3 \cdot \overline{x}_2 \cdot x_1 \vee x_3 \cdot x_2 \cdot x_1.$$

| i | <i>x</i> <sub>3</sub> | $x_2$ | $x_1$ | F(v) |

|---|-----------------------|-------|-------|------|

| 0 | 0                     | 0     | 0     | 0    |

| 1 | 0                     | 0     | 1     | 0    |

| 2 | 0                     | 1     | 0     | 1    |

| 3 | 0                     | 1     | 1     | 1    |

| 4 | 1                     | 0     | 0     | 0    |

| 5 | 1                     | 0     | 1     | 1    |

| 6 | 1                     | 1     | 0     | 0    |

Таблица 1.2 – Таблица истинности функции трех переменных

$CKH\Phi$  — совершенная конъюнктивная нормальная форма. Такую форму записи функции n переменных F(v) можно получить на основании двойственной теоремы разложения (1.22). Однако СКНФ можно получить более простым способом — записав СДНФ инверсии функции  $\overline{F(v)}$ . Инверсная функция в каждой точке  $v_i$  области определения имеет инверсные значения  $\overline{a_i}$  по отношению к значениям  $a_i$  самой функции, т. е. если  $F(v_i) = a_i$ , то  $\overline{F(v_i)} = \overline{a_i}$ .

Тогда на основании (1.34) СДНФ инверсной функции

$$\overline{F(v)} = \sum_{i=0}^{2^{n} - 1} \overline{a}_{i} \cdot K_{i}(v). \tag{1.36}$$

Отсюда на основании закона двойственности (1.20) следует

$$F(v) = \sum_{i=0}^{2^{n}-1} \overline{a_{i}} \cdot K_{i}(v) = \prod_{i=0}^{2^{n}-1} \overline{(\overline{a_{i}} \cdot K_{i}(v))} = \prod_{i=0}^{2^{n}-1} (a_{i} \vee \overline{K_{i}(v)}).$$

(1.37)

Используя определение макстермов (1.30), получаем СКНФ представления функции n переменных:

$$F(v) = \prod_{i=0}^{2^{n} - 1} (a_i \vee M_i(v)). \tag{1.38}$$

Так как значения функции  $a_i=0$  или 1, то  $a_i\vee M_i(v)=1$ , если  $a_i=1$ , и  $a_i\vee M_i(v)=M_i(v)$ , если  $a_i=0$ . Поэтому СКНФ можно представить в виде

$$F(v) = \prod_{i,0} M_{i,0}(v), \qquad (1.39)$$

где i0 – номера точек области определения, в которых функция F(v) равна 0.

Для примера рассмотрим функцию трех переменных  $x_3$ ,  $x_2$  и  $x_1$ , заданную таблицей истинности (см. таблицу 1.2). Так как  $a_0 = a_1 = a_4 = a_6 = 0$ , то на основании (1.39) СКНФ функции имеет вид

$$F(\mathbf{v}) = M_0(\mathbf{v}) \cdot M_1(\mathbf{v}) \cdot M_4(\mathbf{v}) \cdot M_6(\mathbf{v}) =$$

$$= (x_3 \lor x_2 \lor x_1) \cdot (x_3 \lor x_2 \lor \overline{x}_1) \cdot (\overline{x}_3 \lor x_2 \lor x_1) \cdot (\overline{x}_3 \lor \overline{x}_2 \lor x_1).$$

Совершенные нормальные формы в базисах И-НЕ и ИЛИ-НЕ. Совокупность элементарных функций, с помощью которых можно записать любую функцию F(v), называется функционально полной системой функций или базисом. Из выражений (1.35) и (1.39) следует, что для представления любой функции F(v) в СДНФ и СКНФ достаточно использовать только операции (функции) И, ИЛИ и НЕ (операция НЕ нужна для получения первичных термов  $\overline{x_p}$ , входящих в минтермы и макстермы), т. е. совокупность этих операций является базисом.

Преобразуем СДНФ функции (1.34) с использованием закона двойного отрицания и закона двойственности:

$$F(v) = \sum_{i=0}^{2^{n} - 1} a_{i} \cdot K_{i}(v) = \prod_{i=0}^{2^{n} - 1} a_{i} \cdot K_{i}(v).$$

(1.40)

Данная форма представления функции называется совершенной нормальной формой ( $CH\Phi$ ) в базисе U-HE, т. к. она требует использования только функций U-HE.

Преобразуем теперь СКНФ функции (1.38) с использованием закона двойного отрицания и закона двойственности:

$$F(v) = \prod_{i=0}^{2^{n} - 1} (a_i \vee M_i(v)) = \sum_{i=0}^{2^{n} - 1} (a_i \vee M_i(v)).$$

(1.41)

Данная форма представления функции называется *совершенной нормальной формой в базисе ИЛИ-НЕ*, т. к. она требует использования только функций ИЛИ-НЕ.

СНФ функции, рассматриваемой в качестве примера, в базисах И-НЕ и ИЛИ-НЕ будут записаны в виде

$$F(v) = \overline{\overline{x_3} \cdot x_2 \cdot \overline{x_1}} \cdot \overline{\overline{x_3} \cdot x_2 \cdot x_1} \cdot \overline{x_3} \cdot \overline{x_2} \cdot \overline{x_1} \cdot \overline{x_3} \cdot \overline{x_2} \cdot \overline{x_1};$$

$$F(v) = \overline{(\overline{x_3} \vee x_2 \vee x_1) \vee (\overline{x_3} \vee x_2 \vee \overline{x_1}) \vee (\overline{x_3} \vee x_2 \vee x_1) \vee (\overline{x_3} \vee \overline{x_2} \vee x_1)}.$$

Таким образом, термин «дизъюнктивная (конъюнктивная)» форма представления функции подразумевает, что в логическом выражении, задающем функцию, последняя выполняемая операция – дизъюнкция (конъюнкция), термин «нормальная» форма – в логическом выражении, задающем функцию, последовательно выполняется не более двух операций из совокупности операций И, ИЛИ, И-НЕ, ИЛИ-НЕ, «совершенная» – все минтермы (макстермы), входящие в логическое выражение, имеют одинаковую размерность, т. е. содержат одинаковый набор переменных.

# 2 МИНИМИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ

Одной из основных задач, возникающих при синтезе схем цифровых устройств, является минимизация логических функций, которые она реализует. Чем проще логические выражения, описывающие функции, тем проще и дешевле реализующая их цифровая схема.

Существует два основных «ручных» метода минимизации логических функций:

- 1 Аналитический метод с использованием законов и правил алгебры логики.

- 2 Табличный метод, при котором функция представляется в виде карты Карно (диаграммы Вейча).

Аналитический метод минимизации базируется на отыскании соседних элементов в записи функции и их объединении на основании законов алгебры логики.

Два минтерма  $K_i$  (v) и  $K_j$ (v) (макстерма  $M_i$  (v) и  $M_j$ (v)) называются coced- ними, если они различаются только одним первичным термом  $x_p$  (т. е., если один из минтермов содержит  $x_p$ , а другой  $\overline{x}_p$ , все же остальные первичные

термы одинаковые). Так, например, минтермы  $K_2(v) = \overline{x}_3 x_2 \overline{x}_1$  и  $K_6(v) = x_3 x_2 \overline{x}_1$  являются соседними, т. к. они различаются только одним первичным термом  $x_3$ . Для минтерма  $K_2(v)$  соседними будут также минтермы  $K_0(v) = \overline{x}_3 \overline{x}_2 \overline{x}_1$ ,  $K_3(v) = \overline{x}_3 x_2 x_1$ . Очевидно, что каждый минтерм (макстерм) n переменных  $K_i(v)$  имеет по n соседних минтермов (макстермов) из общего числа  $2^n$ . На основании свойств дизьюнкции и конъюнкции один и тот же минтерм (макстерм), входящий в СДНФ (СКНФ) может использоваться несколько раз для объединения с соседними минтермами (макстермами).

Пусть задана СКНФ функции трех переменных  $F(v) = K_0(v) \lor K_2(v) \lor V$   $\lor K_3(v) \lor K_6(v) = \bar{x}_3 \bar{x}_2 \bar{x}_1 \lor \bar{x}_3 x_2 \bar{x}_1 \lor \bar{x}_3 x_2 \bar{x}_1 \lor x_3 x_2 \bar{x}_1$ . Здесь для минимизации минтерм  $K_2(v) = \bar{x}_3 x_2 \bar{x}_1$  необходимо использовать три раза:

$$F(\mathbf{v}) = (\overline{x}_3 \overline{x}_2 \overline{x}_1 \vee \overline{x}_3 x_2 \overline{x}_1) \vee (\overline{x}_3 x_2 x_1 \vee \overline{x}_3 x_2 \overline{x}_1) \vee (x_3 x_2 \overline{x}_1 \vee \overline{x}_3 x_2 \overline{x}_1) =$$

$$= \overline{x}_3 \overline{x}_1 (\overline{x}_2 \vee x_2) \vee \overline{x}_3 x_2 (x_1 \vee \overline{x}_1) \vee x_2 \overline{x}_1 (x_3 \vee \overline{x}_3) = \overline{x}_3 \overline{x}_1 \vee \overline{x}_3 x_2 \vee x_2 \overline{x}_1.$$

Уже из этого элементарного примера видно, что аналитический метод достаточно сложен в силу трудоемкости поиска соседних минтермов.

*Табличный метод* минимизации логической функции базируется на использовании диаграммы Вейча (карты Карно), которая является одним из способов табличного задания функции и состоит из клеток, каждая из которых соответствует определенной точке  $v_i$  области определения функций, т. е. диаграммы Вейча для функции n переменных состоят из  $2^n$  клеток, которые можно пронумеровать числами  $i=0,1,...,2^n-1$ . Чтобы с помощью диаграммы Вейча задать функцию F(v), необходимо в каждую клетку с номером i занести значение функции  $F(v_i) = a_i = 0$  или 1, которое она принимает в точке i. Таким образом, одна строка таблицы истинности функции в диаграмме Вейча представляется одной ячейкой.

Для составления диаграммы Вейча (карты Карно) рисуется таблица, ее строки и столбцы нумеруются в двоичном коде и им присваиваются переменные. Вид диаграммы Вейча и карты Карно для функции четырех переменных представлен на рисунке 2.1. Здесь для наглядности координаты клеток указаны в трех формах: в виде соответствующего минтерма; в виде двоичного числа, соответствующего порядковому номеру наборов аргументов; в десятичном эквиваленте номеров наборов аргументов.

| Ϋ́       |                                                                             |                                                                                        |                                                                                                              |                                                                                                           | Y、y      | 4 <b>X</b> 3                                                                               |                                                                             |                                                                                                    |                                                                                                         |

|----------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| $X_2X_1$ | 00                                                                          | 01                                                                                     | 10                                                                                                           | 11                                                                                                        | $X_2X_1$ | 00                                                                                         | 01                                                                          | 11                                                                                                 | 10                                                                                                      |

| 00       | $\overline{X}_4\overline{X}_3\overline{X}_2\overline{X}_1$ 0000             | $\overline{X}_4 X_3 \overline{X}_2 \overline{X}_1$ 0 1 0 0 4                           | <i>x</i> <sub>4</sub> <i>x</i> <sub>3</sub> <i>x</i> <sub>2</sub> <i>x</i> <sub>1</sub><br>1000<br>8         | $x_4 x_3 \overline{x}_2 \overline{x}_1$<br>1 1 0 0<br>12                                                  | 00       | $ \overline{X}_{4}\overline{X}_{3}\overline{X}_{2}\overline{X}_{1} \\ 0 \ 0 \ 0 \ 0 \\ 0 $ | $\overline{X}_4 X_3 \overline{X}_2 \overline{X}_1$ 0 1 0 0 4                | $x_4x_3\overline{x}_2\overline{x}_1$<br>1 1 0 0<br>12                                              | $ \begin{array}{c} x_4\overline{x}_3\overline{x}_2\overline{x}_1\\ 1\ 0\ 0\ 0\\ 8 \end{array} $         |

| 01       | \$\overline{X}_4 \overline{X}_2 \overline{X}_2 \overline{X}_1\$  0 0 0 1  1 | \$\overline{X}_4 \times_3 \overline{X}_2 \overline{X}_1\$ 0 1 0 1 5                    | <i>x</i> <sub>4</sub> <i>x</i> <sub>3</sub> <i>x</i> <sub>2</sub> <i>x</i> <sub>1</sub><br>1 0 0 1<br>9      | <i>x</i> <sub>4</sub> <i>x</i> <sub>3</sub> <i>x̄</i> <sub>2</sub> <i>x</i> <sub>1</sub><br>1 1 0 1<br>13 | 01       | $ \overline{X}_{4}\overline{X}_{3}\overline{X}_{2}X_{1} \\ 0 0 0 1 \\ 1 $                  | \$\overline{X}_4 \times_3 \overline{X}_2 \overline{X}_1\$ \$0 1 0 1\$ \$5\$ | <i>X</i> <sub>4</sub> <i>X</i> <sub>3</sub> <i>X</i> <sub>2</sub> <i>X</i> <sub>1</sub> 1 1 0 1 13 | <i>x</i> <sub>4</sub> <i>x</i> <sub>3</sub> <i>x</i> <sub>2</sub> <i>x</i> <sub>1</sub><br>1 0 0 1<br>9 |

| 10       | $ \overline{x}_{4}\overline{x}_{3}x_{2}\overline{x}_{1} $ 0010 2            | $\overline{x}_4 x_3 x_2 \overline{x}_1$ 0 1 1 0 6                                      | <i>x</i> <sub>4</sub> <i>x</i> ̄ <sub>3</sub> <i>x</i> <sub>2</sub> <i>x</i> ̄ <sub>1</sub><br>1 0 1 0<br>10 | <i>X</i> <sub>4</sub> <i>X</i> <sub>3</sub> <i>X</i> <sub>2</sub> <i>X</i> <sub>1</sub><br>1 1 1 0<br>14  | 11       | $\overline{x}_{4}\overline{x}_{3}x_{2}x_{1}$ 0011 3                                        | x₄x₃x₂x₁<br>0111<br>7                                                       | x <sub>4</sub> x <sub>3</sub> x <sub>2</sub> x <sub>1</sub><br>1 1 1 1<br>15                       | $x_{4}\overline{x}_{3}x_{2}\overline{x}_{1}$ 1 0 1 1 11                                                 |

| 11       | $\overline{x}_{4}\overline{x}_{3}x_{2}x_{1}$ 0011                           | <del>X</del> <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub><br>0 1 1 1<br>7 | x <sub>4</sub> \overline{X} <sub>3</sub> x <sub>2</sub> \overline{X} <sub>1</sub> 1 0 1 1 11                 | x <sub>4</sub> x <sub>3</sub> x <sub>2</sub> x <sub>1</sub><br>1 1 1 1<br>15                              | 10       | $ \overline{x}_{4}\overline{x}_{3}x_{2}\overline{x}_{1} $ 0010 2                           | $\overline{x}_{4}x_{3}x_{2}\overline{x}_{1}$ 0 1 1 0 6                      | x <sub>4</sub> x <sub>3</sub> x <sub>2</sub> x̄ <sub>1</sub><br>1 1 1 0<br>14                      | $x_{4}\overline{x}_{3}x_{2}\overline{x}_{1}$ 1 0 1 0 10                                                 |

|          |                                                                             | a                                                                                      | l                                                                                                            |                                                                                                           |          |                                                                                            | (                                                                           | 5                                                                                                  |                                                                                                         |

Рисунок 2.1 – Вид диаграммы Вейча (a) и карты Карно для функции четырех аргументов (б)

Следует отметить, что диаграмма Вейча отличается от карты Карно только в способе обозначения строк и столбцов. В диаграмме Вейча строки и столбцы пронумерованы в порядке нарастания двоичных чисел (00, 01, 10, 11), а в карте Карно – последовательностью чисел в коде Грея (00, 01, 11, 10), что делает все клетки карты Карно соседними. Это свойство определяет более широкое применение при минимизации функции именно карты Карно.

Для представления логической функции картой Карно необходимо последнюю заполнить единицами и нулями согласно значениям функции, определяемым ее таблицей истинности либо логическим выражением.

Для минимизации функции единицы в карте объединяются замкнутыми контурами в группы по правилам:

- 1 Число единиц в группе должно быть  $2^k$ , где k=0,1,2,3..., следовательно, допустимое число клеток в контуре 1,2,4,8,....

- 2 Внутри контура должны быть только клетки, заполненные единицами, одна и та же клетка может входить в несколько контуров.

- 3 Крайние столбцы и строки карты Карно являются соседними и их клетки могут входить в общий контур.

- 4 Число контуров (групп) должно быть минимальным, охватывая все единичные клетки.

- 5 При записи минтермов в минимизированной функции исключаются переменные, имеющие взаимоинверсные значения (0 и 1 либо x и  $\overline{x}$ ).

В качестве примера минимизации рассмотрим функцию четырех аргументов, заданную таблицей истинности (таблица 2.1)

Таблица 2.1 – Таблица истинности логической функции

| N  | $x_1$ | $x_2$ | $x_3$ | $x_4$ | $F(x_1, x_2, x_3, x_4)$ |

|----|-------|-------|-------|-------|-------------------------|

| 0  | 0     | 0     | 0     | 0     | $F_0(0,0,0,0) = 0$      |

| 1  | 0     | 0     | 0     | 1     | $F_1(0,0,0,1) = 1$      |

| 2  | 0     | 0     | 1     | 0     | $F_2(0,0,1,0) = 0$      |

| 3  | 0     | 0     | 1     | 1     | $F_3(0,0,1,1) = 0$      |

| 4  | 0     | 1     | 0     | 0     | $F_4(0,1,0,0) = 1$      |

| 5  | 0     | 1     | 0     | 1     | $F_5(0,1,0,1) = 0$      |

| 6  | 0     | 1     | 1     | 0     | $F_6(0,1,1,0) = 1$      |

| 7  | 0     | 1     | 1     | 1     | $F_7(0,1,1,1) = 0$      |

| 8  | 1     | 0     | 0     | 0     | $F_8(1,0,0,0) = 1$      |

| 9  | 1     | 0     | 0     |       | $F_9(1,0,0,1) = 1$      |

| 10 | 1     | 0     | 1     | 0     | $F_{10}(1,0,1,0) = 1$   |

| 11 | 1     | 0     | 1     | 1     | $F_{11}(1,0,1,1) = 1$   |

| 12 | 1     | 1     | 0     | 0     | $F_{12}(1,1,0,0) = 0$   |

| 13 | 1     | 1     | 0     | 1     | $F_{13}(1,1,0,1) = 0$   |

| 14 | 1     | 1     | 1     | 0     | $F_{14}(1,1,1,0) = 1$   |

| 15 | 1     |       | 1     | 1     | $F_{15}(1,1,1,1) = 1$   |

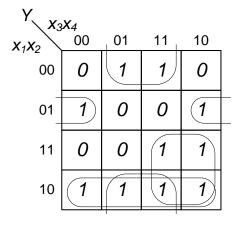

Карта Карно, соответствующая данной функции, представлена на рисунке 2.2.

Рисунок 2.2 – Карта Карно для функции  $F(x_1, x_2, x_3, x_4)$

Объединяем единичные клетки в группы и записываем результат минимизации в минимальной ДНФ:

$$F(x) = x_1 \cdot \overline{x_2} \vee \overline{x_2} \cdot x_4 \vee x_1 \cdot x_3 \vee \overline{x_1} \cdot x_2 \cdot \overline{x_4}.$$

Основная задача минимизации не полностью определенных функций заключается в отыскании оптимального варианта ее доопределения, позволяющего получить минимальную из всех возможных ДНФ или КНФ. Если значения функции не заданы в m точках, то ее можно доопределить  $2^m$  способами. Поэтому минимизация неполностью определенной функции состоит в оптимальном выборе одной из  $2^m$  полностью определенных функций (понятно, что, как и при минимизации полностью определенных функций, может быть получено несколько равноценных МДНФ и МКНФ). Следует иметь в виду, что в результате минимизации неполностью определенных функций всегда получаются полностью определенные функции.

# 3 ТИПОВЫЕ КОМБИНАЦИОННЫЕ СХЕМЫ

#### 3.1 Базовые логические элементы

Физическое устройство, реализующее одну из основных операций алгебры логики или простейшую переключательную функцию, называется логическим элементом (ЛЭ). Схема, составленная из конечного числа ЛЭ путем соединения выходов одних ЛЭ со входами других по определенным правилам, называется логической схемой (ЛС). В общем случае считаем, что построение ЛС основано на следующих правилах:

- выход ЛЭ можно подсоединять ко входам нескольких ЛЭ;

- на входы ЛЭ можно подавать сигналы, представляющие собой константы 0 и 1;

- выходы ЛЭ нельзя соединять вместе;

- выходы ЛЭ нельзя подключать к собственным входам;

- ЛС может иметь любое число обратных связей, по которым выходные сигналы некоторых ЛЭ возвращаются на собственные входы, предварительно пройдя через некоторое число ЛЭ.

Если ЛС полностью описывается переключательными функциями  $y_i = F_i(x_n, ..., x_1)$  (одной или несколькими), то она называется комбинационной схемой (КС). Таким образом, логическое состояние выходного сигнала КС однозначно определяется только текущим логическим состоянием входных сигналов. В таких схемах нет обратных связей, по которым сигнал с выхода схемы может пройти на ее вход. При наличии цепей обратной связи схема становится последовательностной.

Проектирование КС осуществляется по этапам:

- 1 На основании словесной формулировки задачи составляется таблица истинности, задающая значения функции на всех наборах аргументов.

- 2 При использовании аналитического или табличного метода производится минимизация логического выражения.

- 3 При использовании полученного выражения в качестве структурной формулы, при необходимости, осуществляется переход к заданному логическому базису.

- 4 Синтезируется схема с использованием базовых логических элементов.

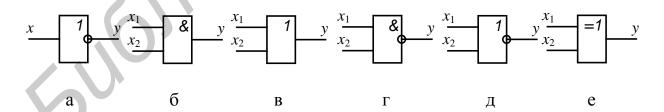

В качестве базовых используются ЛЭ, получившие название исходя из реализуемой логической функции: элемент (схема) НЕ, инвертор; элемент (схема) И, конъюнктор; элемент (схема) ИЛИ, дизъюнктор; элемент (схема) И-НЕ; элемент (схема) исключающее ИЛИ, сумматор по модулю два. Их условные графические изображения представлены на рисунке 3.1. ЛЭ И, ИЛИ, И-НЕ, ИЛИ-НЕ могут иметь более двух входов, реализуя соответствующие логические функции большего числа переменных.

а – НЕ; б – И; в – ИЛИ; г – И-НЕ; д – ИЛИ-НЕ; е – исключающее ИЛИ Рисунок 3.1 – Условные графические обозначения базовых ЛЭ

В любом реальном ЛЭ имеется некоторая паразитная задержка между моментом времени, в который на его входы поступают новые значения сигналов, и моментом времени, когда выходной сигнал принимает значение, опреде-

ляемое функцией, которую выполняет ЛЭ. Эта функция представляет собой статическую модель ЛЭ, т. к. она не учитывает поведение ЛЭ при изменении входных сигналов. Аналогично этому логическая функция или система функций, описывающая работу КС без обратных связей, является ее статической моделью.

Для учета переходных процессов, вызываемых в ЛС изменениями входных сигналов, необходимо использовать динамические модели ЛЭ, учитывающие паразитные задержки. Тогда динамическая модель ЛС в целом будет определяться динамической моделью ЛЭ и статической моделью ЛС.

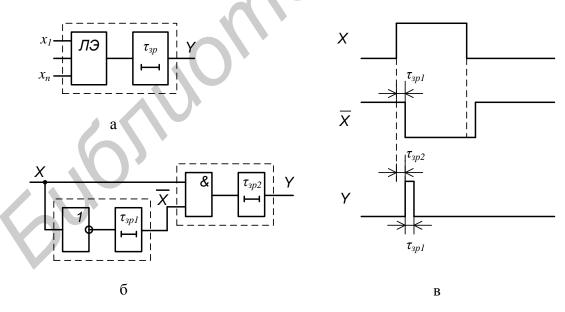

В простейшем случае реальный ЛЭ можно представить в виде последовательного включения идеального ЛЭ, статическая модель которого соответствует выполняемой логической функции и линии задержки на время задержки переключения (рисунок 3.2, а). Учет конечных времен задержек в реальных ЛЭ показывает, что существуют интервалы времени, в пределах которых логическое состояние выхода схемы будет отличаться от тех, что описываются статической моделью. Так, для простейшей схемы (рисунок 3.2, б) статическая модель определяет постоянное нулевое состояние выхода ( $Y = X \cdot \overline{X} = 0$ ), а динамическая — позволяет объяснить появление короткого единичного импульса (рисунок 3.2, в) за счет различных времен задержек в цепях, предшествующих входам ЛЭ.

а – динамическая модель логического элемента;

б – модель логической схемы;

в – временные диаграммы работы

Рисунок 3.2 – Моделирование логической схемы

Максимальное число последовательно выполняемых логических операций для реализации функции  $F(x_n, ..., x_1)$  называется *порядком переключательной функции*. Функции, представленные в любой нормальной форме, имеют порядок не выше второго. Порядком КС называется максимальное число последовательно включенных ЛЭ. Порядки КС и соответствующих им функций совпадают. Очевидно, чем выше порядок КС, тем меньше ее быстродействие.

Для представления логических функций можно использовать не только нормальные формы. Некоторые тождественные преобразования МНФ могут привести к уменьшению числа первичных термов в аналитическом представлении функции, а значит и к уменьшению стоимости ее реализации на ЛЭ.

Так, преобразование МДНФ с помощью первого дистрибутивного закона (1.9) приводит к скобочным формам представления функций и сокращению числа первичных термов.

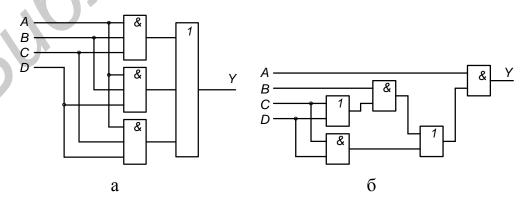

Например, в результате минимизации некой логической функции получено выражение

$$Y = A \cdot B \cdot C \vee A \cdot B \cdot D \vee A \cdot C \cdot D. \tag{3.1}$$

Этой функции соответствует схема второго порядка, представленная на рисунке 3.3, а. На основании дистрибутивных законов функцию (3.1) можно представить в скобочной форме

$$Y = A \cdot (B \cdot (C \vee D) \vee C \cdot D), \tag{3.2}$$

которой соответствует схема на рисунке 3.3, б. В этой КС максимальное число последовательно включенных ЛЭ равно четырем, т. е. КС имеет четвертый порядок.

а – на основе МДНФ (3.1); б – на основе скобочной формы (3.2) Рисунок 3.3 – Варианты схемной реализации логической функции

Наряду с базовыми ЛЭ широкое применение находят типовые КС: мультиплексоры, демультиплексоры, шифраторы, дешифраторы, арифметические устройства и др.

### 3.2 Мультиплексоры и демультиплексоры

*Мультиплексоры* (multiplexer) – это функциональный узел, который по заданному адресному двоичному коду осуществляет выбор одного из информационных каналов и подключает его к своему выходу.

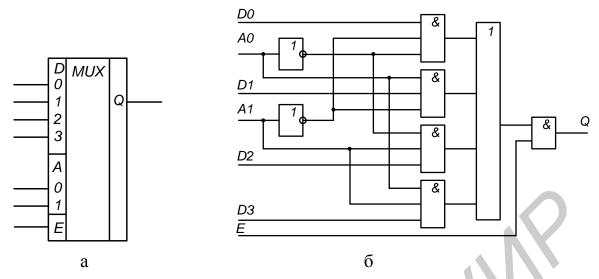

Условное графическое обозначение мультиплексора приведено на рисунке 3.4, a.

В общем случае на входы мультиплексора  $D_0 \dots D_{n-1}$  поступают по информационным каналам n-разрядные сигналы. Число информационных каналов, коммутируемых на выход Q, составляет m=2,4,8,16. При m=4 и Q=1 мультиплексор имеет размерность 4-1. Это 4-канальный одноразрядный мультиплексор, на выход которого передается один из четырех входных сигналов.

На входы  $A_0 \dots A_{n-1}$  подается n-разрядный адресный код, при этом каждому информационному каналу присваивается свой адрес (номер), а общее число комбинаций адресных сигналов  $N=2^n$ .

Вход E (enable) разрешает (либо запрещает) работу мультиплексора при подаче на него сигналов управления.

| Адресные в | ходы  | Вход разрешения | Выход |

|------------|-------|-----------------|-------|

| $A_1$      | $A_0$ | E               | Q     |

| *          | *     | 0               | 0     |

| 0          | 0     | 1               | $D_0$ |

| 0          | 1     | 1               | $D_1$ |

| 1          | 0     | 1               | $D_2$ |

| 1          | 1     | 1               | $D_3$ |

Таблица 3.1 – Таблица истинности мультиплексора 4 – 1

Согласно данным таблицы 3.1 логическая функция Q, реализуемая мультиплексором 4 — 1, описывается выражением

$$Q = E \cdot (D_0 \cdot \overline{A}_1 \cdot \overline{A}_0 \vee D_1 \cdot \overline{A}_1 \cdot A_0 \vee D_2 \cdot A_1 \cdot \overline{A}_0 \vee D_3 \cdot A_1 \cdot A_0). \tag{3.3}$$

а – условное графическое обозначение; б – логическая схема Рисунок 3.4 – Мультиплексор 4 – 1

Если  $A_0=0,\ A_1=1,\ E=1,$  то  $Q=(D_2\cdot A_1\cdot \overline{A}_0)\cdot E=D_2,$  следовательно, при E=1 по адресному коду 10 на выход Q подключается сигнал, действующий на информационном входе  $D_2$ .

Построенная по выражению (3.3) схема мультиплексора приведена на рисунке 3.4, б.

С помощью мультиплексоров можно решать широкий круг задач, используя их как универсальные логические модули.

$\mathcal{L}$ емультиплексор осуществляет передачу сигналов с одного информационного входа D на N выходов, имеющих заданный адрес. В общем случае число выходов  $N=2^n$  и определяется количеством адресных входов n.

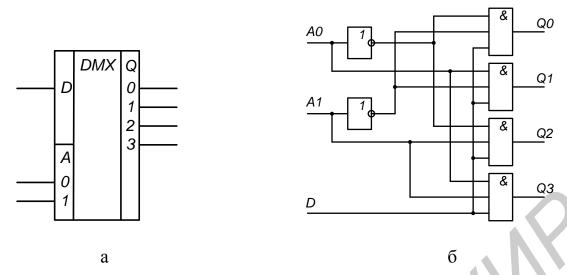

На рисунке 3.5, a показано условное обозначение демультиплексора 1-4, функционирование которого описывается таблицей 3.2 истинности.

Таблица 3.2 – Таблица истинности мультиплексора 4 – 1

| Адреснь | не входы |       | Вых   | ЮДЫ   |       |

|---------|----------|-------|-------|-------|-------|

| $A_1$   | $A_0$    | $Q_0$ | $Q_1$ | $Q_2$ | $Q_3$ |

| 0       | 0        | D     | 0     | 0     | 0     |

| 0       | 1        | 0     | D     | 0     | 0     |

| 1       | 0        | 0     | 0     | D     | 0     |

| 1       | 1        | 0     | 0     | 0     | D     |

а – условное графическое обозначение; б – логическая схема Рисунок 3.5 – Демультиплексор 1 – 4

Согласно данным таблицы истинности запишем логическое выражение для каждого выхода демультиплексора и по ним составим логическую схему (рисунок 3.5, б).

$$Q_{0} = \overline{A_{0}} \cdot \overline{A_{1}} \cdot D,$$

$$Q_{1} = A_{0} \cdot \overline{A_{1}} \cdot D,$$

$$Q_{2} = \overline{A_{0}} \cdot A_{1} \cdot D,$$

$$Q_{3} = A_{0} \cdot A_{1} \cdot D.$$

$$(3.4)$$

# 3.3 Шифраторы и дешифраторы

Шифратор (coder) предназначен для преобразования входных сигналов в виде кода «1 из т» (унитарного) в выходной *п*-разрядный двоичный код и применяется в устройстве ввода информации в цифровые системы. Таким образом, классический шифратор преобразует номер возбуждаемого входа (на который подается логическая 1) в двоичный код на своем выходе.

Шифратор называется полным, если число входов  $m=2^n$ , а число выходов равно n (n – разрядность двоичного кода).

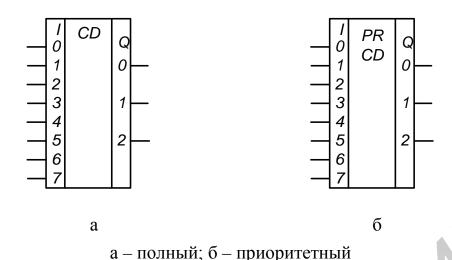

На рисунке 3.6, а показано условное графическое обозначение полного шифратора 8 – 3, а его таблица истинности приведена в таблице 3.3.

Рисунок 3.6 – Условные графические обозначения шифраторов 8 – 3

Таблица 3.3 – Таблица истинности полного шифратора 8 – 3

| Номер<br>входа |       |       |       | Входн | ой код |       |       |       | Вых   | кодной | код   |

|----------------|-------|-------|-------|-------|--------|-------|-------|-------|-------|--------|-------|

|                | $I_7$ | $I_6$ | $I_5$ | $I_4$ | $I_3$  | $I_2$ | $I_1$ | $I_0$ | $Q_2$ | $Q_1$  | $Q_0$ |

| 0              | 0     | 0     | 0     | 0     | 0      | 0     | 0     | 1     | 0     | 0      | 0     |

| 1              | 0     | 0     | 0     | 0     | 0      | 0     | 1     | 0     | 0     | 0      | 1     |

| 2              | 0     | 0     | 0     | 0     | 0      | 1     | 0     | 0     | 0     | 1      | 0     |

| 3              | 0     | 0     | 0     | 0     | 1      | 0     | 0     | 0     | 0     | 1      | 1     |

| 4              | 0     | 0     | 0     | 1     | 0      | 0     | 0     | 0     | 1     | 0      | 0     |

| 5              | 0     | 0     | 1     | 0     | 0      | 0     | 0     | 0     | 1     | 0      | 1     |

| 6              | 0     | 1     | 0     | 0     | 0      | 0     | 0     | 0     | 1     | 1      | 0     |

| 7              | 1     | 0     | 0     | 0     | 0      | 0     | 0     | 0     | 1     | 1      | 1     |

Согласно данным таблицы 3.3 значения выходных переменных шифратора определяются следующими логическими выражениями:

$$Q_{2} = I_{4} \vee I_{5} \vee I_{6} \vee I_{7};$$

$$Q_{1} = I_{2} \vee I_{3} \vee I_{6} \vee I_{7};$$

$$Q_{0} = I_{1} \vee I_{3} \vee I_{5} \vee I_{7}.$$

(3.5)

Необходимо отметить, что шифратор, реализованный по выражениям (3.5), будет правильно работать только в случае подачи на его входы унитарного кода, т. е. должно выполняться условие  $I_j \cdot I_k = 0$  при  $j \neq k$ . Для обнаружения нулевого состояния всех входов шифратора можно предусмотреть в его схеме

дополнительный выход GS. Очевидно, что логическая функция, реализуемая по этому выходу, описывается выражением

$$GS = \overline{I_0 \vee I_1 \vee I_2 \vee I_3 \vee I_4 \vee I_5 \vee I_6 \vee I_7}.$$

(3.6)

Для обработки входного кода, в котором присутствует более одной единицы, т. е. при возбуждении нескольких входов устройства, применяют *приоритетный шифратор*. В нем выходной код соответствует номеру того возбужденого входа, приоритет которого задан более высоким. На схемах приоритетный шифратор обозначается буквами *PRCD* (рисунок 3.6, б).

Таблица истинности шифратора, приоритет входов которого возрастает с увеличением номера входа, представлена таблицей 3.4.

| ,              |       | · ·   |       |       | 1 1    |       |       | 11 1  |       |        |       |

|----------------|-------|-------|-------|-------|--------|-------|-------|-------|-------|--------|-------|

| Номер<br>входа |       |       |       | Входн | ой код |       |       | 2     | Вых   | кодной | код   |

|                | $I_7$ | $I_6$ | $I_5$ | $I_4$ | $I_3$  | $I_2$ | $I_1$ | $I_0$ | $Q_2$ | $Q_1$  | $Q_0$ |

| 0              | 0     | 0     | 0     | 0     | 0      | 0     | 0     | 1     | 0     | 0      | 0     |

| 1              | 0     | 0     | 0     | 0     | 0      | 0     | 1     | *     | 0     | 0      | 1     |

| 2              | 0     | 0     | 0     | 0     | 0      | 1     | *     | *     | 0     | 1      | 0     |

| 3              | 0     | 0     | 0     | 0     | 1/     | *     | *     | *     | 0     | 1      | 1     |

| 4              | 0     | 0     | 0     | 1     | *      | *     | *     | *     | 1     | 0      | 0     |

| 5              | 0     | 0     | 1     | *     | *      | *     | *     | *     | 1     | 0      | 1     |

| 6              | 0     | 1     | *     | *     | *      | *     | *     | *     | 1     | 1      | 0     |

| 7              | 1     | *     | *     | *     | *      | *     | *     | *     | 1     | 1      | 1     |

Таблица 3.4 – Таблица истинности приоритетного шифратора 8 – 3

Состояния выходов такого приоритетного шифратора определяются следующими логическими функциями:

$$Q_{2} = I_{4} \cdot \overline{I_{5}} \cdot \overline{I_{6}} \cdot \overline{I_{7}} \vee I_{5} \cdot \overline{I_{6}} \cdot \overline{I_{7}} \vee I_{6} \overline{I_{7}} \vee I_{7} = I_{4} \vee I_{5} \vee I_{6} \vee I_{7};$$

$$Q_{1} = I_{2} \cdot \overline{I_{3}} \cdot \overline{I_{4}} \cdot \overline{I_{5}} \cdot \overline{I_{6}} \cdot \overline{I_{7}} \vee I_{3} \cdot \overline{I_{4}} \cdot \overline{I_{5}} \cdot \overline{I_{6}} \cdot \overline{I_{7}} \vee I_{6} \cdot \overline{I_{7}} \vee I_{7} =$$

$$= I_{2} \cdot \overline{I_{4}} \cdot \overline{I_{5}} \vee I_{3} \cdot \overline{I_{4}} \cdot \overline{I_{5}} \vee I_{6} \vee I_{7};$$

$$Q_{0} = I_{1} \cdot \overline{I_{2}} \cdot \overline{I_{3}} \cdot \overline{I_{4}} \cdot \overline{I_{5}} \cdot \overline{I_{6}} \cdot \overline{I_{7}} \vee I_{3} \cdot \overline{I_{4}} \cdot \overline{I_{5}} \cdot \overline{I_{6}} \cdot \overline{I_{7}} \vee I_{5} \cdot \overline{I_{6}} \cdot \overline{I_{7}} \vee I_{7} =$$

$$= I_{1} \cdot \overline{I_{2}} \cdot \overline{I_{4}} \cdot \overline{I_{6}} \vee I_{3} \cdot \overline{I_{4}} \cdot \overline{I_{6}} \vee I_{5} \cdot \overline{I_{6}} \vee I_{7}.$$

$$(3.7)$$

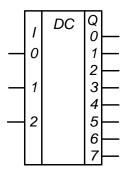

*Дешифратор* (decoder) выполняет функцию, обратную шифратору, т. е. преобразует входной n-разрядный двоичный код в унитарный («1 из m»). Таким образом, сигнал логической единицы появится только на том выходе дешифратора, номер которого соответствует десятичному эквиваленту входного двоичного кода. Дешифратор называется полным, если при n входах имеется  $m=2^n$  выходов. На схемах дешифраторы обозначаются буквами DC (рисунок 3.7).

Рисунок 3.7 – Условное графическое обозначение дешифратора 3 – 8

Рассмотрим пример синтеза полного дешифратора 3 – 8, имеющего на входе 3-разрядный двоичный код, а на восьми выходах – унитарный код.

Таблица 3.5 – Таблица истинности полного дешифратора 3 – 8

| $I_2$ | $I_1$ | $I_0$ | $Q_7$ | $Q_6$ | $Q_5$ | $Q_4$ | $Q_3$ | $Q_2$ | $Q_1$ | $Q_0$ |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

| 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     |

| 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| 0     | 1     | 1     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| 1     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

| 1     | 0     | 1     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Анализ таблицы истинности (таблица 3.5) такого дешифратора показывает, где каждой выходной функции  $Q_0...Q_7$  соответствует только один минтерм. Так как рассматриваемый дешифратор полный, то он реализует полный набор минтермов входных переменных  $I_0$ ,  $I_1$ ,  $I_2$ :

$$Q_0 = \overline{I_0} \cdot \overline{I_1} \cdot \overline{I_2} ;$$

$$Q_1 = I_0 \cdot \overline{I_1} \cdot \overline{I_2}$$

;

$$Q_{2} = \overline{I_{0}} \cdot I_{1} \cdot \overline{I_{2}};$$

$$Q_{3} = I_{0} \cdot I_{1} \cdot \overline{I_{2}};$$

$$Q_{4} = \overline{I_{0}} \cdot \overline{I_{1}} \cdot I_{2};$$

$$Q_{5} = I_{0} \cdot \overline{I_{1}} \cdot I_{2};$$

$$Q_{6} = \overline{I_{0}} \cdot I_{1} \cdot I_{2};$$

$$Q_{7} = I_{1} \cdot I_{1} \cdot I_{2}.$$

$$(3.8)$$

Если комбинационная схема реализует только один минтерм, то ее часто называют дешифратором состояния (кода).

## 3.4 Сумматоры и вычитатели

*Сумматор* (sum) – цифровой функциональный узел, выполняющий арифметическое сложение двоичных чисел.

Простейшим сумматором является полусумматор HS, осуществляющий арифметическое сложение двух одноразрядных чисел A и B (рисунок 3.8, а). Он имеет два выхода — выход S бита суммы и выход P бита переноса в старший разряд. Логика работы полусумматора описывается таблицей 3.6.

а – полусумматор; б – одноразрядный полный сумматор Рисунок 3.8 – Условные графические обозначения

Таблица 3.6 – Таблица истинности полусумматора

| A | В | S | P |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Из таблицы истинности следует, что арифметическая сумма S двух одноразрядных чисел A и B совпадает с суммированием их по модулю два:

$$S = \overline{AB} + A\overline{B} = A \oplus B. \tag{3.9}$$

Сигнал переноса в старший разряд

$$P = A \cdot B \tag{3.10}$$

появляется на выходе только тогда, когда на входы A и B поданы единицы, реализуется логическим элементом U.

Одноразрядный полный сумматор SM (рисунок 3.8, б) отличается от полусумматора HS тем, что на его дополнительный вход C поступает сигнал переноса от предыдущего разряда сумматора (таблица 3.7).

| ,                         | ,           |       | 3       | 1         |            |           |  |

|---------------------------|-------------|-------|---------|-----------|------------|-----------|--|

| $\mathbf{p}_{\mathbf{v}}$ | одные сигна | уштт  | Выходны | е сигналы | Выходны    | е сигналы |  |

| DA                        | одные сигна | 1/1DI | сумм    | атора     | вычитателя |           |  |

| A                         | В           | C     | S       | P         | D          | Z         |  |

| 0                         | 0           | 0     | 0       | 0         | 0          | 0         |  |

| 0                         | 1           | 0     | 1       | 0         | 1          | 1         |  |

| 1                         | 0           | 0     | 1       | 0         | 1          | 0         |  |

| 1                         | 1           | 0     | 0       | 1         | 0          | 0         |  |

| 0                         | 0           | 1     | 1       | 0         | 1          | 1         |  |

| 0                         | 1           | 1     | 0       | 1         | 0          | 1         |  |

| 1                         | 0           | 1     | 0       | 1         | 0          | 0         |  |

| 1                         | 1           | 1     | 1       | 1         | 1          | 1         |  |

Таблица 3.7 – Таблица истинности полного сумматора и вычитателя

Для определения бита суммы S и бита переноса P в старший разряд по таблице истинности составляем логические выражения в СДНФ и преобразуем их:

$$S = \overline{A} \cdot B \cdot \overline{C} + A \cdot \overline{B} \cdot \overline{C} + \overline{A} \cdot \overline{B} \cdot C + A \cdot B \cdot C =$$

$$= \overline{C}(\overline{A} \cdot B + A \cdot \overline{B}) + C(\overline{A} \cdot \overline{B} + A \cdot B) =$$

$$= \overline{C}(A \oplus B) + C(\overline{A \oplus B}) = A \oplus B \oplus C,$$

(3.11)

$$P = A \cdot B \cdot \overline{C} + \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot C = A \cdot B + B \cdot C + A \cdot C. \tag{3.12}$$

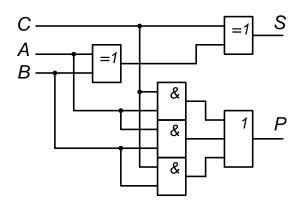

По выражениям (3.11) и (3.12) составляем логическую схему двоичного одноразрядного сумматора SM (рисунок 3.9).

Рисунок 3.9 – Логическая схема одноразрядного полного сумматора

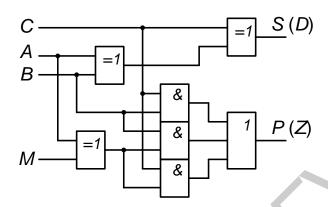

Рассмотрим реализацию универсального блока, который может вычислять не только сумму, но и разность двух одноразрядных чисел A и B, т. е. будет работать либо как сумматор SM, либо как вычитатель SUB (subtraktor).

Управление режимом работы блока осуществляется сигналом M (mode): при M=0 схема работает как сумматор, т. е. выполняет арифметическую операцию A+B+C, где C – бит переноса из младшего разряда, с формированием бита S суммы и бита P переноса в старший разряд. При M=1 схема работает как вычитатель, выполняя операцию A-B-C (при этом C трактуется как бит заема из текущего разряда), с формированием на выходе бита D разности и бита Z заема из старшего разряда (см. таблицу 3.7).

На основании совпадения данных столбцов S и D таблицы 3.7 истинности делаем вывод, что логическое выражение для определения бита D разности будет совпадать с (3.11), т. е.

$$D = A \oplus B \oplus C, \tag{3.13}$$

и, следовательно, сигналы S и D могут быть сформированы одной схемой.

Формирование бита Z заема осуществляется по выражению

$$Z = \overline{A} \cdot B \cdot \overline{C} + \overline{A} \cdot \overline{B} \cdot C + \overline{A} \cdot B \cdot C + A \cdot B \cdot C = \overline{A} \cdot B + B \cdot C + \overline{A} \cdot C, \quad (3.14)$$

которое отличается от (3.12) заменой переменной A на инверсную  $\overline{A}$  .

Схемная реализация такой замены переменной может быть осуществлена на базе элемента Исключающее ИЛИ (сложения по модулю 2), входными сигналами которой выступают A и M. На основании (1.19) можно сделать вывод,

что при M = 0 (режим сумматора) схема сложения по модулю 2 выступает в качестве повторителя сигнала A, а при M = 1 (режим вычитателя) — его инвертора.

С учетом этого по выражениям (3.11)...(3.14) составляем логическую схему одноразрядного универсального сумматора-вычитателя (рисунок 3.10).

Рисунок 3.10 – Логическая схема сумматора-вычитателя

В многоразрядных сумматорах увеличение разрядности достигается путем каскадирования, при этом выход P переноса младшего разряда соединяют с входом C переноса старшего разряда. Однако последовательное формирование бита переноса снижает быстродействие многоразрядных сумматоров. Для его повышения применяют параллельное формирование переносов в специальных блоках ускоренного переноса.

## 3.5 Цифровые компараторы

*Компаратор* (comparator) предназначен для сравнения двух двоичных чисел. С помощью компаратора можно производить проверку равенства чисел или определить какое из них больше. На схемах компаратор обозначается буквами *CMP* либо (= =).

Цифровые компараторы подразделяются на одноразрядные и многоразрядные. Простейшим одноразрядным компаратором является схема Исключающее ИЛИ-НЕ, с помощью которой реализуется функция равнозначности.

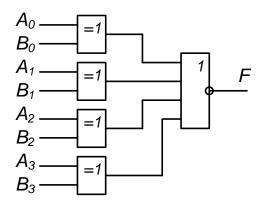

На рисунке 3.11 показана реализация четырехразрядного компаратора, выполненного на логических элементах Исключающее ИЛИ и ИЛИ-НЕ.

Рисунок 3.11 – Логическая схема четырехразрядного цифрового компаратора

При равенстве входных сигналов во всех разрядах выходной сигнал F=1, но если хотя бы в одном разряде сигналы различны, то выходной сигнал F=0.

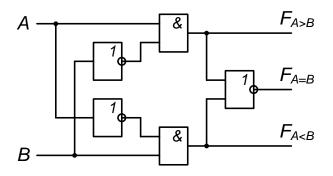

Составим таблицу истинности для одноразрядного универсального компаратора, который кроме констатации равенства двух чисел может определить, какое из них больше.

Таблица 3.8 – Таблица истинности универсального одноразрядного цифрового компаратора

| A | В | $F_{A>B}$ | $F_{A=B}$ | $F_{A < B}$ |

|---|---|-----------|-----------|-------------|

| 0 | 0 | 0         | 1         | 0           |

| 0 | 1 | 0         | 0         | 1           |

| 1 | 0 | 1         | 0         | 0           |

| 1 | 1 | 0         | 1         | 0           |

Согласно таблице 3.8 запишем логические функции, характеризующие признаки равенства или неравенства между входными числами A и B:

$$F_{A>B} = A\overline{B}; (3.15)$$

$$F_{A < B} = \overline{A}B; (3.16)$$

$$F_{A=B} = \overline{A} \cdot \overline{B} \vee A \cdot B = \overline{A \oplus B} = \overline{\overline{A} \cdot B} \vee A \cdot \overline{B} = \overline{F_{A>B}} \vee F_{A$$

По полученным выражениям (3.15)...(3.17) построим схему одноразрядного универсального компаратора (рисунок 3.12).

Рисунок 3.12 – Схема универсального одноразрядного компаратора

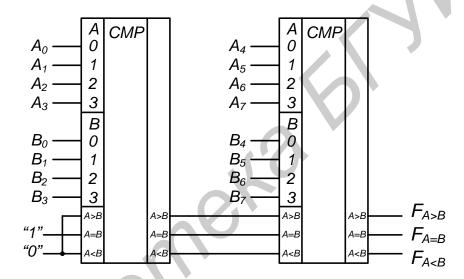

С целью повышения разрядности компараторы соединяют последовательно, как показано на рисунке 3.13 на примере двух четырехразрядных *СМР*.

Рисунок 3.13 – Вариант наращивания разрядности компараторов

## 3.6 Преобразователи кодов

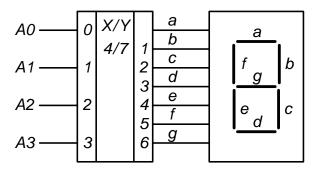

Преобразователи кодов (converter) предназначены для преобразования кода кодирования цифровой информации. На схемах преобразователи обозначаются буквами X/Y.

Преобразователи кодов отличаются достаточным многообразием, в частности, к ним можно отнести схемы шифратора и дешифратора, выполняющие взаимное преобразование двоичного и унитарного кодов.

Рассмотрим синтез преобразователя двоично-десятичного кода в специальный семиразрядный код индикатора. Подсветка всех сегментов цифрового

индикатора, образующих цифры 0...9 (рисунок 3.14), производится подачей на них единичного сигнала, вызывая свечение сегментов в определенных комбинациях.

Рисунок 3.14 – Схема управления семисегментным индикатором

Из рисунка 3.15 следует, что для цифры индикатора, например 6, которая задана двоично-десятичным кодом 0110, необходимо подсветить все сегменты, за исключением сегмента b.

Выходные переменные a, ..., g являются функциями аргументов A3, ..., A0. Определяем для функций  $F_a ... F_g$  таблицу истинности (таблица 3.9), по которой отдельно для каждой функции составляем карты Карно, при этом «лишние» ячейки карт, где функции не определены, помечаем знаком \* и доопределяем единицами.

Таблица 3.9 – Таблица истинности преобразователя кодов

| Цифра      |       | Bxc   | оды   |       |       |       | E     | Выході | J     |       |       |

|------------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|-------|

| индикатора | $A_3$ | $A_2$ | $A_1$ | $A_0$ | $F_a$ | $F_b$ | $F_c$ | $F_d$  | $F_e$ | $F_f$ | $F_g$ |

| 0          | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1      | 1     | 1     | 0     |

| 1          | 0     | 0     | 0     | 1     | 0     | 1     | 1     | 0      | 0     | 0     | 0     |

| 2          | 0     | 0     | 1     | 0     | 1     | 1     | 0     | 1      | 1     | 0     | 1     |

| 3          | 0     | 0     | 1     | 1     | 1     | 1     | 1     | 1      | 0     | 0     | 1     |

| 4          | 0     | 1     | 0     | 0     | 0     | 1     | 1     | 0      | 0     | 1     | 1     |

| 5          | 0     | 1     | 0     | 1     | 1     | 0     | 1     | 1      | 0     | 1     | 1     |

| 6          | 0     | 1     | 1     | 0     | 1     | 0     | 1     | 1      | 1     | 1     | 1     |

| 7          | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 0      | 0     | 0     | 0     |

| 8          | 1     | 0     | 0     | 0     | 1     | 1     | 1     | 1      | 1     | 1     | 1     |

| 9          | 1     | 0     | 0     | 1     | 1     | 1     | 1     | 1      | 0     | 1     | 1     |

Минимизировав логические функции  $F_a \dots F_g$ , получаем выражения для них в минимальной дизъюнктивной нормальной форме:

$$\begin{split} F_{a} &= A_{3} \cdot A_{0} \vee \overline{A_{3}} \cdot \overline{A_{0}} \vee A_{3} \vee A_{1}; \\ F_{b} &= \overline{A_{1}} \cdot \overline{A_{0}} \vee A_{1} \cdot A_{0} \vee \overline{A_{2}}; \\ F_{c} &= A_{2} \vee \overline{A_{1}} \vee A_{0}; \\ F_{d} &= A_{2} \cdot \overline{A_{1}} \cdot A_{0} \vee A_{3} \vee \overline{A_{2}} \cdot \overline{A_{0}} \vee \overline{A_{2}} \cdot A_{1} \vee A_{1} \cdot \overline{A_{0}}; \\ F_{e} &= \overline{A_{2}} \cdot \overline{A_{0}} \vee A_{1} \cdot \overline{A_{0}}; \\ F_{f} &= A_{2} \cdot \overline{A_{1}} \vee \overline{A_{1}} \cdot \overline{A_{0}} \vee A_{2} \cdot \overline{A_{0}} \vee A_{3}; \\ F_{g} &= A_{2} \cdot \overline{A_{1}} \vee A_{1} \cdot \overline{A_{0}} \vee \overline{A_{2}} \cdot A_{1} \vee A_{3}. \end{split}$$

$$(3.18)$$

## 4 ТИПОВЫЕ ПОСЛЕДОВАТЕЛЬНОСТНЫЕ СХЕМЫ

## 4.1 Потенциальные и импульсные сигналы

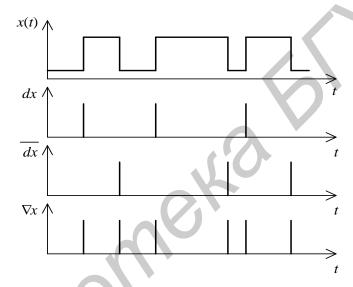

В последовательностных схемах, в отличие от комбинационных, значения выходных сигналов зависят не только от значений входных сигналов, но и от последовательности их изменений. В таких схемах (последовательных автоматах) зачастую необходимо введение в рассмотрение в явном виде времени для описания изменений сигналов. Аналитически это осуществляется путем использования операторов переходов d и  $\nabla$ .

Сигнал называется *потенциальным*, если интервал времени  $T_i$  между соседними изменениями сигнала значительно больше времени установления переходных процессов в схеме, в которой он используется. Сигнал называется *импульсным*, если длительность его активного уровня того же порядка, что и время реакции схемы (схема должна отреагировать на воздействие импульсного сигнала, а он должен закончиться сразу же после окончания в схеме переходного процесса).

При аналитическом описании схем, на которые воздействуют импульсные сигналы, используется понятие абстрактного импульсного сигнала, длительность которого бесконечно мала. Такие сигналы (dx,  $d\overline{x}$  и  $\nabla x$ ) показаны на рисунке 4.1 и соответствуют изменениям потенциального сигнала x с 0 на 1 или (и) с 1 на 0. Реальные импульсные сигналы всегда имеют конечную длительность, которая определяется временем реакции схемы. В зависимости от быст-

родействия ЛЭ, из которых построена схема, время реакции может изменяться в широких пределах. Понятие абстрактного импульсного сигнала позволяет абстрагироваться от физических параметров конкретных схем.

Оператор переходов *d* определяется соотношением

$$dx = x(t) \cdot \overline{x(t - \Delta t)}, \tag{4.1}$$

где dx — импульсный сигнал, принимающий единичное значение при изменении потенциального сигнала с 0 на 1;

x(t) — значение потенциального сигнала в текущий момент времени;

$x(t - \Delta t)$  — значение потенциального сигнала в предыдущий момент времени.

Рисунок 4.1 – Разновидности импульсных сигналов

Импульсный сигнал, соответствующий изменениям потенциального сигнала с 1 на 0:

$$d\overline{x} = \overline{x(t)} \cdot x(t - \Delta t). \tag{4.2}$$

Оператор переходов ∇ определяется соотношением

$$\nabla x = dx \vee d\overline{x} = x(t) \oplus x(t - \Delta t), \tag{4.3}$$

где  $\nabla x = 1$  как при изменении потенциального сигнала с 0 на 1, так и с 1 на 0.

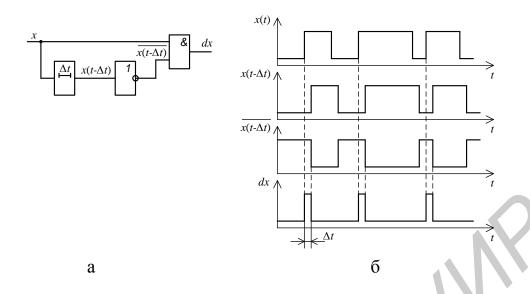

На рисунке 4.2 показана схема формирования импульсного сигнала dx и временные диаграммы ее работы в предположении, что используемые ЛЭ безынерционны.

Рисунок 4.2 — Схема формирования импульсного сигнала dx (a) и временные диаграммы ее работы (б)

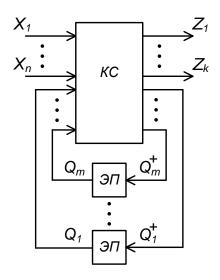

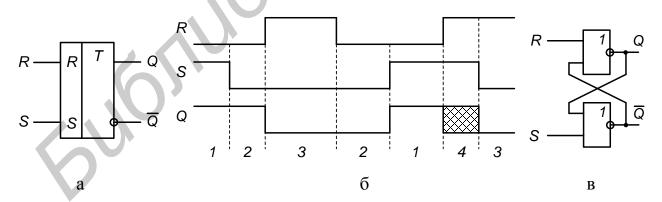

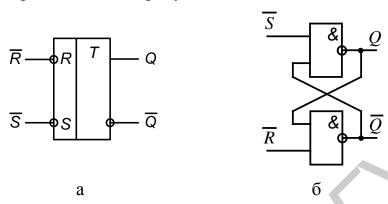

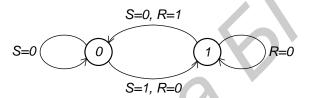

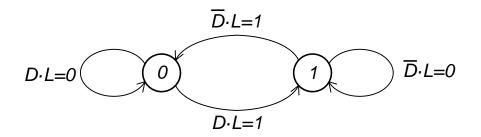

### 4.2 Модель последовательного автомата

Эта модель состоит из комбинационной схемы (КС) и элементов задержки входных сигналов  $Q_r^+$  на время  $\Delta t$ , включенных в цепях обратных связей (рисунок 4.3). Элементы задержки производят запоминание внутренних сигналов КС, т. е. они являются элементами памяти (ЭП). Эти сигналы появляются на входах КС через время  $\Delta t$  и могут вызвать изменение ее выходных сигналов. Понятно, что если сигнал  $Q_r = Q_r(t)$ , то сигнал  $Q_r^+ = Q_r(t + \Delta t)$ .

Рисунок 4.3 – Модель последовательного автомата

В общем случае автомат содержит m ЭП входных сигналов  $Q_m$ , ... $Q_r$ , ... $Q_1$ , имеет n физических входов, на которые подаются сигналы  $x_n$ , ... $x_p$ , ... $x_1$ , и k физических выходов, с которых снимаются сигналы  $z_k$ , ... $z_q$ , ...  $z_1$ .

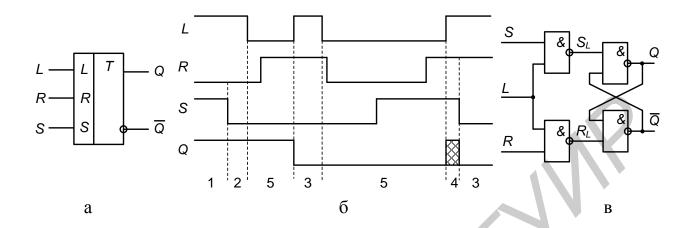

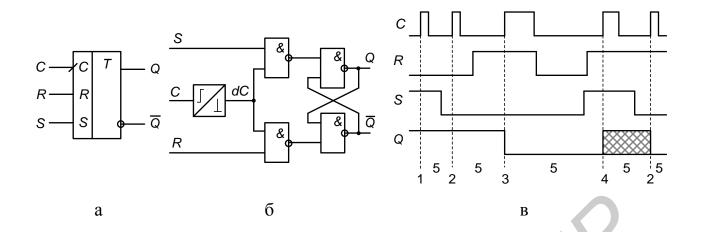

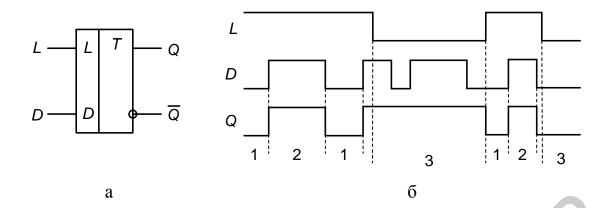

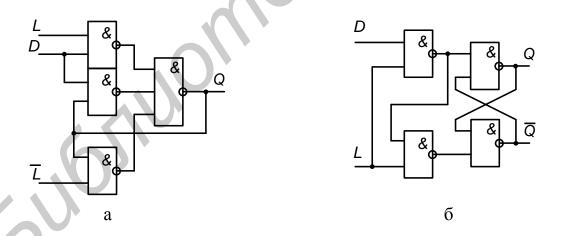

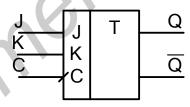

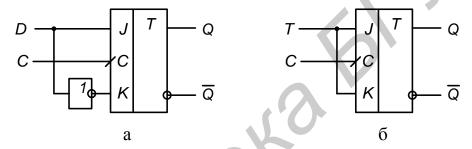

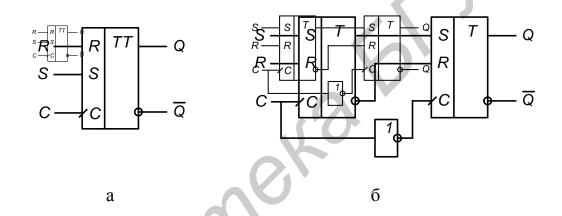

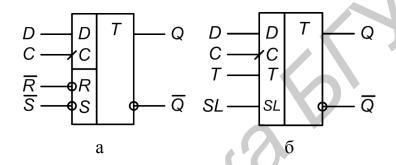

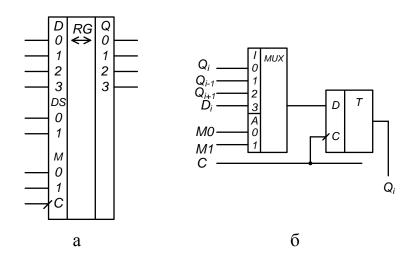

Совокупность входных сигналов автомата  $v = (x_n, ..., x_1)$  называется состоянием входа автомата, совокупность выходных сигналов автомата  $\lambda = (z_k, ..., z_1)$  – состоянием выхода автомата, а совокупность выходных сигналов  $\mu = (Q_m, ..., Q_1)$  элементов памяти – внутренним состоянием автомата.