Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

Кафедра электронно-вычислительных средств

# ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ

# Методическое пособие

по курсу «Основы проектирования ЭВС» для студентов специальности I-40 02 02 «Электронные вычислительные средства» дневной формы обучения

#### Рецензент:

доцент кафедры электронных вычислительных машин БГУИР, канд. техн. наук В.И. Жеребятьев

Авторы:

Г.В. Таранов, М.В. Качинский, В.Б. Клюс, А.Б. Давыдов

Проектирование цифровых устройств на интегральных микросхемах: Метод. пособие по курсу «Основы проектирования ЭВС» для студ. спец. I-40 02 02 «Электронные вычислительные средства» дневн. формы обуч. / Г.В. Таранов, М.В. Качинский, В.Б. Клюс, А.Б. Давыдов – Мн.: БГУИР, 2006. – 36 с.: ил.

ISBN 985-444-912-2.

Методическое пособие предназначено для проведения практических занятий ЭВС» «Основы проектирования для студентов специальности «Электронные вычислительные средства». Содержит примеры решения некоторых задач по проектированию комбинационных и последовательностных схем. Условия рассмотренных задач взяты из «Методического пособия по курсу «Проектирование цифровых устройств на ИМС» для студентов специальности «Проектирование И электронных технология вычислительных средств» М.В. Качинского, Г.В. Таранова под ред. И.М. Русака, вышедшего в БГУИР в 2001 г.

> УДК 004.31 (075.8) ББК 32.973-04 я 73

ISBN 985-444-912-2

© Коллектив авторов, 2006

© БГУИР, 2006

## СОДЕРЖАНИЕ

| Комбинационные Счётчики, регистр | е функциональные узлы, триггеры<br>ры |

|----------------------------------|---------------------------------------|

| итература                        |                                       |

|                                  |                                       |

|                                  |                                       |

#### **ВВЕДЕНИЕ**

В учебными I-40 02 02 соответствии планами специальности c«Электронные вычислительные средства» y студентов предусмотрены практические занятия и курсовое проектирование по дисциплине «Основы проектирования ЭВС». Условия многих задач и ссылки на литературу приведены в [1]. Учитывая отсутствие или недостаточное количество экземпляров литературных источников, в данном пособии приведены примеры решения задач по проектированию комбинационных и последовательностных схем ЭВС из условия минимального количества корпусов интегральных (ИМС). Примеры решения задач позволяют микросхем самостоятельно потренироваться в решении подобных задач [1] при подготовке к практическим занятиям и при выполнении курсового проекта по дисциплине «Основы проектирования ЭВС».

## 1. КОМБИНАЦИОННЫЕ ФУНКЦИОНАЛЬНЫЕ УЗЛЫ, ТРИГГЕРЫ

1.1. На базе одной ИМС КР1554ИД14 (два дешифратора 2-4 с инверсными выходами) и логических схем серии КР1554 построить полный двухступенчатый 4-разрядный дешифратор с инверсными выходами.

#### Решение.

т. д.

Инверсные выходы 4-разрядного дешифратора можно записать:

$$\begin{split} \overline{y}_i &= \overline{\widetilde{x}_3} \overline{\widetilde{x}_2} \overline{\widetilde{x}_1} \overline{\widetilde{x}_0} = \overline{\widetilde{x}_3} \overline{\widetilde{x}_2} + \overline{\widetilde{x}_1} \overline{\widetilde{x}_0} = \overline{g}_l + \overline{h}_p, \\ \text{где } \widetilde{x} &- \text{ это } x \text{ , либо } \overline{x} \text{ ; } \overline{g}_0 &= \overline{\overline{x}_3} \overline{x_2} \text{ , } \overline{g}_1 = \overline{\overline{x}_3} \overline{x_2} \text{ , } \overline{g}_2 = \overline{x_3} \overline{x_2} \text{ , } \overline{g}_3 = \overline{x_3} \overline{x_2} \text{ , } \overline{h}_0 = \overline{\overline{x}_1} \overline{\overline{x}_0} \end{split}$$

и

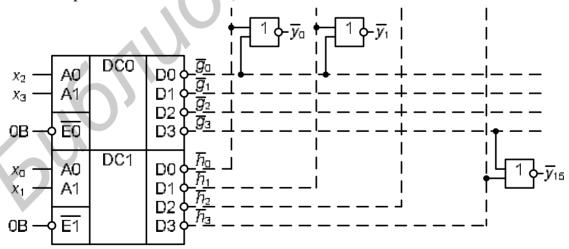

Функциональная схема 4-разрядного 2-ступенчатого дешифратора приведена на рис. 1.

Рис. 1. Функциональная схема 4-разрядного 2-ступенчатого дешифратора

1.2. Каскадным включением только сдвоенных дешифраторов/ демультиплексоров 2 на 4 КР1533ИД4 построить 4-разрядный полный двоичный дешифратор с инверсными выходами.

#### Решение.

Инверсные выходы 4-разрядного дешифратора получаем на выходах, стробируемых по входам  $\overline{C}$  2-разрядных дешифраторов с инверсными выходами в соответствии с выражением

$$\overline{y}_i = \overline{\overline{\overline{c}}_k \widetilde{x}_1 \widetilde{x}}_0 = \overline{\overline{\overline{g}}_k \widetilde{x}_1 \widetilde{x}_0} = \overline{\overline{\widetilde{x}_3 \widetilde{x}_2}} \overline{\widetilde{x}_1 \widetilde{x}_0} = \overline{\widetilde{x}_3 \widetilde{x}_2 \widetilde{x}_1 \widetilde{x}_0},$$

где  $\tilde{x}_i$  – это  $x_i$ , либо  $\bar{x}_i$ ;  $\bar{g}_k$  – инверсные выходы 2-разрядного дешифратора с информационными входами  $x_3$ ,  $x_2$ .

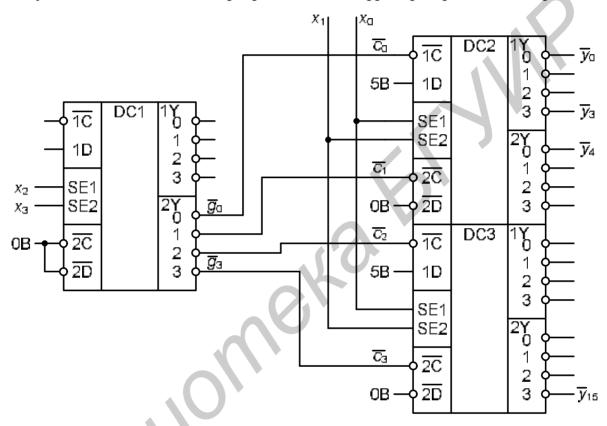

Функциональная схема 4-разрядного дешифратора приведена на рис. 2.

**Рис. 2.** Четырехразрядный полный двоичный дешифратор, построенный по каскадной схеме включения 2-разрядных дешифраторов

# 1.3. На базе ИМС КР1533ИД4 реализовать демультиплексор 1-16. Решение.

Демультиплексор (DMX) получим из схемы, приведенной на рис. 2, если вместо 0В на входы  $\overline{\text{2C}}$ ,  $\overline{\text{2D}}$  дешифратора DC1 подать информационный сигнал X, а входы  $x_3$ ,  $x_2$ ,  $x_1$ ,  $x_0$  использовать в качестве адресных входов DMX  $a_3$ ,  $a_2$ ,  $a_1$   $a_0$ . Получим DMX 1-16 с прямыми выходами  $y_i$ , т. е.  $y_i = X$ ,  $(i)_{10} = (a_3 a_2 a_1 a_0)_2$ .

1.4. На двух ИМС КР1533ИД4 и одном инверторе построить 4-разрядный двоичный дешифратор.

Решение.

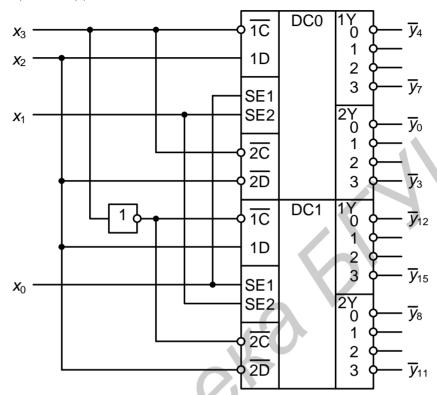

Осуществляя монтажные соединения  $1D-\overline{2D}$  и  $\overline{1C}-\overline{2C}$ , на рис. 3 получаем два 3-разрядных стробируемых дешифратора DC0, DC1. С помощью инвертора, выполняющего функцию одноразрядного дешифратора, старшим разрядом  $x_3$  4-разрядного кода  $x_3x_2x_1x_0$  разрешаем работу либо DC0, либо DC1 по стробирующим входам  $\overline{1C}-\overline{2C}$ .

**Рис. 3.** Четырехразрядный двоичный дешифратор на двух ИМС КР1533ИД4 и одном инверторе

1.5. На логических элементах серии KP1533 построить шифратор, преобразующий унитарный инверсный код с выхода KP1533ИД7 в прямой двоичный код.

#### Решение.

Работа шифратора описывается таблицей истинности (табл. 1).

#### Таблица 1

| $\overline{x}_7$ | $\bar{x}_6$ | $\overline{x}_5$ | $\overline{x}_4$ | $\overline{x}_3$ | $\overline{x}_2$ | $\overline{x}_1$ | $\overline{x}_0$ | $y_2$ | $y_1$ | $y_0$ |

|------------------|-------------|------------------|------------------|------------------|------------------|------------------|------------------|-------|-------|-------|

| 1                | $\sqrt{1}$  | 1                | 1                | 1                | 1                | 1                | 1                | 0     | 0     | 0     |

| 1                | 1           | 1                | 1                | 1                | 1                | 1                | 0                | 0     | 0     | 0     |

| 1                | 1           | 1                | 1                | 1                | 1                | 0                | 1                | 0     | 0     | 1     |

| 1                | 1           | 1                | 1                | 1                | 0                | 1                | 1                | 0     | 1     | 0     |

| 1                | 1           | 1                | 1                | 0                | 1                | 1                | 1                | 0     | 1     | 1     |

| 1                | 1           | 1                | 0                | 1                | 1                | 1                | 1                | 1     | 0     | 0     |

| 1                | 1           | 0                | 1                | 1                | 1                | 1                | 1                | 1     | 0     | 1     |

| 1                | 0           | 1                | 1                | 1                | 1                | 1                | 1                | 1     | 1     | 0     |

| 0                | 1           | 1                | 1                | 1                | 1                | 1                | 1                | 1     | 1     | 1     |

Из табл. 1 получаем логические выражения для выходов шифратора:

$$y_0 = \overline{\overline{x}_1} + \overline{\overline{x}_3} + \overline{\overline{x}_5} + \overline{\overline{x}_7} = \overline{\overline{\overline{x}_1} + \overline{\overline{x}_3} + \overline{\overline{x}_5} + \overline{\overline{x}_7}} = \overline{\overline{x}_1 \cdot \overline{x}_3 \cdot \overline{x}_5 \cdot \overline{x}_7},$$

$$y_1 = \overline{\overline{\overline{x}_2} + \overline{\overline{x}_3} + \overline{\overline{x}_6} + \overline{\overline{x}_7}} = \overline{\overline{x}_2 \cdot \overline{x}_3 \cdot \overline{x}_6 \cdot \overline{x}_7},$$

$$y_2 = \overline{\overline{\overline{x}_4} + \overline{\overline{x}_5} + \overline{\overline{x}_6} + \overline{\overline{x}_7}} = \overline{\overline{x}_4 \cdot \overline{x}_5 \cdot \overline{x}_6 \cdot \overline{x}_7}.$$

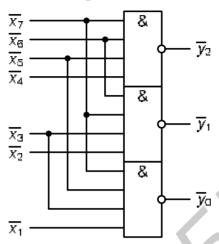

Схема шифратора приведена на рис. 4.

Рис. 4. Шифратор

1.6. На элементах серии КР1533 построить приоритетный шифратор. <u>Решение.</u>

Работа приоритетного шифратора описывается таблицей истинности (табл. 2).

| $x_7$ | $x_6$ | $x_5$ | $x_4$ | $x_3$ | $x_2$ | $x_1$ | $x_0$ | $y_2$ | $y_1$ | $y_0$ |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | X     | 0     | 0     | 1     |

| 0     | 0     | 0     | 0     | 0     | 1     | X     | X     | 0     | 1     | 0     |

| 0     | 0     | 0     | 0     | 1     | X     | X     | X     | 0     | 1     | 1     |

| 0     | 0     | 0     | 1     | X     | X     | X     | X     | 1     | 0     | 0     |

| 0     | 0     | 1     | X     | X     | X     | X     | X     | 1     | 0     | 1     |

| 0     | 1     | X     | X     | X     | X     | X     | X     | 1     | 1     | 0     |

| 1     | X     | X     | X     | X     | X     | X     | X     | 1     | 1     | 1     |

|       |       |       |       |       |       |       |       |       |       |       |

Таблица 2

Из табл. 2 можно записать:

$$\begin{aligned} y_2 &= x_7 + \overline{x}_7 x_6 + \overline{x}_7 \overline{x}_6 x_5 + \overline{x}_7 \overline{x}_6 \overline{x}_5 x_4, \\ y_1 &= x_7 + \overline{x}_7 x_6 + \overline{x}_7 \overline{x}_6 \overline{x}_5 \overline{x}_4 x_3 + \overline{x}_7 \overline{x}_6 \overline{x}_5 \overline{x}_4 \overline{x}_3 x_2, \\ y_0 &= x_7 + \overline{x}_7 \overline{x}_6 x_5 + \overline{x}_7 \overline{x}_6 \overline{x}_5 \overline{x}_4 x_3 + \overline{x}_7 \overline{x}_6 \overline{x}_5 \overline{x}_4 \overline{x}_3 \overline{x}_2 x_1. \end{aligned}$$

Повторным применением к каждой функции  $y_i$  соотношения алгебры логики  $a+F\overline{a}=a+F$  можно упростить  $y_i$  и преобразовать, например, для использования 2-входовых логических элементов И, ИЛИ:

$$y_2 = x_7 + x_6 + x_5 + x_4 = (x_7 + x_6) + (x_5 + x_4),$$

$$y_{1} = x_{7} + x_{6} + \overline{x}_{5}\overline{x}_{4}x_{2} + \overline{x}_{5}\overline{x}_{4}x_{3} = (x_{7} + x_{6}) + \overline{\overline{x}_{5}\overline{x}_{4}}(x_{2} + x_{3}) =$$

$$= (x_{7} + x_{6}) + \overline{(x_{5} + x_{4})}(x_{2} + x_{3}),$$

$$y_{0} = x_{7} + \overline{x}_{6}x_{5} + \overline{x}_{6}\overline{x}_{4}x_{3} + \overline{x}_{6}\overline{x}_{4}\overline{x}_{2}x_{1} = x_{7} + \overline{x}_{6}[x_{5} + \overline{x}_{4}(x_{3} + \overline{x}_{2}x_{1})].$$

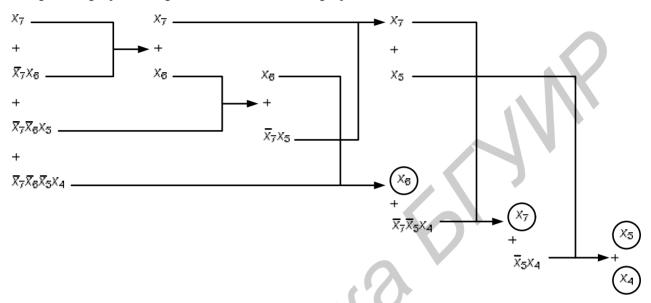

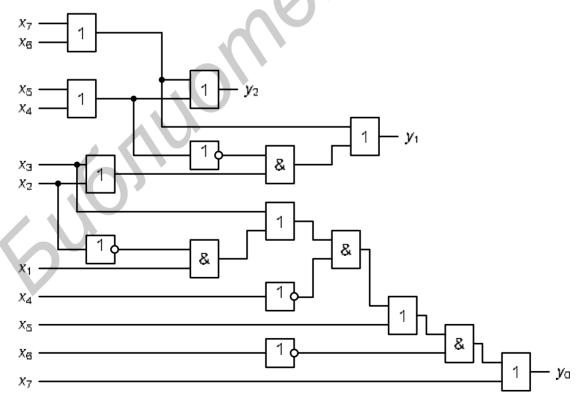

На рис. 5 показан пример упрощения функции  $y_2$ . Функциональная схема приоритетного кодера приведена на рис. 6 и может быть реализована на четырех корпусах серии КР1533 (два корпуса ЛЛ1, один ЛА3 и один ЛН1).

**Рис. 5.** Пример применения формулы  $a+F\overline{a}=a+F$  к  $y_2$

Рис. 6. Приоритетный шифратор

1.7. Реализовать с помощью дешифратора КР1533ИД7 и элемента И-НЕ булеву функцию

$$y = \overline{x}_1 \overline{x}_2 \overline{x}_3 + x_1 x_3 + x_2 x_3 + x_1 x_2$$

.

#### Решение.

Запишем СДНФ функции y, например, с помощью правила развёртывания, а также учитывая, что x + x = x, получим:

$$y = \overline{x}_{1}\overline{x}_{2}\overline{x}_{3} + x_{1}1x_{3} + 1x_{2}x_{3} + x_{1}x_{2}1 = \overline{x}_{1}\overline{x}_{2}\overline{x}_{3} + x_{1}(x_{2} + \overline{x}_{2})x_{3} + (x_{1} + \overline{x}_{1})x_{2}x_{3} + x_{1}x_{2}(x_{3} + \overline{x}_{3}) = \overline{\overline{x}_{1}}\overline{x}_{2}\overline{x}_{3} + x_{1}x_{2}x_{3} + x_{1}\overline{x}_{2}x_{3} + \overline{x}_{1}x_{2}x_{3} + \overline{x}_{1}x_{2}\overline{x}_{3} + x_{1}x_{2}\overline{x}_{3} = \overline{\overline{x}_{1}}\overline{x}_{2}\overline{x}_{3} \cdot \overline{x}_{1}x_{2}x_{3} \cdot \overline{x}_{1}x_{2}x_{3} \cdot \overline{x}_{1}x_{2}\overline{x}_{3} = \overline{\overline{y}_{0}}\overline{y}_{7}\overline{y}_{5}\overline{y}_{3}\overline{y}_{6},$$

где  $\bar{y}_i$  – выходы 3-разрядного дешифратора КР1533ИД7.

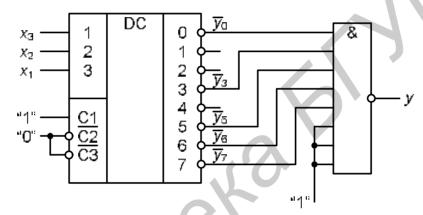

На рис. 7 приведена функциональная схема, реализующая функцию y.

**Рис. 7.** Комбинационная схема, реализующая функцию  $y = \overline{x_1} \overline{x_2} \overline{x_3} + x_1 x_3 + x_2 x_3 + x_1 x_2$

Функцию у можно получить и на выходе схемы И  $y=\overline{y}_1\overline{y}_2\overline{y}_4$ , либо  $y=\overline{\overline{y}_1}\overline{y}_2\overline{y}_4$ .

1.8. Построить преобразователь кода 2421 в код Грея на логических элементах серии КР1533.

#### Решение.

Работа преобразователя кода 2421 в код Грея описывается следующей таблицей истинности.

Таблица 3

| Код 2421       | Код Грея       | Код 2421       | Код Грея       |

|----------------|----------------|----------------|----------------|

| $x_3x_2x_1x_0$ | $y_3y_2y_1y_0$ | $x_3x_2x_1x_0$ | $y_3y_2y_1y_0$ |

| 0000           | 0000           | 1011           | 0111           |

| 0001           | 0001           | 1100           | 0101           |

| 0010           | 0011           | 1 1 0 1        | 0100           |

| 0011           | 0010           | 1110           | 1100           |

| 0100           | 0110           | 1111           | 1101           |

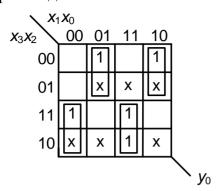

Нанесём функции  $y_i$  на карты Карно, добавив 6 крестов в избыточных наборах кода 2421.

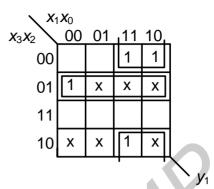

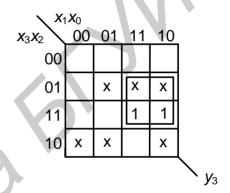

**Рис. 8.** Карта Карно  $y_0$

**Рис. 9.** Карта Карно  $y_1$

**Рис. 10.** Карта Карно  $y_2$

**Рис. 11.** Карта Карно  $y_3$

В соответствии с рис. 8 – 11 можем записать:

$$y_{0} = x_{3}\overline{x}_{1}\overline{x}_{0} + \overline{x}_{3}\overline{x}_{1}x_{0} + x_{3}x_{1}x_{0} + \overline{x}_{3}x_{1}\overline{x}_{0} = \overline{x}_{1}(x_{3} \oplus x_{0}) + x_{1}(\overline{x_{3} \oplus x_{0}}) = x_{1} \oplus x_{3} \oplus x_{0},$$

$$y_{1} = \overline{x}_{2}x_{1} + \overline{x}_{3}x_{2} = \overline{\overline{x}_{2}x_{1}} \cdot \overline{\overline{x}_{3}x_{2}}, \quad y_{2} = \overline{\overline{x}_{2} + x_{3}} = \overline{\overline{x}_{2}\overline{x}_{3}}, \quad y_{3} = x_{2}x_{1} = \overline{\overline{x}_{2}x_{1}}.$$

Таким образом, преобразователь кода 2421 в код Грея можно реализовать на двух корпусах КР1533ЛА3 и одном корпусе КР1533ЛП5 (рис. 12).

Рис. 12. Преобразователь кода 2421 в код Грея

1.9. Разработать приоритетный шифратор с инверсными входами и выходами 16-4 на двух ИМС 555ИВ1 и логических элементах той же серии.

#### Решение.

Функционирование приоритетного шифратора PRCD 8-3 555ИВ1 описывается таблицей истинности (табл. 4).

Таблица 4

| ΕĪ | $\overline{7}$ $\overline{6}$ $\overline{5}$ $\overline{4}$ $\overline{3}$ $\overline{2}$ $\overline{1}$ $\overline{0}$ | GS | $\overline{\mathbf{A}}_{2}  \overline{\mathbf{A}}_{1}  \overline{\mathbf{A}}_{0}$ | EO |

|----|-------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------|----|

| Н  | XXXXXXXX                                                                                                                | Н  | ННН                                                                               | Н  |

| L  | ННННННН                                                                                                                 | Н  | ннн                                                                               | L  |

| L  | HHHHHHHL                                                                                                                | L  | ннн                                                                               | Н  |

| L  | HHHHHHLX                                                                                                                | L  | HHL                                                                               | Н  |

| L  | HHHHHLXX                                                                                                                | L  | HLH                                                                               | Н  |

| L  | HHHHLXXX                                                                                                                | L  | HLL                                                                               | Н  |

| L  | HHHLXXXX                                                                                                                | L  | LHH                                                                               | Н  |

| L  | HHLXXXXX                                                                                                                | L  | LHL                                                                               | Н  |

| L  | HLXXXXXX                                                                                                                | L  | LLH                                                                               | Н  |

| L  | LXXXXXXX                                                                                                                | L  | LLL                                                                               | Н  |

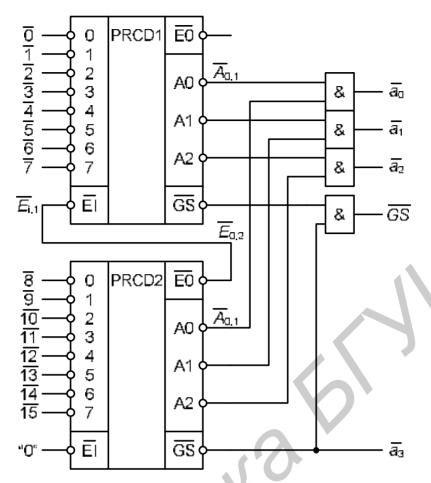

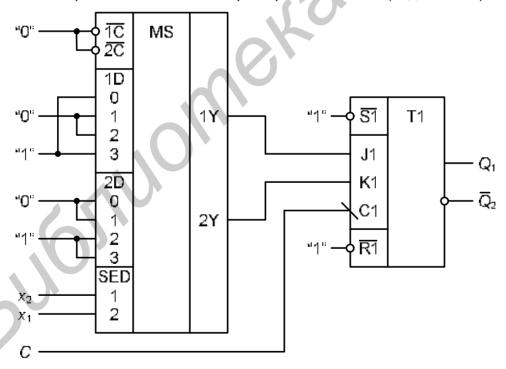

Так как шифратор 16-4 должен быть приоритетным, то ИМС 555ИВ1 (PRCD2) старших входов  $\overline{8}-\overline{15}$  должна "отключать" микросхему PRCD1 младших входов  $\overline{0}-\overline{7}$  по цепи  $\overline{EO}-\overline{EI}$ . Числа 0–7 и 8–15 совпадают соответственно в трёх младших разрядах двоичного кода. Если обозначить выходные сигналы PRCD 16–4  $a_3a_2a_1a_0$ , выходы ИМС PRCD1 младших входов —  $A_{2.1}$ ,  $A_{1.1}$ ,  $A_{0.1}$ , а старших —  $A_{2.2}$ ,  $A_{1.2}$ ,  $A_{0.2}$ , то должно выполняться условие  $a_i=A_{i.1}+A_{i.2}$ , где i=0–2. Так как выходы 555ИВ1 инверсные и выходы  $a_i$  должны быть инверсными по условию задачи, то можно записать  $\overline{a}_i=\overline{A_{i,1}+A_{i,2}}=\overline{A_{i,1}}\overline{A_{i,2}}$ . Старший разряд  $\overline{a}_3$  можно взять с выхода сигнала  $\overline{GS}$  PRCD2. Функциональная схема PRCD 16-4 показана на рис. 13.

1.10. Реализовать на базе одной ИМС КР1533КП2 и логических элементах той же серии мультиплексор 8-1 по параллельной схеме наращивания каналов.

#### Решение.

Микросхема КР1533КП2 представляет собой сдвоенный селектормультиплексор 4-1. Таблица истинности КР1533КП2 с информационными входами D0-D3 приведена в табл. 5.

Таблица 5

| ]    | Выход |                |    |

|------|-------|----------------|----|

| SED2 | SED1  | $\overline{C}$ | Y  |

| X    | X     | 1              | 0  |

| 0    | 0     | 0              | D0 |

| 0    | 1     | 0              | D1 |

| 1    | 0     | 0              | D2 |

| 1    | 1     | 0              | D3 |

Рис. 13. Функциональная схема PRCD 16-4

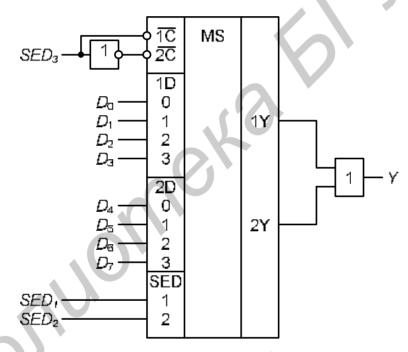

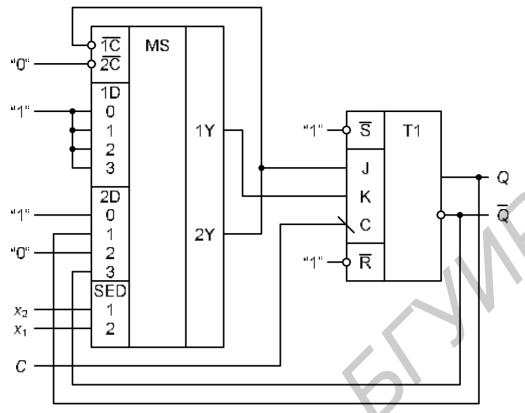

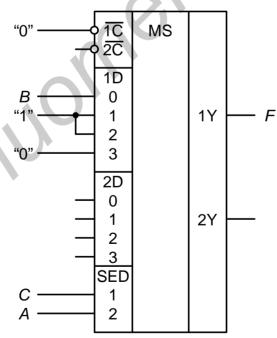

Параллельная схема предполагает наличие нескольких MUX, управление которыми осуществляется по стробирующим входам  $\overline{C}$  с выхода дешифратора старших разрядов выбора данных. Прямые выходы мультиплексоров 1Y и 2Y через схему ИЛИ передаются на выход Y MUX 8-1. Для построения MUX 8-1 из MUX 4-1 достаточно иметь два MUX 4-1 (8 : 4 = 2) или один сдвоенный MUX 4-1. В качестве дешифратора старшего разряда выбора данных *SED*3 может служить одноразрядный дешифратор на одном инверторе.

Функциональная схема MUX 8-1 приведена на рис. 14.

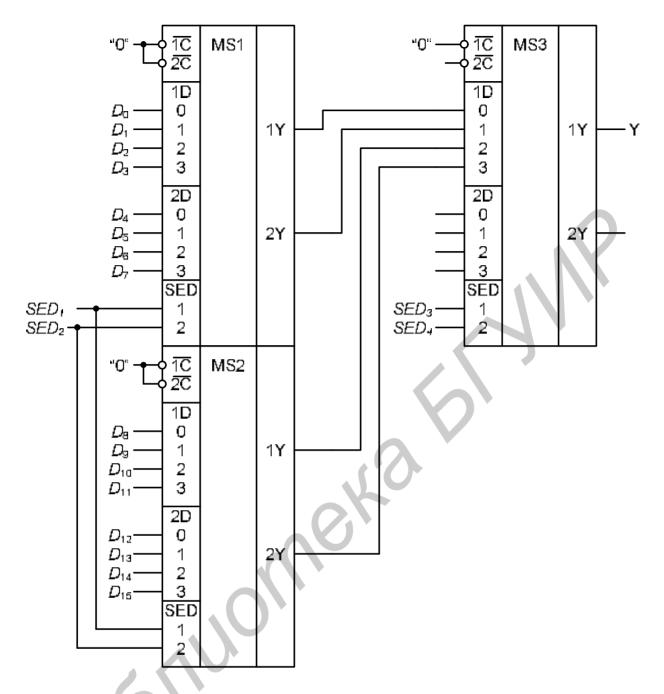

1.11. Каскадным соединением только (без дополнительных элементов) ИМС КР1533КП2 (табл. 5) построить MUX 16-1.

#### Решение.

При каскадном соединении выбор одного из выходов мультиплексоровселекторов MS1, MS2 осуществляется старшим мультиплексором-селектором MS3 (рис. 15), управляемым старшими разрядами выбора данных SED4, SED3. На выход Y проходят с входов данные  $D_i$ , где

$$(i)_{10} = (SED4 SED3 SED2 SED1)_2$$

.

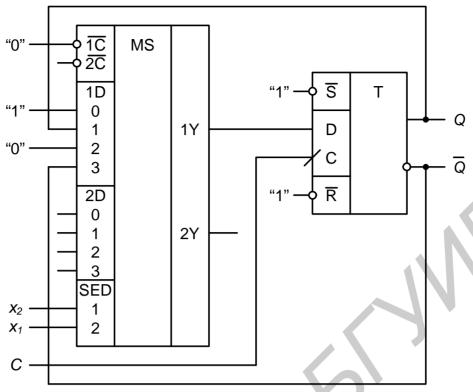

1.12. Реализовать на мультиплексоре-селекторе КР1533КП2 и D-триггере КР1533ТМ2 триггер, имеющий два информационных входа  $x_1$ ,  $x_2$  и функционирующий в соответствии с таблицей переключения (табл. 6).

Таблица 6

| $x_1$ | $x_2$ | $Q_{n+1}$        |

|-------|-------|------------------|

| 0     | 0     | 1                |

| 0     | 1     | $Q_n$            |

| 1     | 0     | 0                |

| 1     | 1     | $\overline{Q}_n$ |

#### Решение.

Так как уравнение D-триггера  $Q_{n+1} = D_n$ , то, подключив выход мультиплексора к информационному входу D-триггера и подавая  $x_1$ ,  $x_2$  на входы выбора данных мультиплексора (рис. 16), будем выбирать один из информационных входов мультиплексора, подавая на него соответствующее значение  $Q_{n+1}$  из табл. 6.

Рис. 14. Мультиплексор 8-1 на базе КР1533КП2

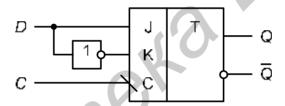

1.13. На ИМС КР1533КП2 и ЈК-триггере КР1533ТВ9 реализовать триггер, заданный табл. 6.

#### Решение.

Первый вариант. Из JK-триггера делаем D-триггер по схеме рис. 17, при этом выход инвертора получаем на свободном выходе 2Y мультиплексора КР1533КП2 (рис. 18).

Второй вариант. Составляем по сокращённой табл. 6 полную таблицу переключения (табл. 7) искомого триггера.

**Рис. 15.** Мультиплексор 16-1, построенный по каскадной схеме из мультиплексоров 4-1

## Таблица 7

| $x_1$ | $x_2$ | $Q_n$ | $Q_{n+1}$ | JK  |

|-------|-------|-------|-----------|-----|

| 0     | 0     | 0     | 1         | 1 x |

| 0     | 0     | 1     | 1         | x 0 |

| 0     | 1     | 0     | 0         | 0 x |

| 0     | 1     | 1     | 1         | x 0 |

| 1     | 0     | 0     | 0         | 0 x |

| 1     | 0     | 1     | 0         | x 1 |

| 1     | 1     | 0     | 1         | 1 x |

| 1     | 1     | 1     | 0         | x 1 |

Рис. 16. Триггер, функционирующий в соответствии с табл. 6 (задача 1.12)

Рис. 17. D-триггер на базе ЈК-триггера

Столбцы J и K табл. 7 заполним с помощью управляющей таблицы JК-тригера (табл. 8).

| Таблица 8 |  |

|-----------|--|

|-----------|--|

| $Q_n$ – | $\rightarrow Q_{n+1}$ | JK  |

|---------|-----------------------|-----|

| 0       | 0                     | 0 x |

| 0       | 1                     | 1 x |

| 1       | 0                     | x 1 |

| 1       | 1                     | x 0 |

Подавая выход 1Y мультиплексора на вход J, а 2Y на вход K, получим схему (рис. 19). Можно вместо табл. 7 и 8 привести сокращённую табл. 9 переключения JK-триггера.

Таблица 9

| J K | $Q_{n+1}$        |

|-----|------------------|

| 0 0 | $Q_n$            |

| 0 1 | 0                |

| 1 0 | 1                |

| 1 1 | $\overline{Q_n}$ |

**Рис. 18.** Триггер, функционирующий в соответствии с табл. 6 и построенный на базе JK-триггера КР1533ТВ9 (задача 1.13)

**Рис. 19.** Второй вариант реализации триггера, функционирующего в соответствии с табл.6 и построенного на базе JK-триггера КР1533ТВ9 (задача 1.13)

Теперь сопоставим табл. 6 и табл. 9. Например, при  $x_1 = x_2 = 0$  (выбираются входы мультиплексора 1D0 и 2D0 на рис. 19)  $Q_{n+1} = 1$ , что в табл. 9 соответствует J = 1, K = 0. Следовательно, на рис. 19 необходимо подать 1D0 = 1, 2D0 = 0 и т. д.

1.14. Построить только на одной микросхеме КР1533КП2 комбинационный узел, таблица истинности которого представлена табл. 10.

| Ta | ส | п  | и |   | 2 | 1 | n |

|----|---|----|---|---|---|---|---|

| ıa | u | JI | И | ш | a |   | u |

| A | В | C | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

#### Решение.

Мультиплексор имеет два адресных входа (входы выбора данных SED1, SED2), а необходимо реализовать булеву функцию трёх переменных. В этом случае иногда может потребоваться дополнительный инвертор. Чтобы это определить, нанесём функцию F на карту Карно. После минимизации получим  $F = A\overline{B} + \overline{A}C + B\overline{C}$ .

В этом выражении все переменные встречаются в инверсном виде, поэтому потребуется дополнительно инвертор, выход которого получим на втором выходе мультиплексора-селектора.

Разобьём табл. 10 по две строки. Если подать A на SED2, B на SED1 и сравнить C с F, то легко определить, что нужно подавать на входы данных (рис. 20).

Рис. 20. Реализация булевой функции F, заданной таблицей истинности 10

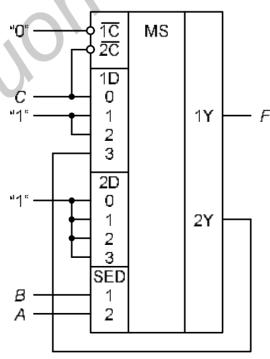

1.15. Построить только на одной микросхеме КР1533КП2 функциональный узел, выполняющий булеву функцию, заданную табл. 11.

Таблица 11

|   |   |   | I = |

|---|---|---|-----|

| A | В | C | F   |

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 1   |

| 0 | 1 | 0 | 1   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 0   |

Таблица 12

| $\overline{A}$ | $\overline{C}$ | В | F |

|----------------|----------------|---|---|

|                |                |   |   |

| 0              | 0              | 0 | 0 |

| 0              | 0              | 1 | 1 |

| 0              | 1              | 0 | 1 |

| 0              | 1              | 1 | 1 |

| 1              | 0              | 0 | 1 |

| 1              | 0              | 1 | 1 |

| 1              | 1              | 0 | 0 |

| 1              | 1              | 1 | 0 |

#### Решение.

Если нанести на карту Карно булеву функцию F, то после минимизации получим  $F = \overline{A}C + B\overline{C} + A\overline{C}$ .

Из этой функции следует, что переменная В встречается без инверсии. Поэтому в качестве адресных входов мультиплексора выбираем A, C, которые встречаются с инверсией. Табл. 11 можем представить для удобства в виде табл. 12. Разобьём табл. 12 по две строки, подадим A на SED2, C на SED1 и сравнивая B и F определим, что нужно подавать на входы данных мультиплексора (рис. 21).

**Рис. 21.** Реализация булевой функции F, заданной табл. 12

Можно не составлять табл. 12, а в выражение функции подставлять адресные наборы AC и определять  $D_i$ . Например, подставим A=C=0. Тогда  $D_0 = \overline{0}0 + B\overline{0} + 0\overline{0} = B$  и т. д.

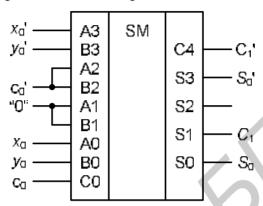

1.16. На 4-разрядном сумматоре К555ИМ6 реализовать два одноразрядных сумматора. Входы первого сумматора  $x_0, y_0, c_0$ , выходы  $S_0, C_1$ , для второго сумматора  $-x_0', y_0', c_0'$  и  $S_0', C_1'$ .

#### Решение.

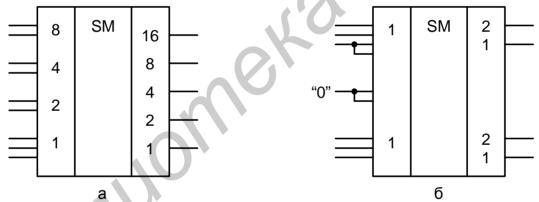

Схема приведена на рис. 22. Учитывая, что в двоичной системе вес i-го разряда в два раза меньше (i+1)-го, то  $c_0$ ' подаётся на два разряда  $A_2$  и  $B_2$ , или можно подать  $A_2=1$ ,  $B_2=c_0$ '. С учётом весов разрядов 4-разрядный и два одноразрядных сумматора показаны на рис. 23 а,б.

Рис. 22. Реализация двух одноразрядных сумматоров на одном 4-разрядном

**Рис. 23.** Условное графическое обозначение (с учётом весов разрядов) 4-разрядного сумматора (а) и двух одноразрядных сумматоров на базе одного 4-разрядного (б)

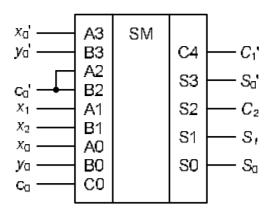

1.17. На 4-разрядном сумматоре К555ИМ6 реализовать одноразрядный сумматор (с входами  $x_0$ ',  $y_0$ ',  $c_0$ ' и выходами  $S_0$ ',  $C_1$ ') и 2-разрядный сумматор (с входами  $x_0$ ,  $x_1$ ,  $y_0$ ,  $y_1$ ,  $c_0$  и выходами  $S_0$ ,  $S_1$ ,  $C_2$ ).

#### Решение.

Схема приведена на рис. 24. Наличие  $c_0$ '=1 не изменяет состояния  $S_2$ = $C_2$ , т.к.  $S_2=A_2\oplus B_2\oplus C_2=1\oplus 1\oplus C_2=C_2$ .

1.18. Используя решение предыдущих задач, построить пороговую схему 9-разрядного (n=9) двоичного кода  $x_8, x_7, ..., x_0$  с порогом k=6 на трёх ИМС К555ИМ6.

**Рис. 24.** 4-разрядный сумматор в качестве двух сумматоров: одноразрядного с входами  $x_0$ ',  $y_0$ ',  $c_0$ ' и выходами  $S_0$ ',  $C_1$ ' и 2-разрядного с входами  $x_0$ ,  $x_1$ ,  $y_0$ ,  $y_1$ ,  $c_0$  и выходами  $S_0$ ,  $S_1$ ,  $C_2$

#### Решение.

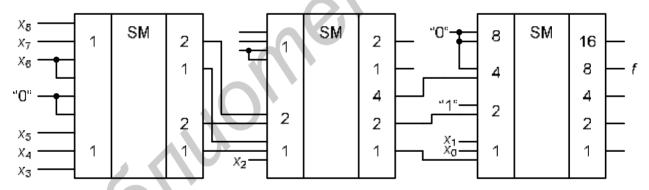

Все разрядные коэффициенты 9-разрядного кода суммируются с весом  $2^0$  = 1 и могут подаваться в любом порядке на входы сумматоров с весом 1. Результат суммирования на одном сумматоре должен передаваться со своими весами на соответствующие входы следующего сумматора. Для организации выхода f порогового элемента можно использовать выход 4-разрядного сумматора с весом 8, добавив 8 - k = 8 - 6 = 2 константой на вход сумматора с весом 2 или можно использовать выход с весом 16, добавив 16 - 6 = 10 = 8 + 2 в виде констант на входы сумматора с весами 8 и 2. Схема приведена на рис. 25.

**Рис. 25.** Функциональная схема порогового элемента 9-разрядного (n = 9) двоичного кода  $x_8, x_7, ..., x_0$  с порогом k = 6 на трёх ИМС К555ИМ6

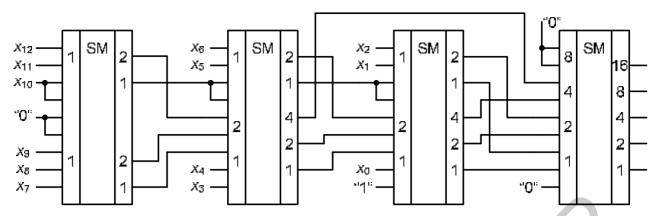

1.19. Построить мажоритарный элемент для 13-разрядного двоичного кода  $x_{12},...,x_0$  (n=13) на четырёх сумматорах К555ИМ6.

#### Решение.

Используя решение предыдущих задач, а также учитывая, что для мажоритарного элемента порог k=(n+1)/2=(13+1)/2=7, на рис. 26 приведена функциональная схема мажоритарного элемента. Его выход f организован на выходе сумматора с весом 8 после добавления константы 8-k=8-7=1 на вход сумматора с весом 1.

**Рис. 26.** Мажоритарный элемент 13-разрядного двоичного кода  $x_{12},...,x_0$  (n=13) на четырёх сумматорах К555ИМ6

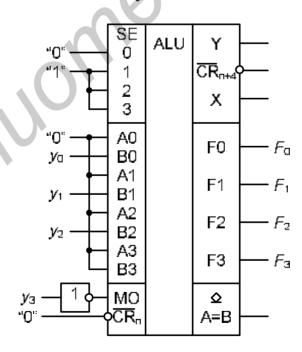

1.20. Разработать преобразователь 4-разрядного прямого кода целого числа  $y_3.y_2y_1y_0$  ( $y_3$  — разряд знака) в дополнительный  $F_3.F_2F_1F_0$  ( $F_3$  — знаковый разряд) на КР1533ИПЗ и инверторе.

#### Решение.

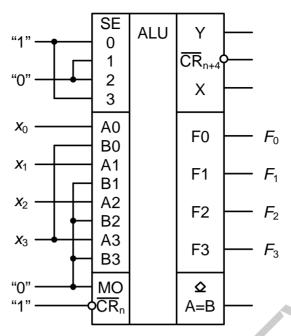

Схема преобразователя приведена на рис. 27. По входам SE выбрана четырнадцатая операция 1110. При  $y_3=0$  (MO = 1) выполняется поразрядная логическая операция  $A \lor B = (0 \lor 0).(0 \lor y_2)(0 \lor y_1)(0 \lor y_0) = 0.y_2y_1y_0 = y_3.y_2y_1y_0$ . При  $y_3=1$  (MO = 0) и  $\overline{CR}_n=0$  выполняется арифметическая операция  $A \lor \overline{B} + A + 1 = 0 \lor \overline{B} + 0 + 1 = (0 \lor \overline{0})(0 \lor \overline{y}_2)(0 \lor \overline{y}_1)(0 \lor \overline{y}_0) + 1 = 1.\overline{y}_2\overline{y}_1\overline{y}_0 + 1 = y_3.y_2y_1y_0 + 1$ , т.е. на выходах Fi получаем дополнительный код.

**Рис. 27.** Преобразователь 4-разрядного прямого кода в дополнительный на КР1533ИПЗ и инверторе

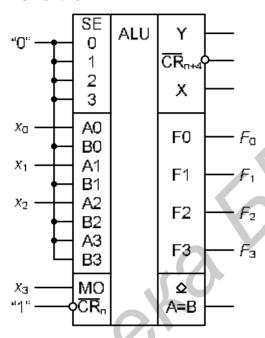

1.21. Разработать преобразователь 4-разрядного прямого кода целого числа  $x_3.x_2x_1x_0$  в обратный  $F_3.F_2F_1F_0$  ( $x_3$  и  $x_3$  – знаковые разряды).

#### Решение.

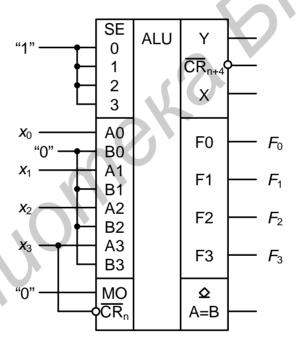

Схема преобразователя приведена на рис. 28. По входам SE выбрана нулевая операция 0000. При  $x_3=\mathrm{MO}=0$ ,  $\overline{\mathrm{CR}}_{\mathrm{n}}=1$  выбирается арифметическая операция  $A=0.x_2x_1x_0=x_3.x_2x_1x_0$ , а при  $x_3=\mathrm{MO}=1$  выполняется операция  $\overline{A}=\overline{0}.\overline{x}_2\overline{x}_1\overline{x}_0=1.\overline{x}_2\overline{x}_1\overline{x}_0=x_3.\overline{x}_2\overline{x}_1\overline{x}_0$ , т.е. на выходах Fi получаем обратный код.

Рис. 28. Преобразователь 4-разрядного прямого кода в обратный на КР1533ИП3

1.22. Разработать преобразователь 4-разрядного обратного кода целого числа  $x_3.x_2x_1x_0$  в дополнительный  $F_3.F_2F_1F_0$  ( $x_3$  и  $F_3$  – знаковые разряды).

#### Решение.

Схема преобразователя приведена на рис. 29. По входам SE выбрана девятая операция 1001, по входу MO — арифметическая,  $\overline{CR}_n = 1$  — без переноса. В результате выполняется операция  $A + B = X + 000x_3$ . При  $x_3 = 0$  результат операции равен X, а при  $x_3 = 1 - X + 1$ , что соответствует переходу от обратного кода к дополнительному.

1.23. Разработать преобразователь 4-разрядного дополнительного кода целого числа  $x_3.x_2x_1x_0$  в обратный  $F_3.F_2F_1F_0$  ( $x_3$  и  $x_3$  – знаковые разряды).

#### Решение.

Схема преобразователя приведена на рис. 30. Выполняется постоянно пятнадцатая арифметическая операция (SE=1111, MO=0). Если число X положительное ( $x_3=0$ ), то выполняется функция A=X, если число X отрицательное, то A-1=X-1 что соответствует переходу от дополнительного кода к обратному.

**Рис. 29.** Преобразователь 4-разрядного обратного кода в дополнительный на КР1533ИП3

**Рис. 30.** Преобразователь 4-разрядного дополнительного кода в обратный на КР1533ИП3

# 2. СЧЁТЧИКИ И РЕГИСТРЫ

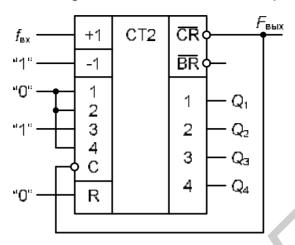

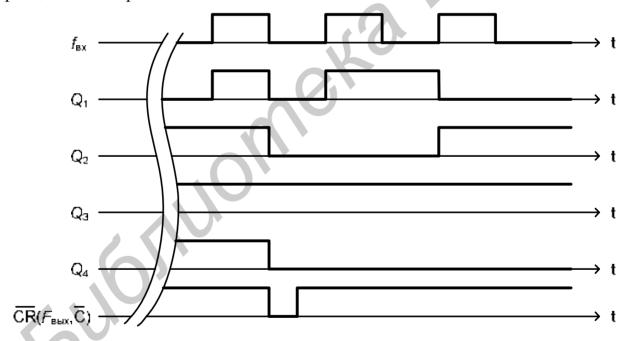

2.1. Привести схему, реализующую на счётчике КР1533ИЕ7 модуль счёта  $k=11\,$  в режиме суммирования. Нарисовать несколько тактов временной диаграммы до и после момента параллельного занесения информации.

#### Решение.

Модуль счёта k в режиме суммирования определяется по формуле  $k=2^n-1-D$  ,

откуда определим число D для параллельного занесения информации:

$$D = 2^n - 1 - k = 2^4 - 1 - 11 = 4_{10} = 0100_2$$

.

Схема счётчика с модулем k=11 приведена на рис. 31. Выходная частота следования импульсов  $F_{\textit{вых}}$  в k раз меньше, чем входная  $f_{\textit{ex}}$ .

**Рис. 31.** Счётчик с модулем счёта k = 11 на КР1533ИЕ7 в режиме суммирования

На рис. 32 приведен фрагмент временной диаграммы работы схемы, приведенной на рис. 31.

Рис. 32. Фрагмент временной диаграммы работы схемы, приведенной на рис. 31

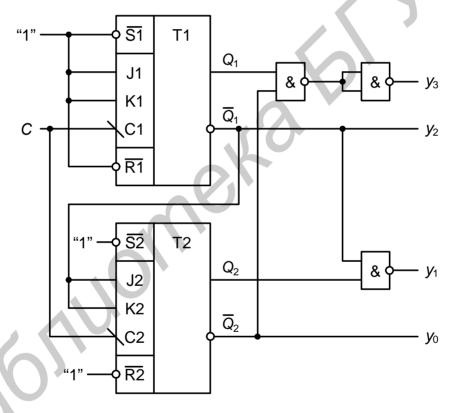

2.2. На одной ИМС КР1533ТВ9 и логических элементах той же серии построить генератор чисел 7-2-4-11.

#### Решение.

Для построения генератора нужна последовательностная схема на 4 состояния (два триггера), к выходам которой подключается выходная логика, имеющая четыре выхода  $y_3y_2y_1y_0$ , так как для кодирования числа 11

необходимо четыре двоичных разряда. Четыре состояния можно получить в схеме регистра сдвига, суммирующего счётчика, вычитающего счётчика или пересчётного устройства, обеспечивающего любую заданную последовательность состояний. Выберем схему вычитающего двухразрядного счётчика. Выходы  $y_i$  определим из табл. 13.

|       |       | гаолица 13 |       |       |       |  |

|-------|-------|------------|-------|-------|-------|--|

| $Q_2$ | $Q_1$ | $y_3$      | $y_2$ | $y_1$ | $y_0$ |  |

| 0     | 0     | 0          | 1     | 1     | 1     |  |

| 1     | 1     | 0          | 0     | 1     | 0     |  |

| 1     | 0     | 0          | 1     | 0     | 0     |  |

| 0     | 1     | 1          | 0     | 1     | 1     |  |

$$y_{3} = \overline{Q}_{2}Q_{1} = \overline{\overline{Q}_{2}}\overline{Q_{1}};$$

$$y_{2} = \overline{Q_{1}};$$

$$y_{1} = \overline{Q_{2}}\overline{\overline{Q_{1}}};$$

$$y_{0} = \overline{Q_{2}}.$$

Функциональная схема генератора чисел приведена на рис. 33. Схема построена на одной ИМС КР1533ТВ9 и одной ИМС КР1533ЛА3.

**Рис. 33.** Генератор чисел 7 – 2 – 4 – 11 на двух JK-триггерах ИМС КР1533ТВ9 и логических элементах

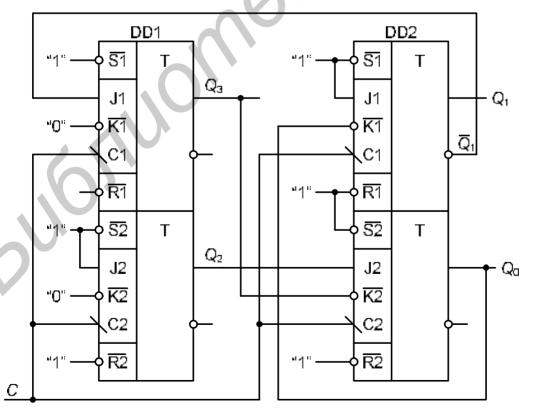

2.3. На выходах четырех ЈК-триггеров (две ИМС КР1533ТВ15) и логических элементах этой же серии построить генератор чисел 7-2-4-11. Построить полный граф шестнадцати ( $2^4$ ) состояний.

#### Решение.

Составим таблицу переходов (табл. 14) генератора чисел. С помощью управляющей табл. 15  $J\overline{K}$  -триггера заполним столбцы  $J_i$ ,  $\overline{K_i}$  табл. 14.

Таблица 14

| $Q_3$ | $Q_2$ | $Q_{\scriptscriptstyle 1}$ | $Q_0$ | $J_3$ | $\overline{K}_3$ | $oldsymbol{J}_2$ | $\overline{K}_2$ | $oldsymbol{J}_1$ | $\overline{K}_1$ | $oldsymbol{J}_0$ | $ar{K}_0$ |

|-------|-------|----------------------------|-------|-------|------------------|------------------|------------------|------------------|------------------|------------------|-----------|

| 0     | 1     | 1                          | 1     | 0     | ×                | ×                | 0                | ×                | 1                | ×                | 0         |

| 0     | 0     | 1                          | 0     | 0     | ×                | 1                | ×                | ×                | 0                | 0                | ×         |

| 0     | 1     | 0                          | 0     | 1     | ×                | ×                | 0                | 1                | ×                | 1                | ×         |

| 1     | 0     | 1                          | 1     | ×     | 0                | 1                | ×                | ×                | 1                | ×                | 1         |

Таблица 15

| $Q^{t}$ - | $\rightarrow Q^{t+1}$ | J | $\bar{K}$ |

|-----------|-----------------------|---|-----------|

| 0         | 0                     | 0 | ×         |

| 0         | 1                     | 1 | ×         |

| 1         | 0                     | × | 0         |

| 1         | 1                     | × | 1         |

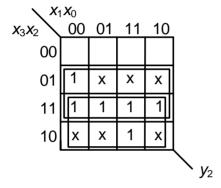

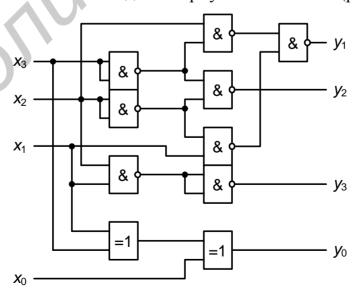

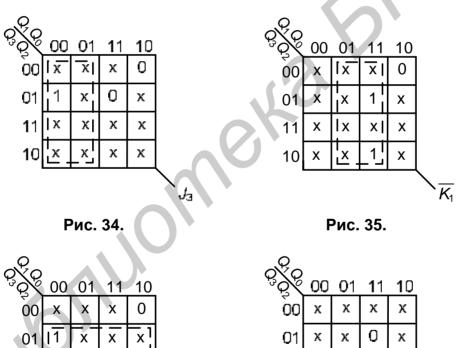

Составляем карты Карно для  $J_i$  и  $\overline{K}_i$ , в избыточных состояниях ставим кресты.

Рис. 36.

Рис. 37.

По картам Карно составляем логические выражения для  $J_i$  и  $\overline{K}_i$   $J_3=\overline{Q}_1,\ J_2=1,\ J_1=1,\ J_0=Q_2,\ \overline{K}_3=0,\ \overline{K}_2=0,\ \overline{K}_1=Q_0,\ \overline{K}_0=Q_3.$

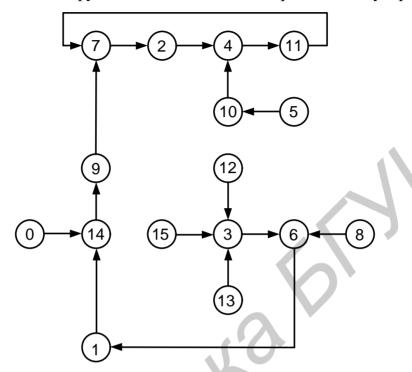

Для построения графа состояний выпишем 16-4=12 избыточных состояний (табл. 16), по уравнениям  $J_i$ ,  $\overline{K}_i$  заполним значения  $J_i$ ,  $\overline{K}_i$ , а по табл. 17 переключения  $J\overline{K}$  -триггера определим следующие состояния в момент времени t+1.

Таблица 16

|          |       |       |       |       |                    | t           |                  |                  |                  |                  |                  |             |       |       | <i>t</i> +1 |       |          |

|----------|-------|-------|-------|-------|--------------------|-------------|------------------|------------------|------------------|------------------|------------------|-------------|-------|-------|-------------|-------|----------|

| $Q_{10}$ | $Q_3$ | $Q_2$ | $Q_1$ | $Q_0$ | $\boldsymbol{J}_3$ | $\bar{K}_3$ | $oldsymbol{J}_2$ | $\overline{K}_2$ | $oldsymbol{J}_1$ | $\overline{K}_1$ | $oldsymbol{J}_0$ | $\bar{K}_0$ | $Q_3$ | $Q_2$ | $Q_1$       | $Q_0$ | $Q_{10}$ |

| 0        | 0     | 0     | 0     | 0     | 1                  | 0           | 1                | 0                | 1                | 0                | 0                | 0           | 1     | 1     | 1           | 0     | 14       |

| 1        | 0     | 0     | 0     | 1     | 1                  | 0           | 1                | 0                | 1                | 1                | 0                | 0           | 1     | 1     | 1           | 0     | 14       |

| 3        | 0     | 0     | 1     | 1     | 0                  | 0           | 1                | 0                | 1                | 1                | 0                | 0           | 0     | 1     | 1           | 0     | 6        |

| 5        | 0     | 1     | 0     | 1     | 1                  | 0           | 1                | 0                | 1                | 1                | 1                | 0           | 1     | 0     | 1           | 0     | 10       |

| 6        | 0     | 1     | 1     | 0     | 0                  | 0           | 1                | 0                | 1                | 0                | 1                | 1           | 0     | 0     | 0           | 1     | 1        |

| 8        | 1     | 0     | 0     | 0     | 1                  | 0           | 1                | 0                | 1                | 0                | 0                | 1           | 0     | 1     | 1           | 0     | 6        |

| 9        | 1     | 0     | 0     | 1     | 1                  | 0           | 1                | 0                | 1                | 1                | 0                | 1           | 0     | 1     | 1           | 1     | 7        |

| 10       | 1     | 0     | 1     | 0     | 0                  | 0           | 1                | 0                | 1                | 0                | 0                | 1           | 0     | 1     | 0           | 0     | 4        |

| 12       | 1     | 1     | 0     | 0     | 1                  | 0           | 1                | 0                | 1                | 0                | 1                | 1           | 0     | 0     | 1           | 1     | 3        |

| 13       | 1     | 1     | 0     | 1     | 1                  | 0           | 1                | 0                | 1                | 1                | 1                | 1           | 0     | 0     | 1           | 1     | 3        |

| 14       | 1     | 1     | 1     | 0     | 0                  | 0           | 1                | 0                | 1                | 0                | 1                | 1           | 1     | 0     | 0           | 1     | 9        |

| 15       | 1     | 1     | 1     | 1     | 0                  | 0           | 1                | 0                | 1                | 1                | 1                | 1           | 0     | 0     | 1           | 1     | 3        |

Таблица 17

| $\overline{J}$ | $\bar{K}$ | $Q_{n+1}$                      |

|----------------|-----------|--------------------------------|

| 0              | 0         | 0                              |

| 0              | 1         | $Q_n$                          |

| 1              | 0         | $ar{Q}_{\scriptscriptstyle n}$ |

| 1              | 1         | 1                              |

Граф состояний показан на рис. 38. Из графа следует, что схема не имеет тупиковых состояний и при любом сбое из любого избыточного состояния в конечном счёте вернётся к генерации состояний 7-2-4-11. Функциональная схема генератора приведена на рис. 39.

Возможно объединение  $J_i$  с  $\overline{K}_i$  и использование  $J\overline{K}$  -триггера как D-триггера с определением  $D_i$ , однако в этом случае потребуется дополнительная логика.

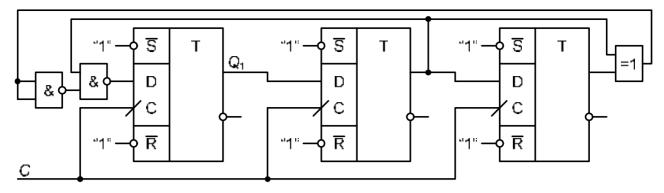

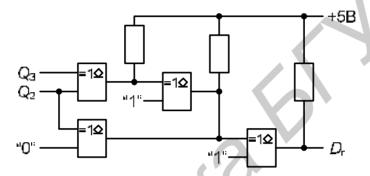

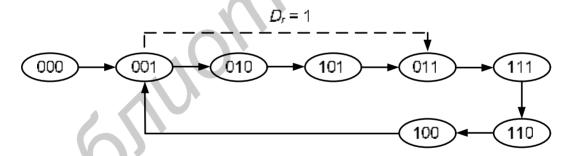

2.4. В 3-разрядный (на КР1533ТМ2) регистр  $Q_3Q_2Q_1$  последовательности максимальной длины ПМД с обратной связью  $D_r = Q_3 \oplus Q_2$  добавить логику на элементах той же серии для получения модуля счета k=5 методом скачка (скачок из  $a_1=001$ ,  $D_r=1$ ) и обеспечить также выход из нулевого состояния.

#### Решение.

Булеву функцию  $D_{r}$  обратной связи с учетом выхода из нуля можно записать в виде

$$\begin{split} D_{r} &= Q_{2} \oplus Q_{3} + \overline{Q_{3}} \cdot \overline{Q_{2}} Q_{1} + \overline{Q_{3}} \cdot \overline{Q_{2}} \cdot \overline{Q_{1}} = Q_{2} \oplus Q_{3} + \overline{Q_{3}} \cdot \overline{Q_{2}} \left( Q_{1} + \overline{Q_{1}} \right) = Q_{2} \oplus Q_{3} + \overline{Q_{3}} \cdot \overline{Q_{2}} = Q_{2} \oplus Q_{3} + \overline{Q_{2}} \left( Q_{3} + \overline{Q_{3}} \right) = \overline{\overline{Q_{2} \oplus Q_{3} + \overline{Q_{2}}}} = \overline{\overline{Q_{2} \oplus Q_{3} + \overline{Q_{$$

На рис. 40 показана функциональная схема пересчетного устройства.

**Рис. 38.** Граф генератора чисел 7 – 2 – 4 – 11

**Рис. 39.** Генератор чисел 7 - 2 - 4 - 11 на четырёх *JK*-триггерах КР1533ТВ15

**Рис. 40.** Пересчётное устройство с модулем счёта k = 5

Функцию  $D_r = \overline{Q_2 \oplus Q_3} \cdot Q_2$  можно реализовать также на одном корпусе КР1533ЛП12 по схеме рис. 41.

**Рис. 41.** Реализация функции  $D_r = \overline{Q_2 \oplus Q_3} \cdot Q_2$  на одном корпусе КР1533ЛП12

Граф пересчетного устройства показан на рис. 42.

Рис. 42. Граф пересчетного устройства, приведенного на рис. 40

2.5. В задаче 2.4 обеспечить k=6 (скачок должен быть из состояния  $a_3=011,\ D_r=0$ ). Регистр построить на КР1533TM8.

#### Решение.

Обратную связь  $D_{r}$  запишем в следующем виде:

$$D_r = (Q_2 \oplus Q_3) \cdot \overline{\overline{Q_3}Q_2Q_1} + \overline{Q_3} \cdot \overline{Q_2} \cdot \overline{Q_1}$$

.

$\overline{Q_3} \cdot \overline{Q_2} \cdot \overline{Q_1}$  упростится до  $\overline{Q_2} \cdot \overline{Q_1}$  . Тогда

$$D_{r} = (Q_{2} \oplus Q_{3}) \cdot \overline{\overline{Q_{3}Q_{2}Q_{1}}} + \overline{Q_{2}} \cdot \overline{Q_{1}} = (Q_{2} \oplus Q_{3})(Q_{3} + \overline{Q_{2}} + \overline{Q_{1}}) + \overline{Q_{2}} \cdot \overline{Q_{1}} = \overline{(Q_{2} \oplus Q_{3})Q_{3} + (Q_{2} \oplus Q_{3})\overline{Q_{2}} + (Q_{2} \oplus Q_{3})\overline{Q_{1}} + \overline{Q_{2}} \cdot \overline{Q_{1}}}$$

Функциональная схема приведена на рис. 43 и содержит 3 корпуса ИМС (КР1533ТМ8, КР1533ЛР13, КР1533ЛП5).

Рис. 43. Функциональная схема к задаче 2.5

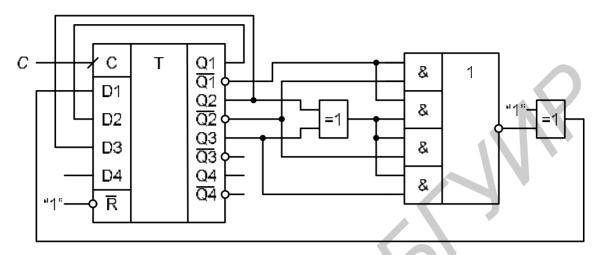

2.6. Построить на KP1533TM2 и ИМС той же серии 3-разрядный счетчик, который при управляющем сигнале M=1 работает как счетчик в коде Грея, а при M=0 как двоичный суммирующий счетчик.

#### Решение.

Можно составить таблицу переходов, нанести на карты Карно функции возбуждения  $D_i$  D-триггеров, минимизировать межразрядные связи как функции  $f(Q_2,Q_1,Q_0,M)$ , преобразовать их для реализации на логических элементах с минимальным количеством корпусов.

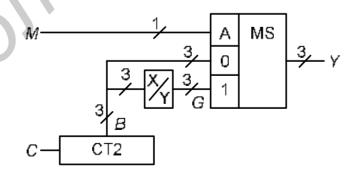

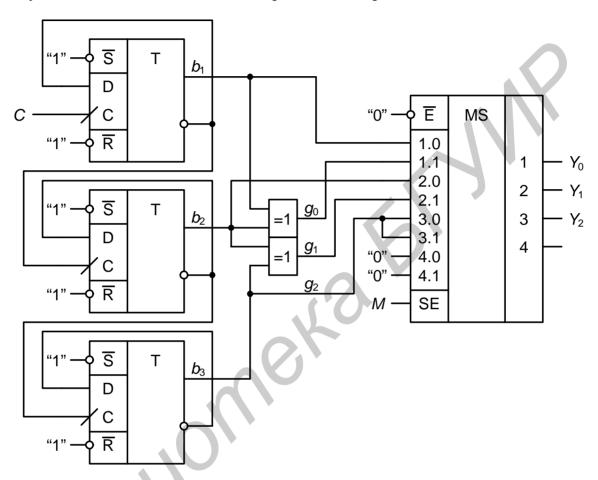

Рассмотрим ещё один вариант решения задачи по схеме рис. 44, где X/Y – преобразователь двоичного кода в код Грея.

**Рис. 44.** Структурная схема счётчика (с выходами У), который при M=1 работает как счетчик в коде Грея (G), а при M=0 как двоичный (B) суммирующий счетчик

Сам счётчик СТ2 постоянно работает как двоичный суммирующий счётчик, но на выход  $Y=y_2y_1y_0$  мультиплексора-селектора в зависимости от сигнала по входу M проходит либо двоичный код  $B=b_2b_1b_0$ , либо код Грея  $G=g_2g_1g_0$ .

Как известно  $g_i = b_i \oplus b_{i+1}$ , при  $0 \le i \le n-1$  и  $g_n = b_n$ . Функциональная схема задачи приведена на рис. 45.

Рис. 45. Функциональная схема к задаче 2.6

Схема на рис. 45 построена на четырёх корпусах серии КР1533 (2 корпуса КР1533TM2, 1 корпус КР1533ЛП5, 1 корпус КР1533КП16).

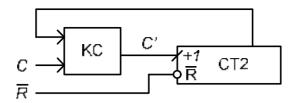

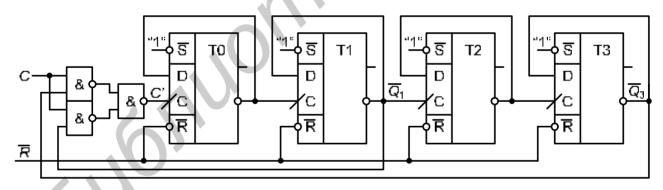

2.7. Синтезировать на КР1533ТМ2 и логических элементах той же серии асинхронный суммирующий счётчик с остановкой в состоянии  $a_{_{10}}=1010$ . Для повторного цикла счёта предусмотреть общий вход сброса  $\overline{R}$ . Привести несколько тактов временной диаграммы  $(a_{_{8}},a_{_{9}},a_{_{10}},a_{_{0}},a_{_{1}})$ .

## Решение.

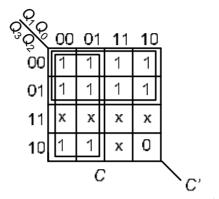

Необходимо разработать комбинационную схему КС (рис. 46), выход которой C' = C (C – вход счётных импульсов) при состояниях счётчика  $a_0 - a_9$  и C' = 0 при  $a_{10} = 1010$ , а при  $a_{11} - a_{15}$  – безразличное значение. Покажем это на карте Карно (рис. 47).

Рис. 46. Структурная схема задачи 2.7

**Рис. 47.** Карта Карно для C'и прямых значений C

Функция C' является функцией пяти переменных  $C, Q_0, Q_1, Q_2, Q_3$  и может быть представлена двумя картами Карно C и  $\overline{C}$  для переменных  $Q_0, Q_1, Q_2, Q_3$ . Карта  $\overline{C}$  нас не интересует, поэтому рассмотрим карту для C (рис. 47).

По карте Карно, приведенной на рис. 47, получаем

$$C' = C\overline{Q}_3 + C\overline{Q}_1 = \overline{C\overline{Q}_3}\overline{C\overline{Q}_1}$$

.

Функциональная схема счётчика показана на рис. 48.

**Рис. 48.** Функциональная схема счётчика с остановкой в состоянии  $a_{10} = 1010$  Временная диаграмма приведена на рис. 49.

2.8. На ИМС КР1554ТМ8 и логических элементах той же серии построить регистр сдвига, имеющий последовательность состояний  $a_1 - a_3 - a_7 - a_6 - a_4$ . Решение.

Обозначив выход логики обратной связи  $D_r = f(Q_2, Q_1, Q_0)$ , составим ее таблицу истинности (табл. 18), учитывая, что для устранения "застревания" схемы в  $a_0 D_r$  должна равняться 1, а в  $a_7 - D_r = 0$ .

Рис. 49. Фрагмент временной диаграммы схемы, приведенной на рис. 48

Таблица 18

| $Q_2$ | $Q_1$ | $Q_0$ | $D_r$ |

|-------|-------|-------|-------|

| 0     | 0     | 1     | 1     |

| 0     | 1     | 1     | 1     |

| 1     | 1     | 1     | 0     |

| 1     | 1     | 0     | 0     |

| 1     | 0     | 0     | 1     |

| 0     | 0     | 0     | 1     |

| 0     | 1     | 0     | ×     |

| 1     | 0     | 1     | ×     |

Нанеся  $D_r$  на карту Карно или из табл. 18 можно записать:

$$\overline{D}_r = Q_2 Q_1, \ D_r = \overline{Q_2 Q_1}.$$

Функциональная схема приведена на рис. 50.

Пунктирные цепи относятся к следующей задаче.

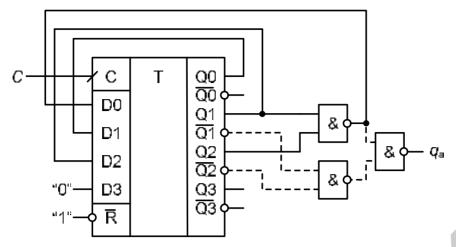

2.9. На ИМС КР1554ТМ8 построить регистр сдвига, генерирующий двоичную последовательность 1-0-1-1=0.

Двоичная последовательность имеет длину L=5. Из графа трёхразрядного регистра сдвига выбираем замкнутую последовательность состояний и определяем  $D_r$ . Эта часть задачи есть в решении задачи 2.8. К регистру подключаем выходную логику с выходом  $q_a$  (табл. 19).

Рис. 50. Регистр сдвига к задаче 2.8

Таблица 19

| $Q_2$ | $Q_1$ | $Q_0$ | $q_a$ |

|-------|-------|-------|-------|

| 0     | 0     | 1     | 1     |

| 0     | 1     | 1     | 0     |

| 1     | 1     | 1     | 1     |

| 1     | 1     | 0     | 1     |

| 1     | 0     | 0     | 0     |

| 0     | 0     | 0     | ×     |

| 0     | 1     | 0     | ×     |

| 1     | 0     | 1     | ×     |

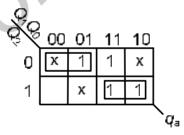

Нанесём  $q_a$  на карту Карно (рис. 51). Получим  $q_a=\overline{Q}_2\overline{Q}_1+Q_2Q_1=\overline{\overline{Q}_2\overline{Q}_1}\overline{Q}_2\overline{Q}_1$  (пунктир на рис. 50).

**Рис. 51.** Карта Карно для  $q_{\scriptscriptstyle a}$ .

#### ЛИТЕРАТУРА

- 1. Качинский М.В. Методическое пособие по курсу «Проектирование цифровых устройств на ИМС» для студ. спец. Т.08.02.00 «Проектирование и технология электронных вычислительных средств» / М.В. Качинский, Г.В. Таранов; Под ред. И.М. Русака. Мн.: БГУИР, 2001. 23 с.

- 2. Логические ИС КР1533, КР1554: Справочник: В 2 ч. / И.И. Петровский, А.В. Прибыльский, А.А. Троян, В.С. Чувелев. М.: БИНОМ, 1993. 496 с.

- 3. Голдсуорт Б. Проектирование цифровых логических устройств: Пер. с англ. М.В. Сергиевского; Под ред. Ю.И. Топчеева. М.: Машиностроение, 1985. 288 с.

- 4. Угрюмов Е.П. Цифровая схемотехника. СПБ.: БХВ Санкт-Петербург, 2000.-528 с.

- 5. Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для втузов. СПб.: Политехника, 1996. 885 с.

- 6. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. М.: Радио и связь, 1990.-304 с.

- 7. Цифровые интегральные микросхемы: Справ. / М.И. Богданович, И.Н. Грель, С.А. Дубина и др. 2-е изд., перераб. и доп. Мн.: Беларусь: Полымя, 1996. 605 с.

- 8. Таранов Г.В., Качинский М.В., Клюс В.Б., Давыдов А.Б. Лабораторный практикум курсам «Основы логического проектирования ПО ЭВС», «Проектирование цифровых устройств на ИМС» для студ. спец. Т.08.02.00 «Проектирование технология электронных И вычислительных средств» / Г.В. Таранов, М.В. Качинский, В.Б. Клюс, А.Б. Давыдов. – Мн.: БГУИР, 2001. – 28 с.

#### Учебное издание

Таранов Геннадий Васильевич, Качинский Михаил Вячеславович, Клюс Владимир Борисович, Давыдов Александр Борисович

# ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ

# Методическое пособие

по курсу «Основы проектирования ЭВС» для студентов специальности I-40 02 02 «Электронные вычислительные средства» дневной формы обучения

#### Редактор Т.П. Андрейченко

Подписано в печать Гарнитура «Таймс». Уч.-изд. л. 1,8.

Формат 60х84 1/16. Печать ризографическая. Тираж 200 экз. Бумага офсетная. Усл. печ. л. Заказ 452.

Издатель и полиграфическое исполнение: Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники» ЛИ №02330/0056964 от 01.04.2004. ЛП №02330/0131518 от 30.04.2004. 220013, Минск, П. Бровки, 6