# Экспресс-контроль элементов интегральных микросхем с использованием растровой электронной микроскопии и режима наведенного тока

АЛЕКСАНДР ПЕТЛИЦКИЙ, ДМИТРИЙ ЖИГУЛИН, ВЛАДИМИР ЛАНИН

Рассмотрена методика выявления отказов элементов интегральных схем растровой электронной микроскопией в режиме наведенного тока EBIC. Данный метод является основой экспресс-контроля работоспособности ИС и отдельных интегральных элементов.

### **ВВЕДЕНИЕ**

Современный уровень технологий позволяет производить микроэлектронные структуры чрезвычайно малых размеров. Размер затвора современных наиболее малых массово производимых транзисторов составляет 18 нм. Надежность работы таких структур определяется не только современным уровнем развития технологии производства и квалификацией персонала, но и способами контроля работоспособности элементов интегральной электроники.

Для определения значения линейных размеров в субмикронном диапазоне применяют различные виды высокоразрешающей микроскопии, такие как сканирующая зондовая микроскопия, просвечивающая электронная микроскопия, растровая электронная микроскопия, микроскопия на основе фокусированных ионных пучков и т. д. Однако, для решения задач, требующих

оперативного контроля (без специальной пробоподготовки) подходит только растровая электронная микроскопия.

Перспективным методом выявления отказов, как целых блоков, так и отдельных элементов интегральных схем (ИС) является растровая электронная микроскопия в режиме наведенного тока (Electron Beam Induced Current) EBIC [1]. Данный метод широко распространен в ряде крупных компаний и применяется в качестве экспресс-контроля работоспособности ИС или отдельных интегральных элементов. Он отличается своей простотой, быстродействием и не требует специальной подготовки образцов к измерениям. Метод ЕВІС может использоваться для исследования электрофизических свойств полупроводников и приборов микроэлектроники, поскольку он позволяет определить области локальных дефектов, места утечек и пробоев, а также оценить параметры и местоположения p-n-переходов.

Сравнительный анализ годных ИС с бракованными, позволяет определить отказавшие электронные модули, а дальнейший их детальный анализ – установить причину отказа. Таким образом, поэтапный анализ кристалла ИС позволяет не только производить отбраковку микросхем, но и выявлять место и причину отказа. Метод наведенного тока также может быть использован и для изучения электрофизических свойств полупроводниковых структур на отдельных этапах технологического процесса.

# **МЕТОДИКА ЕВІС**

При взаимодействии электронного пучка с поверхностью твердого тела происходит образование электроннодырочных пар, вызывающих генерацию тока в полупроводниках. На основе анализа распределения сигнала наведенного тока можно дать оценку различным свойствам полупроводника.

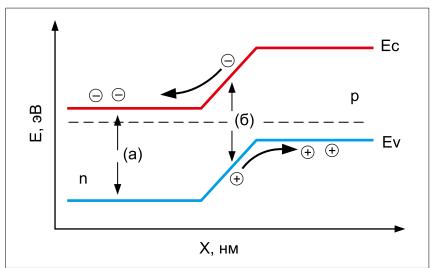

На рисунке 1 показана энергетическая диаграмма *p-n*-перехода. Когда пучок электронов попадает в область *p-n*-перехода (б), то электроны и дырки, возникающие под действием электронного пучка, расходятся в разные стороны за счет электрического поля Е, присутствующего в области перехода. Носители заряда, которые возникают в объеме полупроводника (а), где отсутствует электрическое поле, с большой вероятностью рекомбинируют друг с другом.

Для проведения измерений и получения изображений электронный микроскоп должен быть оснащен детектором EBIC. Если подключить устройство, содер-

Рис. 1. Энергетическая диаграмма р-п-перехода

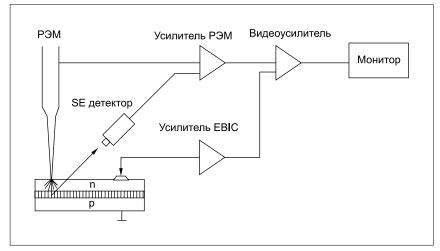

жащее p-n-переход к такому детектору, то на изображении станут видны области, содержащие p-n-переход, яркость которых будет зависеть от параметров перехода. На рисунке 2 показана схема измерения методом EBIC. В методе EBIC электронный пучок сканирует полупроводниковый образец, содержащий *p-n*-переход либо барьер Шоттки. Энергия электронов в пучке составляет от 1 до 30 кэВ, в то время как минимальная энергия, необходимая для образования электронно-дырочной пары в полупроводнике и определяемая шириной запрещенной зоны, составляет порядка 1-3 эВ.

В результате воздействия электронного пучка в полупроводнике образуется большое число электроннодырочных пар. Электронно-дырочные пары генерируются в материале внутри ограниченного объема (объема генерации). Важными здесь являются неосновные носители заряда — электроны для полупроводника р-типа, и дырки для полупроводника n-типа [2].

Возбужденные пучком электроны и дырки двигаются случайно, генерируются и рекомбинируют друг с другом.

Модуль EBIC используется для настройки параметров усиления тока, наведенного электронным пучком, с целью получения карты тока, собранного в каждой точке сканирования. Наведенный электронным пучком ток попадает на зонд манипулятора в выбранных областях контакта (см. рис. 2). При сканировании электронным пучком высокоэнергетические электроны инжектируются в образец, проникают через оксидные и металлические слои полупроводника до p-n-перехода и генерируют электронно-дырочные пары, которые разделяются внутренним электрическим

Рис. 2. Схема измерения полупроводниковой структуры методом ЕВІС

полем *p-n*-перехода [3]. Электроны или дырки, попадая в проводящую область, вызывают ток, детектируемый зондом и обрабатываемый затем усилителем. Ток, вызванный при этом, преобразовывается в напряжение, которое подается на видеоусилитель монитора микроскопа.

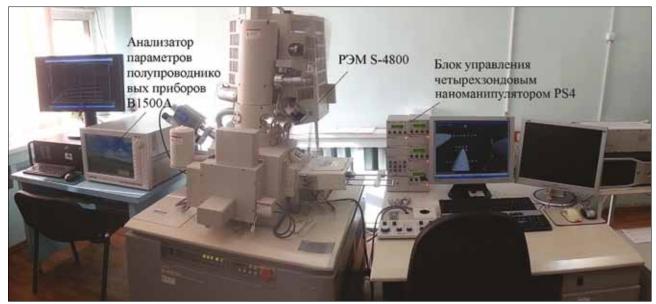

Для проведения измерений в режиме EBIC применяют растровый электронный микроскоп РЭМ типа S-4800 фирмы НІТАСНІ (Япония) и четырехзондовый наноманипулятор PS4 фирмы KLEINDIEK (Германия). На рисунке 3 показан измерительный комплекс по контролю элементов ИС методом EBIC. Экспресс-анализ отказавших кристаллов методом EBIC необходимо проводить по сравнению с заведомо годным кристаллом. Для этого вначале необходимо закрепить заведомо годный кристалл ИС на объектодержатель с помощью токопроводящего клея. Крепеж кристалла должен производиться на поднятых рабочих элементах манипулятора. Данный кристалл будет

являться эталонным, относительно которого будут сравниваться все остальные кристаллы ИС.

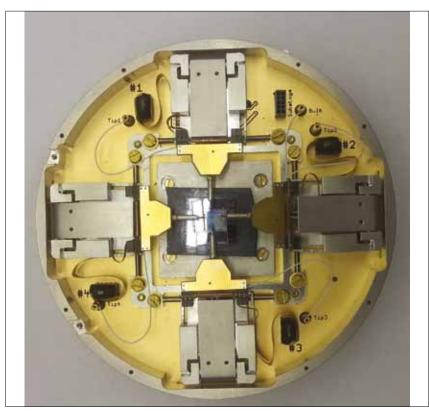

С помощью пинцета на поднятые рабочие элементы манипулятора надевают заостренные и загнутые специальные вольфрамовые иглы, после чего аккуратно опускают рабочие элементы вместе с зондами как можно ближе к поверхности кристалла, но не касатясь его. Механическим усилием сводят зонды в центр кристалла, как показано на рисунке 4. Зондодержатель с кристаллом ИС устанавливают в рабочую камеру электронного микроскопа (см. рис. 5). Далее поднимают столик микроскопа вместе с зондодержателем в максимально высокое положение (WD = 1,5 mm).

Для перевода РЭМ S-4800 в режим измерения наведенных токов в меню управления устанавливают ускоряющее напряжение 15 кВ; ток эмиссии (le) 10 мкА; ток образца (Probe Current) в режим High; в сигнале управления

Рис. З. Измерительный комплекс контроля элементов ИС методом ЕВІС

Рис. 4. Внешний вид зондодержателя с опущенными зондами

Рис. 5. Загрузка зондодержателя в РЭМ S-4800

Рис. 6. Блок управления нанозондом №1

(Signal Select) выбрать SE. На левом экране появится изображение поверхности кристалла в SE электронах. Правый экран предназначен для отображения поверхности в наведенных токах.

При запуске блока управления четырехзондовым наноманипулятором на информационном экране (см. рис. 6) отобразится информация о координатах зонда (3) (начальное значение нулевое), шаге перемещения (4) и скорости передвижения (5). Начальная скорость движения по умолчанию равна 6. Это самая быстрая скорость. Она может быть понижена до 1 с помощью кнопки (1) или увеличена до 6 с помощью кнопки 2.

Для того чтобы перевести блок управления в режим EBIC (см. рис. 7) необходимо переключателем режима управления (1) (Моde) выбрать режим DC (режим наведенного тока); переключателем (4) установить коэффициент усиления Gain на 7. При необходимости тонкой настройки усиления можно использовать регулятор (3). Затем переключатель (7) перевести в положение Invert off; переключатель (8) перевести в положение Tip Volt Int; регулятор контрастности (5) (грубо) и (6) (тонко) установить в среднее положение.

Для экспресс-анализа выбирают необходимую контактную площадку на кристалле и один из четырех зондов, который будет контактироваться к ней. Присоединяют выбранный зонд к блоку управления четырехзондовым наноманипулятором PS4 через входной разъем 2 и с помощью ручек CLKW (9) (движение зонда влево-вправо), UP (10) (подъем-опускание), RETRACT (11) (движение зонда вперед-назад) и кнопок (12) (увеличить скорость перемещения), (13) (уменьшить скорость перемещения) подводят зонд и касаются выбранной контактной площадки. В момент касания на правом экране монитора появятся разводы в виде полос.

Кнопкой Slow (3) на экране монитора запускают минимально возможную скорость развертки; производят настройку полученной картинки в наведенном токе с помощью ручек управления (3–6) блока управления. Необходимо помнить, что чем выше коэффициент усиления сигнала, тем больше усиливаются шумы, помехи и наводки. Поэтому, предпочтение отдают не коэффициенту усиления сигнала, а величине тока, падающего на образец. Если все манипуляции проведены правильно, то должно получиться следующее изображение поверхности кристалла (см. рис. 8).

Для получения изображения кристалла в режиме EBIC на данной контактной площадке на ускоряющих напряжениях 20 и 30 кВ необходи-

Рис. 7. **Блок управления четырехзондовым** наноманипулятором **PS4**

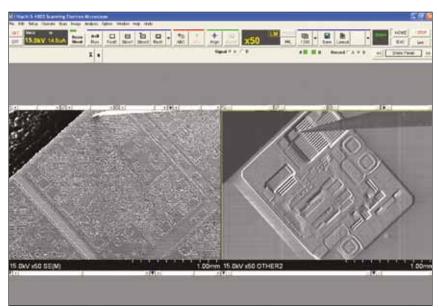

Рис. 8. Изображение поверхности кристалла в режиме ЕВІС

Рис. 9. Выявление отказавшего кристалла методом ЕВІС

Рис. 10. Биполярный транзистор в режиме ЕВІС, с локализованным местом пробоя эмиттер-база

мо, не поднимая зонд, перевести РЭМ в режим 20, а затем 30 кВ. Таким образом, для каждой контактной площадки будет получено три изображения поверхности ИМС в режиме EBIC с разным ускоряющим напряжением. Далее сравнивают изо-

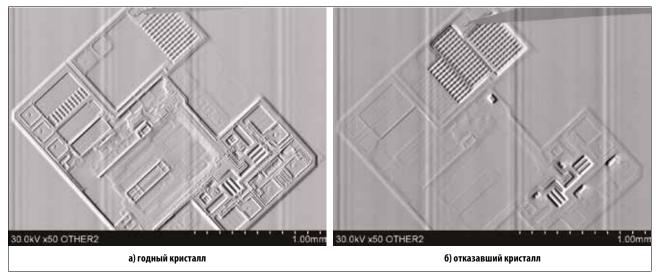

бражения, полученные от годного кристалла, со всеми остальными кристаллами ИС. Существенные отличия в изображениях указывают на проблемные или отказавшие места микросхемы, например, повреждение проводника (см. рис. 9).

Рис. 11. Конденсатор в режиме ЕВІС с локализованным местом пробоя

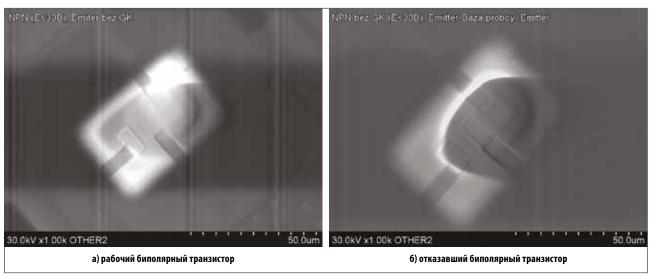

Задача разбраковки топологических элементов существенно упрощается, если данные элементы находятся в тестовом модуле. В этом случае каждому элементу соответствует своя контактная площадка (либо несколько контактных площадок), что существенно уменьшает количество измерений, а значит, и время, необходимое на выявление и идентификацию отказавшего элемента. На рисунке 10 показаны рабочий и отказавший биполярные транзисторы в сравнении в режиме EBIC

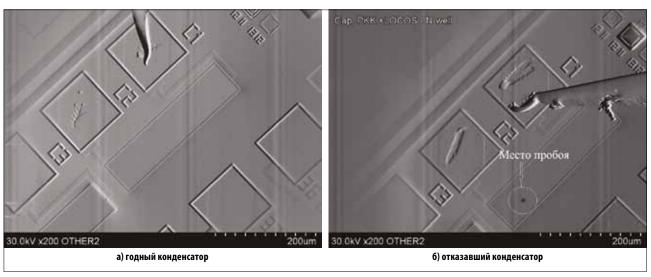

На рисунке 11 показан отказавший конденсатор в сравнении с годным в режиме EBIC.

# выводы

Экспресс-анализ методом EBIC позволяет быстро и оперативно проводить отбраковку кристаллов ИС, отделяя бракованные кристаллы. Отсутствие специальной пробоподготовки, его простота и доступность – основное преимущество данного метода анализа. Помимо сравнительного анализа годных и бракованных ИС, метод EBIC позволяет детально исследовать нерабочие места схемы и установить причину их отказа. В частности, данным методом можно определить причину выхода транзистора или диода из строя, локализо-

вать место пробоя конденсатора. Таким образом, метод EBIC может использоваться для исследования электрофизических свойств полупроводниковых приборов, определять области локальных дефектов, места утечек, пробоев, а также узнать параметры и местоположения *p-n*-переходов.

Метод EBIC может быть рекомендован как неразрушающий метод экспресс-контроля работоспособности интегральных компонентов.

## ЛИТЕРАТУРА

- 1. Advanced Scanning Electron Microscopy Methods and Applications to Integrated Circuit Failure Analysis/Jr. Cole [and ets.]//Scanning Microscopy, 1988. № 2.

- 2. Исследование локальных свойств приборных структур микроэлектроники методом наведенного тока/А. Н. Антанович, А. А. Петрушин, Е. В. Доронин, А. Н. Бурцев.//Материалы Международной научной конференции INTERMATIC—2016, Москва, 21—25 ноября 2016.

- 3. Altmann, F. Combined electron beam induced current imaging (EBIC) and focused ion beam (FIB) techniques for thin film solar cell characterization/F. Altmann, J. Schischka//Proceedings from the 36th International Symposium for Testing and Failure Analysis. 2010.