Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

Институт информационных технологий

Кафедра информационных систем и технологий

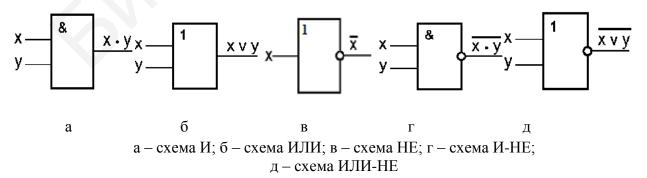

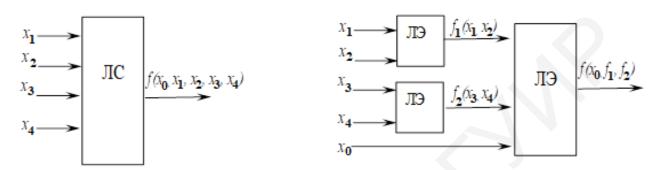

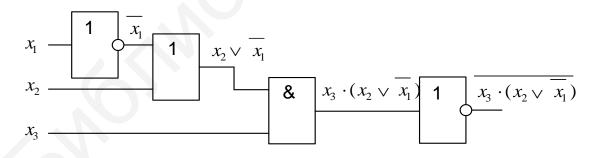

Ю. А. Скудняков, И. И. Шпак

## ВЫЧИСЛИТЕЛЬНЫЕ МАШИНЫ И СИСТЕМЫ

Рекомендовано УМО по образованию в области информатики и радиоэлектроники в качестве учебно-методического пособия для выполнения контрольных работ для специальности 1-36 04 02 «Промышленная электроника»

УДК [004.38+004.7](076) ББК 32.973.202я73 С46

#### Рецензенты:

кафедра программного обеспечения информационных систем и технологий Белорусского национального технического университета, (протокол №9 от 20.03.2019);

доцент кафедры энергоэффективных технологий учреждения образования «Международный государственный экологический институт имени А. Д. Сахарова» Белорусского государственного университета кандидат технических наук, доцент В. И. Красовский

## Скудняков, Ю. А.

С46 Вычислительные машины и системы : учеб.-метод. пособие / Ю. А. Скудняков, И. И. Шпак. – Минск : БГУИР, 2020. – 79 с. : ил. ISBN 978-985-543-551-9.

Приведены краткие сведения по теоретическим основам вычислительных машин и систем, теоретическим основам организации памяти современных ЭВМ и вычислительных систем, логическим основам ЭВМ, методикам анализа и синтеза комбинационных схем. Рассмотрена общая характеристика контрольной работы, предложено по три индивидуальных задания для каждого студента.

Предназначено для студентов специальности 1-36 04 02 «Промышленная электроника» заочной формы получения высшего образования, может быть полезно студентам других специальностей, а также магистрантам, аспирантам и специалистам, занимающимся проектированием, созданием и эксплуатацией современных ЭВМ и вычислительных систем.

УДК [004.38+004.7](076) ББК 32.973.202я73

ISBN 978-985-543-551-9

© Скудняков Ю. А., Шпак И. И., 2020

<sup>©</sup> УО «Белорусский государственный университет информатики и радиоэлектроники», 2020

## Содержание

| Введение                                                     | 4  |

|--------------------------------------------------------------|----|

| Общая характеристика контрольной работы                      | 5  |

| 1 Задание №1                                                 |    |

| Краткие сведения по теоретическим основам вычислительных     |    |

| машин и систем                                               |    |

| 1.1 История развития электронных вычислительных машин        | 6  |

| 1.2 Элементы и узлы ЭВМ                                      | 10 |

| 1.3 Форматы хранения информации                              |    |

| 1.4 Периферийные устройства ЭВМ                              | 16 |

| 1.5 Интерфейс компьютерной системы                           | 18 |

| 1.6 Архитектура команд вычислительной системы                |    |

| 1.7 Центральный процессор вычислительной машины              | 28 |

| 1.8 Тенденции развития вычислительной техники                | 32 |

| 1.9 Содержание задания №1                                    | 33 |

| 1.10 Вопросы к заданию №1                                    |    |

| 2 Задание №2                                                 |    |

| Краткие сведения по теоретическим основам организации памяти |    |

| современных ЭВМ и систем                                     | 36 |

| 2.1 Организация памяти вычислительной системы                | 36 |

| 2.2 Содержание задания №2                                    | 55 |

| 2.3 Вопросы к заданию №2                                     | 55 |

| 3 Задание №3                                                 |    |

| Краткие сведения по логическим основам ЭВМ,                  |    |

| методикам анализа и синтеза комбинационных схем              | 58 |

| 3.1 Логические основы ЭВМ                                    |    |

| 3.2 Методика выполнения задания №3                           |    |

| 3.3 Содержание задания №3                                    |    |

| Питепатура                                                   | 78 |

#### Введение

Информатизация всех отраслей экономики и оснащение современных производств новейшим технологическим оборудованием, вычислительными машинами и системами высокого быстродействия являются важнейшим необходимым условием научно-технического прогресса, в том числе и в области промышленной электроники. Эффективное использование вычислительных машин и систем и создание на их основе современных средств автоматизации и управления основываются на знании принципов действия как аппаратных компонентов вычислительной техники, так и программного обеспечения вычислительной техники.

Целью изучения дисциплины «Вычислительные машины и системы» (ВМиС) является получение студентами знаний о принципах организации и построения цифровых вычислительных систем и сетей, логических основах их работы, функциональных возможностях современных контроллеров, программируемых логических интегральных схем, вычислительных машин и систем и их структурных компонентов, а также навыков использования современных средств автоматизированного проектирования.

В результате изучения дисциплины «Вычислительные машины и системы» обучаемый должен знать:

- многообразие архитектур вычислительного комплекса;

- принципы построения и функционирования операционных устройств вычислительных машин;

- историю и перспективные направления развития вычислительных машин, систем и сетей;

- модели и методы организации процессоров и памяти современной вычислительной техники;

- принципы работы устройств и блоков современных вычислительных машин, систем и сетей.

В результате изучения дисциплины студент должен уметь:

- использовать системы автоматизированного проектирования узлов вычислительных комплексов;

- применять методы и модели различной степени детализации проекта;

- применять технические средства систем автоматизированного проектирования;

- применять современные технологические решения при использовании микропроцессоров, модулей памяти и периферийных устройств вычислительных систем;

- грамотно формулировать постановку задачи проектирования и тестирования компонентов контроллеров и вычислительных систем;

- применять базовые научно-теоретические знания для решения теоретических и практических задач.

Выполнение контрольных работ является одной из важнейших форм самостоятельной работы студента по усвоению материала дисциплины.

## ОБЩАЯ ХАРАКТЕРИСТИКА КОНТРОЛЬНОЙ РАБОТЫ

Учебной программой дисциплины ВМиС предусмотрено выполнение одной контрольной работы (КР). Варианты заданий указываются преподавателем индивидуально каждому студенту во время установочной сессии и соответствуют порядковому номеру студента в группе на момент выдачи задания.

Выполнение индивидуального задания по КР предусматривает не только изучение студентами учебной и методической литературы, но и самостоятельную работу над справочной и специальной научно-технической литературой, патентными и рекламно-информационными источниками.

Основная цель выполнения контрольной работы состоит в изучении учебного материала по всем темам дисциплины: в изучении выданных преподавателем теоретических вопросов и поиске ответов на них и решении задач.

КР по дисциплине ВМиС предусматривает выполнение трех заданий.

Для выполнения первого задания требуется изучение и усвоение материала дисциплины, необходимого для ответа на один или группу вопросов по всем разделам программы.

Второе задание предусматривает изучение и усвоение материала по различным видам организации памяти современных ЭВМ и систем. Для этого студенту необходимо усвоить информацию о назначении, принципах построения и функционирования, результатах проведенного сравнительного анализа и методиках выбора видов памяти в зависимости от класса решаемых задач с помощью современных ЭВМ и компьютерных систем, рассмотреть пути перспективного развития устройств памяти.

Для выполнения третьего задания студент должен изучить логические основы ЭВМ, методику анализа и синтеза комбинационных схем, решить задачу их построения. Результаты выполнения задания необходимо представить в письменном и (или) электронном виде.

#### 1 Задание №1

## **Краткие сведения по теоретическим основам вычислительных** машин и систем

Данный раздел содержит только краткие сведения о принципах построения и функционирования вычислительных машин и систем. Более полная информация по данному разделу представлена в приведенных ниже литературных источниках.

**Вычислительная машина** (**BM**), или компьютер, — комплекс технических и программных средств, предназначенный для решения задач пользователя путем автоматической обработки информации.

**Вычислительная система** (**BC**) — совокупность взаимодействующих процессоров или вычислительных машин, периферийного оборудования и программного обеспечения, предназначенная для решения задач пользователей.

## 1.1 История развития электронных вычислительных машин

Впервые классическую архитектуру ВМ предложил Джон фон Нейман. *Основные принципы организации неймановской ВМ*:

- использование двоичной системы счисления для представления информации;

- программы и данные записываются в двоичном коде с использованием форматов одинаковой длины с сохранением их в общих запоминающих устройствах, следует выполнять операции над командами программы как над числами;

- управление вычислительным процессом осуществляется централизованно путем последовательного выполнения команд, а каждая команда руководит выполнением одной операции и передает управление следующей команде;

- память BM имеет линейную организацию она состоит из последовательно пронумерованных ячеек.

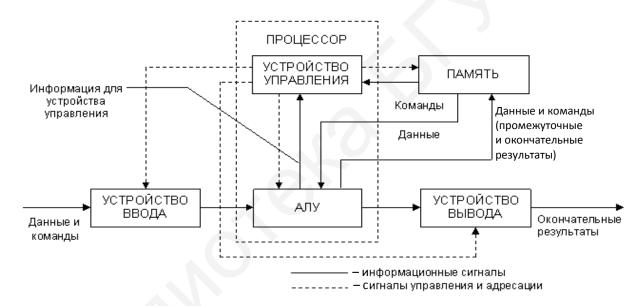

Укрупненная схема неймановской ВМ представлена на рисунке 1.

Рисунок 1 – Укрупненная схема неймановской ВМ

ВМ состоит из нескольких основных устройств:

- арифметико-логического устройства (АЛУ);

- устройства управления (УУ);

- памяти:

- устройства ввода и вывода.

АЛУ выполняет логические и арифметические операции для переработки информации, хранящейся в памяти.

УУ обеспечивает управление и контроль всех устройств ВМ (управляющие сигналы указаны пунктирными стрелками).

Данные, хранящиеся в запоминающем устройстве, представлены в дво-ичной форме.

Программа работы ВМ и данные хранятся в одном и том же устройстве памяти.

Для ввода и вывода информации используются устройства ввода и вывода (периферийные устройства).

В архитектуре фон Неймана применяется однородная память микропроцессора, в которую могут записываться различные программы. При этом специальная программа-загрузчик работает с ними как с данными. Затем управление может быть передано этим программам, и они уже начинают выполнять свой алгоритм. При подобном подходе к управлению микропроцессором удается достигнуть максимальной гибкости работы ВМ.

Недостатком архитектуры фон Неймана является возможность непреднамеренного нарушения работоспособности **BM** (программные ошибки) и преднамеренное уничтожение ее работы (вирусные атаки).

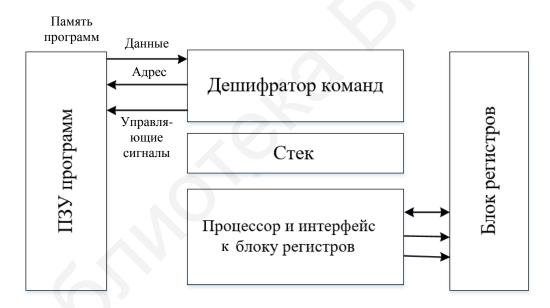

**В гарвардской архитектуре, в отличие от неймановской,** имеют место раздельное хранение и обработка команд и данных. Для работы с памятью программ и с памятью данных организуются отдельные шины обмена данными (системные шины) (рисунок 2).

Рисунок 2 – Структура гарвардской архитектуры

Гарвардская архитектура применяется в микроконтроллерах и сигнальных процессорах, где требуется обеспечить высокую надежность работы аппаратуры. К недостаткам такой архитектуры можно отнести высокую стоимость и большое количество внешних выводов микропроцессора.

Современные ВМ в основном базируются на неймановской архитектуре в силу ее более простой реализации.

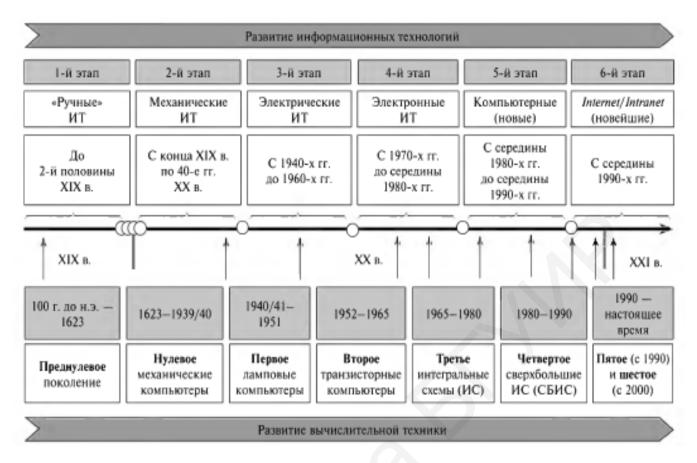

Кратко история развития вычислительной техники и информационных технологий отображена на рисунке 3.

Рисунок 3 – История развития вычислительной техники и информационных технологий

Из рисунка видно, что благодаря развитию элементной базы и компьютерных технологий в настоящее время широко используются наиболее компактные, надежные, экономичные и комфортные персональные компьютеры (ПК), на базе которых создаются и используются современные компьютерные комплексы, системы и сети, позволяющие решать задачи разной сложности в различных сферах человеческой деятельности благодаря использованию информационных ресурсов, имеющих место как в отдельном ПК, так и в компьютерах сети Интернет. Кроме того, современные ПК, обладая относительно высокими показателями качества, такими как производительность, время обработки данных, надежность и приемлемая стоимость, в настоящее время вполне отвечают требованиям большинства пользователей.

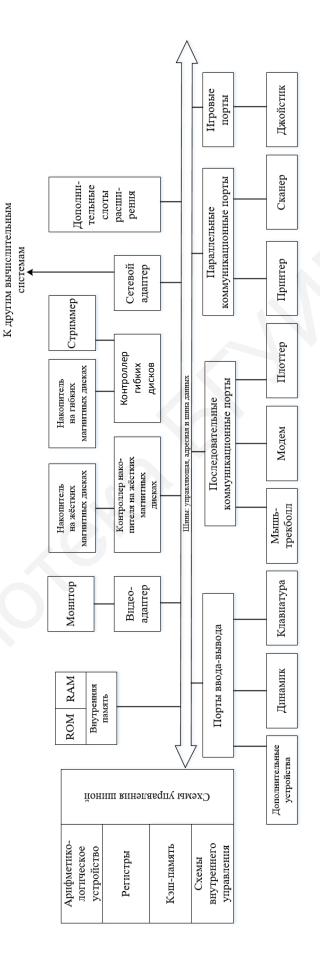

Структура современного ПК представлена на рисунке 4 и содержит основные взаимосвязанные функциональные модули компьютера.

Рисунок 4 – Структура современного ПК

## 1.2 Элементы и узлы ЭВМ

Каждый модуль, представленный в структуре ПК, состоит из ряда элементов и узлов, необходимых для полноценного функционирования компьютера (см. рисунок 4). К таким элементам и узлам можно отнести: триггеры, элементы различных видов памяти, сумматоры, мультиплексоры, дешифраторы, компараторы, регистры, счетчики и т. д.

Основным узлом ПК является материнская плата, представляющая собой многофункциональный модуль, содержащий ряд основных компонентов, в том числе и микропроцессор.

Микропроцессор состоит:

- из арифметико-логического устройства (АЛУ), предназначенного для выполнения арифметических и логических операций;

- устройства управления (УУ), выполняющего функции управления работой отдельных модулей и ПК в целом;

- микропроцессорной памяти (МП), предназначенной для хранения обрабатываемых данных и программ.

На рисунке 5 представлен общий вид конструктивного исполнения материнской платы ПК с указанием ее основных функциональных компонентов.

Рисунок 5 – Внешний вид конструкции материнской платы ПК

Внешний вид конструкций отдельных основных функциональных компонентов системного блока ПК показан на рисунке 6.

## Структура системного блока

Процессор

Материнская плата

Оперативная память (ОЗУ)

Винчестер (HDD)

Видеокарта

Звуковая карта

Блок питания

Дисковод 3,5" (FDD)

Картридер

Дисковод CD/DVD-ROM

Порру дисковод СD/DVD-ROM

Сетевая карта

Внутренний модем

Рисунок 6 – Конструкции отдельных компонентов системного блока ПК

## 1.3 Форматы хранения информации

#### 1.3.1 Системы счисления

Система счисления — способ представления любого числа посредством некоторого алфавита символов, называемых цифрами.

Существуют непозиционные и позиционные системы счисления.

В непозиционных системах счисления каждая цифра сохраняет свое значение независимо от ее положения в числе.

К таким системам относятся: **египетская**, в которой для изображения чисел используются иероглифы; **римская** и **славянская**, в которых для представления цифр используются буквы латинского и славянского алфавитов соответственно. Данные системы в силу своей сложности реализации не получили практического применения.

**В позиционных системах** значение цифр зависит от их места, или позиции, в числе.

В настоящее время для функционирования ЭВМ применяются позиционные системы счисления с основанием 2, 8, 16, так как в данных системах счисления при той же точности требуется минимальное количество двоичных знаков для представления одного числа.

## 1.3.2 Форматы хранения графических изображений

Для сохранения изображений в памяти создаются и используются графические файлы.

Кодировка графических изображений осуществляется с помощью определенного способа — формата.

В настоящее время для хранения изображений используются различные форматы файлов, однако лишь часть из них практически применяется в подавляющем большинстве программ. Как правило, несовместимые форматы имеют файлы растровых, векторных, трехмерных изображений, хотя существуют форматы, позволяющие хранить данные разных классов. Многие приложения ориентированы на собственные «специфические» форматы, перенос их файлов в другие программы вынуждает использовать специальные фильтры или экспортировать изображения в стандартный формат.

Большое количество сфер применения изображений с различными требованиями к файлам приводит к многообразию графических форматов.

При выборе формата файлов необходимо учитывать, что данный формат должен поддерживаться заданной сферой применения.

Для редактирования изображения могут использоваться маски, если редактирование выполняется повторно с применением формата, в котором помимо изображения будут сохраняться и маски.

# Для хранения векторных изображений используются следующие форматы:

- AutoCADDXF и MicrosoftSYLK (наиболее распространенные форматы);

- WMF формат, используемый графическими программами ОС Windows;

- AI внутренний формат программы Illustrator, может открываться программой Photoshop;

- CDR внутренний формат программы Corel Draw.

# *Хранение растровых изображений осуществляется с помощью сле- дующих форматов:*

- MicrosoftBMP, PCX, TIFF и TGA (наиболее распространенные форматы);

- *TIFF* лучший выбор при передаче изображений и растровой графики в векторные программы и издательские системы;

- JPG формат для сжатия изображения в десятки раз, в котором используется метод сжатия jpeg;

- GIF используется для создания веб-страниц, анимаций;

- PNG формат, использующий метод сжатия без потерь качества, который обозначается deflate;

- -PDF не зависящий от графических программ формат для создания электронной документации, презентаций, а также для передачи графики через компьютерные сети;

- *PSD* внутренний формат программы *Photoshop*, который поддерживается все большим количеством графических программ. Этот формат позволяет

записывать изображение со многими слоями и дополнительными альфаканалами, а также с каналами простых цветов и контурами и другой специфической информацией;

- *PCX* является самым известным форматом. Практически любая программа, работающая с графикой, поддерживает этот формат. Формат *PCX* поддерживает метод сжатия, который обозначается *RLE*. Этот формат используется для штрихованных изображений и для изображений с небольшой глубиной цвета;

- *BMP* формат, который является родным графическим форматом *Windows*. Поддерживается всеми редакторами. В этом формате хранятся небольшие растровые изображения, предназначенные для использования в системе *Windows*. Этот формат невысокого качества и с низкой степенью сжатия. Его не рекомендуется использовать ни для веб-дизайна, ни для передачи.

**Метафайловые форматы** могут хранить и растровые, и векторные данные, среди которых наиболее распространенными являются *WPG*, *Macintosh PICT* и *CGM*.

**Цветовая модель** — математическая модель описания представления цветов в виде кортежей чисел (обычно из трех, реже — четырех значений), называемых цветовыми компонентами или цветовыми координатами. Все возможные значения цветов, задаваемые моделью, определяют цветовое пространство.

Цветовая модель задает соответствие между воспринимаемыми человеком цветами, хранимыми в памяти, и цветами, формируемыми на устройствах вывода.

Наиболее широко применяемы следующие цветовые модели:

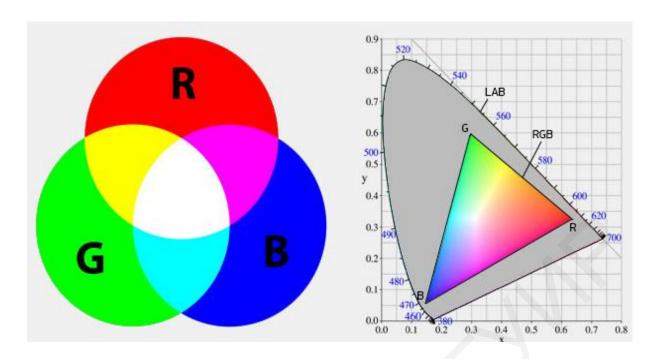

1 *RGB* — аддитивная (от англ. *add* — добавлять) цветовая модель, как правило, предназначенная для вывода изображения на экраны мониторов и другие электронные устройства. Состоит из синего, красного и зеленого цветов (аббревиатура английских слов *red*, *green*, *blue* — красный, зеленый, синий), которые образуют все промежуточные, и обладает большим цветовым охватом. Аддитивная цветовая модель предполагает, что вся палитра цветов складывается из светящихся точек, т. е. на бумаге, например, невозможно отобразить цвет в цветовой модели *RGB*, поскольку бумага цвет поглощает, а не светится сама по себе. Итоговый цвет можно получить, прибавляя к исходной черной (несветящейся) поверхности проценты от каждого из ключевых цветов.

Наглядная интерпретация данной модели приведена на рисунке 7.

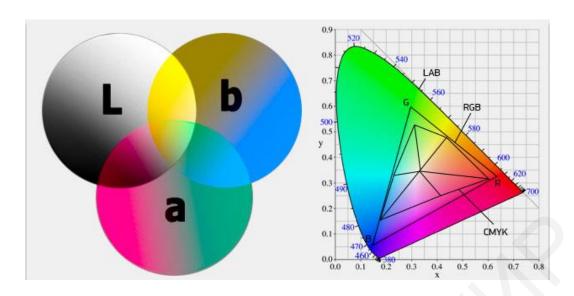

$2\,\textit{Lab}$  — цветовая модель, в которой значение светлоты отделено от значения хроматической составляющей цвета (тон, насыщенность). Светлота задана координатой L (изменяется от 0 до 100, т. е. от самого темного до самого светлого), хроматическая составляющая — двумя декартовыми координатами a и b. Первая обозначает положение цвета в диапазоне от зеленого до пурпурного, вторая — от синего до желтого.

Рисунок 7 – Изображение модели *RGB*

В отличие от цветовых пространств *RGB* или *CMYK*, которые являются, по сути, набором аппаратных данных для воспроизведения цвета на бумаге или на экране монитора (цвет может зависеть от типа печатной машины, марки красок, влажности воздуха на производстве или производителя монитора и его настроек), Lab однозначно определяет цвет. Поэтому Lab нашла широкое применение в программном обеспечении для обработки изображений в качестве промежуточного цветового пространства, через которое происходит конвертирование данных между другими цветовыми пространствами (например, из RGB сканера в СМҮК печатного процесса). При этом особые свойства Lab сделали редактирование в этом пространстве мощным инструментом цветокоррекции. Благодаря характеру определения цвета в *Lab* появляется возможность отдельно воздействовать на яркость, контраст изображения и на его цвет. Во многих случаях это позволяет ускорить обработку изображений, например, при допечатной подготовке. Lab предоставляет возможность избирательного воздействия на отдельные цвета в изображении, усилении цветового контраста. Незаменимыми являются и возможности, которые это цветовое пространство предоставляет для борьбы с шумом на цифровых фотографиях.

Наглядные данные модели *Lab* представлены на рисунке 8.

Рисунок 8 – Изображение модели *Lab*

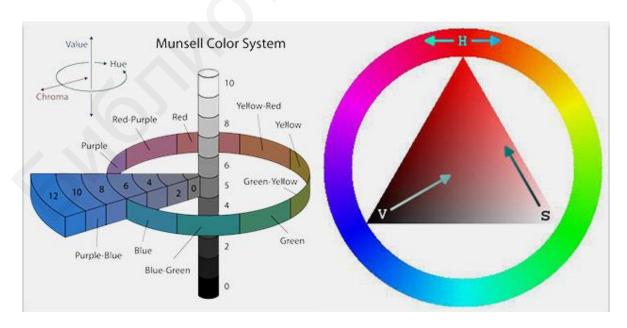

3 *HSB* — модель, которая в принципе является аналогом *RGB* и основана на ее цветах, но отличается системой координат. Любой цвет в этой модели характеризуется тоном (*Hue*), насыщенностью (*Saturation*) и яркостью (*Brightness*). Тон — это собственно цвет. Насыщенность — процент добавленной к цвету белой краски. Яркость — процент добавленной к цвету черной краски. *HSB* — трехканальная цветовая модель. Любой цвет в *HSB* получается добавлением к основному спектру черной или белой, т. е. фактически серой краски. В основе модели *HSB* лежит *RGB*. В любом случае *HSB* конвертируется в *RGB* для отображения на мониторе и в *CMYK* для печати, а любая конвертация не обходится без потерь.

Принцип формирования модели *HSB* показан на рисунке 9.

Рисунок 9 – Принцип формирования модели *HSB*

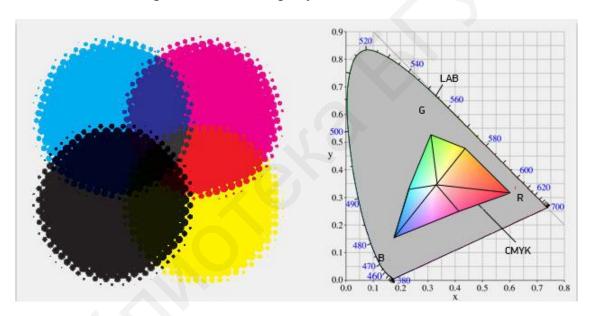

4 *CMYK* – *Cyan*, *Magenta*, *Yellow*, *Key color* – субтрактивная (от англ. *subtract* – вычитать) схема формирования цвета, используемая в полиграфии для стандартной триадной печати. Обладает меньшим, в сравнении с *RGB*, цветовым охватом. *CMYK* – субстрактивная модель, так как бумага и прочие печатные материалы являются поверхностями, отражающими свет.

Удобнее считать, какое количество света отразилось от той или иной поверхности, нежели сколько поглотилось. Таким образом, если вычесть из белого три первичных цвета *RGB*, то получится тройка дополнительных цветов *CMY*. Субтрактивный означает «вычитаемый» т. е. из белого вычитаются первичные цвета. *Key Color* (черный) используется в этой цветовой модели в качестве замены смешению в равных пропорциях красок триады *CMY*, поскольку только в идеальном варианте при смешении красок триады получается чистый черный цвет. На практике же он получится, скорее, грязно-коричневым — в результате внешних условий, впитываемости краски материалом и неидеальности красителей.

Модель СМҮК представлена на рисунке 10.

Рисунок 10 – Модель СМҮК

## 1.4 Периферийные устройства ЭВМ

Периферийные устройства (ПУ) ЭВМ – набор средств, непосредственно не входящих в центральную часть компьютера.

ПУ делятся:

- на устройства хранения данных;

- устройства ввода/вывода (мышь, клавиатура, монитор, принтер, сканер);

- коммуникационные устройства (сетевые платы, модемы, *Bluetooth*-адаптеры).

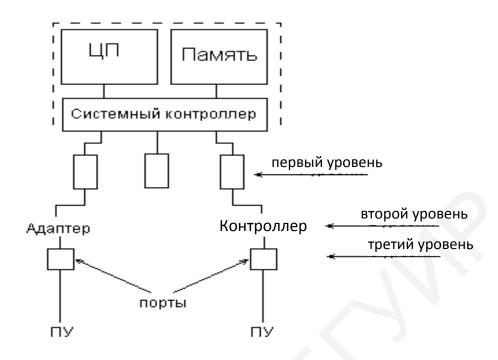

Между центральной частью ЭВМ и ПУ существует иерархическая система подключения (рисунок 11).

Рисунок 11 – Иерархическая система подключения ПУ

Центральная часть иерархии ЭВМ взаимодействует с ПУ через системный контроллер.

Верхним уровнем иерархии является шина расширения ввода/вывода. К шине расширения подключаются адаптеры и контроллеры.

Приведенные на рисунке 11 уровни являются интерфейсами, осуществляющими передачу информации между устройствами.

Существует множество ПУ различного назначения:

1 *Монитор* — устройство, через которое пользователь воспринимает всю визуальную информацию от компьютера. Данные, отображаемые на экране монитора, хранятся в определенном блоке памяти компьютера (видеопамять). Управляет работой монитора устройство, размещенное в системном блоке и называемое видеокартой или видеоадаптером. Видеокарта вместе с монитором образуют видеосистему. Процессор помещает в видеопамять данные, а видеокарта монитора просматривает данные и рисует соответствующее их содержанию изображение на экране. Сейчас наиболее широкое применение получили жидкокристаллические, или *LCD*-мониторы.

LCD-мониторы, выполняются на основе жидких кристаллов. Молекулы жидких кристаллов меняют свойства проходящего сквозь них светового луча, создавая таким образом на мониторе изображение. В LCD-мониторах отсутствует вредное электромагнитное излучение, а также такие устройства потребляют незначительное количество энергии.

2 **Принтеры** — печатающие устройства, работающие на основе разных физических принципов. Наиболее широко применяемые — лазерные принтеры, использование которых позволяет получать высокое качество печати.

- 3 *Манипулятор «мышь»* устройство ввода и управления информацией в ЭВМ. По принципу действия мыши делятся на оптико-механические и оптические. Оптические мыши отличаются высокой надежностью и точностью позиционирования на экране.

- 4 *Клавиатура* устройство ввода информации в ЭВМ. После нажатия клавиши клавиатура посылает процессору сигнал прерывания и заставляет процессор приостановить свою работу и переключиться на программу обработки прерывания клавиатуры. При этом клавиатура в своей собственной специальной памяти запоминает, какая клавиша была нажата. После передачи кода нажатой клавиши процессору эта информация из памяти клавиатуры исчезает.

- 5 *Сканер* устройство, выполняющее функции оцифровки и ввода в компьютер изображений с бумажных копий. Современные сканеры позволяют оцифровывать изображения даже объемных предметов и диапозитивов (слайдов).

- 6 *USB-накопитель на флэш-памяти* самое универсальное средство переноса информации, имеет небольшие габариты, высокую механическую прочность, относительно нечувствительно к электромагнитным излучениям и изменениям состояния окружающей среды, а также работает без наличия электропитания.

- 7 **Цифровая камера** формирует любые изображения сразу в компьютерном формате.

- 8 *Микрофон* осуществляет ввод звуковой информации, при этом звуковая карта преобразует звук из аналоговой формы в цифровую.

- 9 *Веб-камера* служит для ввода динамического изображения в компьютер и звука, например, для общения людей через телеконференции.

Сейчас, кроме вышеперечисленных, используется достаточно большое количество и других ПУ.

Для подключения к ЭВМ ПУ на системном блоке имеются разъемы различных портов:

- *COM* последовательный порт, передающий последовательно электрические импульсы, несущие информацию. К ним обычно подключают мышь и модем;

- *LPT* параллельный порт, передающий одновременно восемь электрических импульсов. Реализует более высокую скорость передачи информации;

- *USB* (*Universal Serial Bus*) последовательная универсальная шина, обеспечивающая высокоскоростное подключение нескольких ПУ (сканера, цифровой камеры и т. д.).

## 1.5 Интерфейс компьютерной системы

Информационный обмен между процессором и другими электронными компонентами ЭВМ осуществляется через интерфейс с использованием системных и локальных шин.

**Системная шина (СШ)** – это совокупность сигнальных линий, объединенных по их назначению (данные, адреса, управление).

По СШ осуществляется адресация устройств и происходит обмен специальными служебными сигналами. Передачей информации по шине управляет одно из подключенных к ней устройств или специально выделенный для этого узел, называемый арбитром шины.

Для работы с внешними устройствами в этой шине предусмотрены линии аппаратных прерываний ( $Interupt\ ReQuest-IRQ$ ) и линии для требования внешними устройствами прямого доступа в память ( $Direct\ Memory\ Access-DMA$ ). Для подключения плат расширения используются специальные разъемы.

**Локальные** (*local*) шины (ЛШ) непосредственно связывают процессор с контроллерами ПУ. В качестве ЛШ можно привести шины: *VL-bus* (*VLB*), предложенная ассоциацией *VESA* (*Video Electronics Standards Association*), и *PCI* (*Pe-ripheral Component Interconnect*), разработанная фирмой *Intel*. Обе эти шины были предназначены для увеличения быстродействия компьютера, позволяя таким ПУ, как видеоадаптеры и контроллеры накопителей, работать с тактовой частотой до 33 МГц и выше. Обе шины используют разъемы типа *MCA*.

Спецификация шины PCI обладает несколькими преимуществами перед основной версией VL-bus. Так, использовать PCI можно вне зависимости от типа процессора. Специальный контроллер заботится о разделении управляющих сигналов ЛШ процессора и PCI-шины и, кроме того, осуществляет арбитраж на PCI. Именно поэтому данная шина может использоваться и в иных компьютерных платформах. Гибкость и быстродействие этой шины предполагают и большие аппаратные затраты, чем для VL-bus. Тем не менее шина PCI стала практическим стандартом для систем на базе Pentium и не менее успешно используется в других компьютерах, даже и не PC-совместимых.

Шина *PCI* представляет собой мощное средство взаимодействия различных компонентов ПК, как расположенных внутри системного блока, так и находящихся за его пределами. Использование данной шины позволяет разделить различные функции, возложенные на чипсет материнской платы, на две группы. При этом имеет место интеграция одной группы функций в микросхему с названием *North bridge* (Северный мост). Другая группа функций была интегрирована (фирмой *Intel* и некоторыми из ее конкурентов) в микросхему под названием *South bridge* (Южный мост). Эти микросхемы соединяются шиной *PCI*.

## 1.6 Архитектура команд вычислительной системы

## 1.6.1 Формы представления данных

Наименьшая единица информации — двоичный разряд (нуль или единица), получивший название бит. Для представления символов в ЭВМ используется байт (восемь бит).

Наименьшей адресуемой структурной единицей информации в современных ЭВМ принят байт и байтовая организация информации в оперативной памяти.

Для представления в ЭВМ алфавитно-цифровой информации обычно применяется машинное слово, представляющее совокупность символов, которая извлекается из оперативной памяти или записывается в нее за одно обращение. Машинное слово обычно содержит целое число байтов, которые образуются последовательно, начиная с нуля.

В ЭВМ и микроЭВМ в качестве операндов используются следующие форматы данных: байт, полуслово, слово, двойные слово и поле — информационная единица переменной длины, но не более 256 байт. Это объясняется тем, что число возможных комбинаций допустимых значений нулей или единиц в одном байте равно  $2^8$ = 256 (от 0 до 255), т. е. максимально возможное двоичное число равно 1111 1111<sub>2</sub>. И в десятичном виде оно будет иметь следующее значение:

$$1111 \ 1111_2 = (1111 \ 1111_2 + 1) - 1 = 1000 \ 000 - 1 = 2^8 - 1 = 255.$$

Для микропроцессоров и микроЭВМ применяются форматы данных с длиной слова 4, 8, 12, 16, 32 и 64 бита. Побайтовая организация информации в памяти ЭВМ обеспечивает информационную совместимость форматов данных между различными микропроцессорами и микроЭВМ.

На рисунках 12 и 13 представлены форматы данных фиксированной и переменной длины соответственно.

| 0 /                 | 8 15 | 16 23     | 24 31 | 32 39     | 40 4/ | 48 55 | 56 63 |

|---------------------|------|-----------|-------|-----------|-------|-------|-------|

| Байт                | Байт | Байт      | Байт  | Байт      | Байт  | Байт  | Байт  |

| Полуслово Полуслово |      | Полуслово |       | Полуслово |       |       |       |

| Слово               |      |           | Слово |           |       |       |       |

| Двойное слово       |      |           |       |           |       |       |       |

Рисунок 12 – Формат данных фиксированной длины

| Байт | Байт | Байт | Байт | Байт | ••• | Байт |

|------|------|------|------|------|-----|------|

| 0    | 1    | 2    | 3    | 4    | ••• | 255  |

Рисунок 13 – Формат данных переменной длины

При размещении обрабатываемой информации в ЭВМ следует учитывать необходимость контроля ее обработки и адресации в ячейке оперативной памяти. Это вызывает определенные требования к организации разрядной сетки ЭВМ. Под разрядной сеткой ЭВМ понимают количество разрядов, необходи-

мых для размещения в ячейке оперативной памяти полного машинного слова. Для каждого типа ЭВМ она имеет строго определенное количество разрядов.

В ЭВМ используются две формы представления чисел в разрядной сетке:

- с фиксированной запятой (точкой) (ФЗ);

- с плавающей запятой (точкой) (ПЗ).

Представление с  $\Phi 3$  — это естественная форма представления числа, которая характеризуется тем, что положение его запятой в разрядной сетке всегда остается постоянным (фиксируется), независимо от величины самого числа. Обычно запятая фиксируется перед старшим или после младшего разряда. Если запятая фиксируется перед старшим разрядом, то числа в ЭВМ представляются как правильные дроби, если после младшего, то как целые числа.

При выполнении на ЭВМ вычислений необходимо, чтобы все исходные и получающиеся в процессе вычислений промежуточные и конечные данные не выходили за диапазон чисел, представимых в данной разрядной сетке. В противном случае в вычислениях могут возникнуть грубые ошибки. Для этого при программировании задачи данные, участвующие в вычислениях, берутся с соответствующими масштабными коэффициентами.

Использование представления чисел в ФЗ позволяет упрощать схемы ЭВМ, повысить ее быстродействие, но создает трудности при программировании. Первые ЭВМ были с ФЗ.

В настоящее время представление чисел с ФЗ используется как основное и единственное лишь в сравнительно небольших по своим вычислительным возможностям масштабах, применяемых для управления технологическими процессами и обработки измерительной информации в реальном масштабе времени.

В ЭВМ, предназначенных для решения широкого круга вычислительных задач, основным является представление чисел с плавающей запятой, поскольку оно не требует масштабирования данных. В ЭВМ форма с ПЗ используется при переполнении чисел ФЗ. Причем перевод выполняется автоматически по подпрограмме (микропрограмме).

В ЭВМ часто наряду с ПЗ используется и форма с ФЗ, поскольку операции с такими числами выполняются за меньшее время. При этом в большинстве случаев формат чисел с ФЗ служит для представления целых двоичных чисел (запятая фиксируется справа от младшего разряда числа) и выполнения операций над ними, что, в частности, необходимо для операций над кодами адресов (операции индексной арифметики).

```

Представление числа с ПЗ в общем случае имеет вид N=mr^{\pm p}, где m — мантисса числа N, \mid m\mid <1; p — порядок числа; r — основание c/c; r^{\pm p} — характеристика числа N.

```

Это представление числа называется также *полулогарифмическим*, так как часть числа — характеристика  $(r^p)$  выражена в логарифмической форме.

Мантисса числа *т* является правильной дробью.

Порядок числа p, который может быть положительным или отрицательным числом, определяет положение запятой в числе N:

$129,467=12,9467\cdot 10^{+1}=0,129467\cdot 10^{+3}=0,000129467\cdot 10^{+6}=12946,7\cdot 10^{-2}$ . Для двоичных чисел  $N=m\cdot 2^{\pm p}$ .

## 1.6.2 Семейство процессоров *Intel*

Первый микропроцессор *I*4004 был изготовлен в 1971 году, и с тех пор фирма *Intel* (*INTegrated ELectronics*) прочно удерживает лидирующее положение на данном сегменте рынка.

Реализация ряда проектов фирмы *Intel* по разработке однокристальных микропроцессоров (*i*4040, *i*8008) возвестила о наступлении эры персональных компьютеров. Наиболее успешным был, пожалуй, проект разработки микропроцессора *i*8080. Именно на этом микропроцессоре был основан компьютер «Альтаир», для которого молодой Билл Гейтс написал свой первый интерпретатор Бейсика. Он был выполнен по *n*-канальной МОП-технологии (*n-MOS*), а его тактовая частота не превышала 2 МГц. Классическая архитектура *i*8080 оказала огромное влияние на дальнейшее развитие однокристальных микропроцессоров. Несмотря на заслуженный успех *i*8080, настоящим промышленным стандартом для персональных компьютеров стал другой микропроцессор фирмы *Intel*.

Микропроцессор *i*8088 был анонсирован *Intel* в июне 1979 года, а в 1981 году фирма *IBM*, выбрала этот микропроцессор для своего первого ПК. Новый чип содержал примерно 29 тыс. транзисторов. Одним из существенных достоинств микропроцессора *i*8088 была возможность (благодаря 20 адресным линиям) физически адресовать область памяти в 1 Мбайт. Для *IBM PC* в этом пространстве программам было отведено всего лишь 640 Кбайт.

Хотя с внешними периферийными устройствами (дисками, видео) *i*8088 был связан через свою внешнюю 8-разрядную шину данных, его внутренняя структура (адресуемые регистры) позволяла работать с 16-разрядными словами. Как известно, на системной шине *IBM PC* для передачи данных было отведено восемь линий (1 байт). Первоначально микропроцессор *i*8088 работал на частоте 4,77 МГц и имел быстродействие около 0,33 *MIPS* (*MillionInstruction-PerSecond*), однако впоследствии были разработаны его модификации, рассчитанные на более высокую тактовую частоту (например, 8 МГц).

В июне 1978 года появился процессор **i8086**, ставший популярным в основном благодаря компьютеру *Compaq Desk Pro*. Программная модель (доступные регистры) этого микропроцессора полностью совпадала с моделью *i*8088. Основное отличие данных микропроцессоров состоит в различной разрядности внешней шины данных: 8 разрядов у *i*8088 и 16 разрядов у *i*8086. Понятно, что более высокой производительности с новым микропроцессором можно было достичь только

при использовании компьютера, на системной шине которого под данные предусмотрено 16 линий. Адресная шина микропроцессора *i*8086 по-прежнему позволяла адресовать 1 Мбайт памяти.

Опираясь на архитектуру i8086 и учитывая запросы рынка, фирма *Intel* в феврале 1982 года выпустила свой новый микропроцессор — i80286. На кристалле было реализовано около 130 тыс. транзисторов. Надо сказать, что этот чип появился практически одновременно с новым компьютером фирмы *IBM PC/AT*. Наряду с увеличением производительности этот микропроцессор (i80286) мог теперь работать в двух режимах: реальном и защищенном. Если первый режим был (за рядом исключений) похож на обычный режим работы і8088/86, то второй использовал более изощренную технику управления памятью. В частности, защищенный режим работы позволял, например, таким программным продуктам, как Windows 3.0 и OS/2, работать с оперативной памятью выше 1 Мбайта. Благодаря 16 разрядам данных на новой системной шине, которая была впервые использована в ІВМ РС/АТ286, микропроцессор і80286 мог обмениваться с периферийными устройствами 2-байтными сообщениями. 24 адресные линии позволяли в защищенном режиме обращаться уже к 16 Мбайтам памяти. В микропроцессоре і80286 впервые на уровне микросхем были реализованы мультизадачность и управление виртуальной памятью. При тактовой частоте 8 МГц достигалась производительность 1,2 MIPS.

В октябре 1985 года фирмой *Intel* был анонсирован первый 32-разрядный микропроцессор *i*80386. Новый чип содержал примерно 275 тыс. транзисторов. Полностью 32-разрядная архитектура (32-разрядные регистры и 32-разрядная внешняя шина данных) в новом микропроцессоре была дополнена расширенным устройством управления памятью *MMU* (*Memory Management Unit*), которое помимо блока сегментации (*Segmentation Unit*) было дополнено блоком управления страницами (*Paging Unit*). Это устройство позволяло легко переставлять сегменты из одного места памяти в другое (свопинг) и освобождать драгоценные килобайты памяти. На тактовой частоте 16 МГц быстродействие нового процессора составило примерно 6 *MIPS*.

В реальном режиме (после включения питания) микропроцессор *i*80386 работал как «быстрый *i*8088» (адресное пространство 1 Мбайт, 16-разрядные регистры). Защищенный режим был полностью совместим с аналогичным режимом в *i*80286. Тем не менее в этом же режиме *i*80386 мог выполнять и свои «естественные» (*native*) 32-разрядные программы. Вспомним, что 32 адресные линии микропроцессора позволяют физически адресовать 4 Гбайта памяти. Кроме того, был введен новый режим виртуального процессора (*V*86). В этом режиме могли одновременно выполняться несколько задач, предназначенных для *i*8086.

Более дешевая альтернатива 32-разрядному процессору i80386, который впоследствии получил окончание DX, появилась только в июне 1988 года. Это был микропроцессор i80386SX. В отличие от своего старшего «собрата» новый микропроцессор использовал 16-разрядную внешнюю шину данных и 24-разрядную адресную (адресуемое пространство 16 Мбайт). Это было особенно удобно для

стандартных *PC/AT*, системная шина которых использует, как известно, только 16 линий данных. Благодаря дешевизне нового изделия многие производители аппаратных средств стали заменять теперь уже устаревший микропроцессор *i*80286 на более производительный *i*80386*SX*. Одним из решающих факторов для замены была полная совместимость 32-разрядных микропроцессоров: программное обеспечение, написанное для *i*80386*DX*, корректно работало и на *i*80386*SX*. Дело в том, что внутренние регистры их были полностью идентичны. К концу 1988 года микропроцессор *i*80386*SX* выпускался в количествах, существенно превосходящих рекордные показатели для *i*80386*DX*. Кстати, считается, что индекс *SX* произошел от слова *SiXteen* (шестнадцать), поскольку разрядность внешней шины данных нового тогда процессора была именно такой. В дальнейшем, правда, для 486-х процессоров *SX* стал означать отсутствие математического сопроцессора.

В 1989 году фирма *Intel* впервые анонсировала микропроцессор *i*486DX, который содержал более миллиона транзисторов (а точнее, 1,2 млн) на одном кристалле и был полностью совместим с процессорами ряда x86. Напомним, что на кристалле первого члена этого семейства – микропроцессора і8088 – насчитывалось около 29 тыс. транзисторов. В борьбе с «микропроцессорами-клонами» фирма Intel намеренно убрала из названия нового устройства число 80. Новая микросхема впервые объединила на одном чипе такие устройства, как центральный процессор, математический сопроцессор и кэш-память. Использование конвейерной архитектуры, присущей RISC-процессорам, позволило достичь четырехкратной производительности обычных 32-разрядных систем. Это связано с уменьшением количества тактов для реализации каждой команды. Встроенная кэш-память 8 Кбайт ускоряет выполнение программ за счет промежуточного хранения часто используемых команд и данных. На тактовой частоте 25 МГц микропроцессор показал производительность 16,5 MIPS. Созданная в июне 1991 года версия микропроцессора с тактовой частотой 50 МГц позволила увеличить производительность еще на 50 %. Встроенный математический сопроцессор существенно облегчил и ускорил математические вычисления. Однако впоследствии стало ясно, что подобный сопроцессор необходим всего лишь 30 % пользователей.

Появление нового микропроцессора *i486SX* фирмы *Intel* вполне можно было считать одним из важнейших событий 1991 года. Уже предварительные испытания показали, что компьютеры на базе *i486SX* с тактовой частотой 20 МГц работают быстрее (примерно на 40 %) компьютеров, основанных на *i80386DX* с тактовой частотой 33 МГц. Микропроцессор *i486SX*, подобно оригинальному *i486DX*, содержал на кристалле кэш-контроллер и кэш-память, а вот математический сопроцессор у него был заблокирован. Значительная экономия (благодаря исключению затрат на тестирование сопроцессора) позволила фирме *Intel* существенно снизить цены на новый микропроцессор. Если микропроцессор *i486DX* был ориентирован на применение в сетевых серверах и рабочих станциях, то *i80486SX* послужил отправной точкой для создания мощных настольных компьютеров.

В семействе микропроцессоров *i*486 предусматривалось несколько новых возможностей для построения мультипроцессорных систем: соответствующие

команды поддерживают механизм семафоров памяти, аппаратно реализованное выявление недостоверности строки кэш-памяти обеспечивает согласованность между несколькими модулями кэш-памяти и т. д. Для микропроцессоров семейства *i*486 допускалась адресация физической памяти размером 4 Гбайта и виртуальной памяти размером 64 Тбайта.

К концу 1991 года 32-разрядные микропроцессоры стали стандартными для компьютеров типа лэптоп и ноутбук, однако обычные микросхемы i80386DX/SX не полностью отвечали требованиям разработчиков портативных компьютеров. Для удовлетворения потребностей этого сегмента рынка фирмой *Intel* в 1990 году был разработан микропроцессор *i*80386SL, который содержал примерно 855 тыс. транзисторов. Данный микропроцессор представлял собой интегрированный вариант микропроцессора і80386SX, базовая архитектура которого была дополнена еще несколькими вспомогательными контроллерами. По существу, все компоненты, необходимые для построения портативного компьютера, сосредоточены в двух микросхемах: микропроцессоре i80386SL и периферийном контроллере i82360SL. В набор i386SL впервые было введено новое прерывание, называемое System Management Interrupt (SMI), которое использовалось для обработки событий, связанных, например, с управлением потребляемой мощности. Вместе с математическим сопроцессором i80387SL данный набор микросхем позволял создать 32-разрядный компьютер на площади, ненамного превышающей размер игральной карты.

## 1.6.3 Конвейерное выполнение команды

Для повышения производительности процессора при выполнении операций его операционное устройство (ОУ) может строиться по блочному принципу. В таких блочных ОУ реализуется несколько функционально независимых исполнительных устройств, выполняющих различные операции (или различные группы операций, например: три блока целочисленного сложения, два — целочисленного умножения, по одному блоку деления, сложения и умножения с плавающей запятой и т. д.).

Эти устройства работают параллельно: каждое обрабатывает свои операнды.

Управление этими устройствами осуществляется с помощью так называемых длинных командных слов ( $Very\ Long\ Instruction\ Word\ -\ VLIW$ ). Командные слова включают инструкции для каждого из исполнительных устройств, а также операнды или указатели на них.

Преимуществом блочных ОУ является более высокая производительность, достигаемая за счет распараллеливания вычислений. В то же время использование таких устройств не всегда эффективно, поскольку не всегда есть возможность загрузить все исполнительные устройства в каждом такте, в результате часть из них простаивает.

Более эффективными часто оказываются конвейерные операционные устройства, поскольку конвейеризовать вычисления в ряде случаев проще, чем распараллелить, что связано с повторением однотипных вычислений в алгоритмах.

Для конвейеризации вычислений необходимо:

- разбить вычисления на последовательность одинаковых по времени этапов;

- реализовать каждый этап аппаратно в виде ступени конвейера;

- обеспечить фиксацию промежуточных результатов вычислений на выходе каждой ступени в регистрах-защелках.

Эффективность конвейера будет тем выше, чем больше задач будет поступать на его вход.

Типичным примером конвейерных операционных устройств могут служить матричные умножители, включающие матрицу операционных элементов (сумматоров) и применяемые в основном для умножения матриц.

## 1.6.4 Архитектура системы команд *RISC* и *CISC* процессоров

Под архитектурой системы команд (*Instruction Set Architecture – ISA*) понимают состав и возможности системы команд (СК), общий взгляд на СК и связанную с ней микроархитектуру процессора с точки зрения программиста. Во многом именно архитектура СК определяет трактовку архитектуры компьютера вообще, как «...абстрактного представления о вычислительной машине с точки зрения программиста».

Исторически первые микропроцессоры, появившиеся в 70-х годах прошлого века, имели относительно простую систему команд, что объяснялось небольшими возможностями интегральной схемотехники. По мере увеличения степени интеграции ИМС разработчики микропроцессоров (МП) старались расширять систему команд и делать команды более функциональными, «семантически нагруженными». Это объяснялось, в частности, двумя моментами:

- во-первых, требованиями экономить память для размещения программ, оставлять больше памяти под данные и т. д.;

- во-вторых, возможностью реализовать внутри кристалла процессора сложные инструкции быстрее, чем при их программной реализации.

В результате появились процессоры с большими наборами команд, причем команды эти также зачастую являлись достаточно сложными. Впоследствии эти МП назвали *CISC* (*Complete Instruction Set Computer* – компьютер с полным набором команд или *Complex ISC* – со сложным набором команд).

Типичным примером CISC-процессоров являются процессоры семейства x86 корпорации Intel и ее конкурентов (а также Motorola~68K и др.).

Наряду с отмеченными преимуществами процессоры *CISC* обладали и рядом недостатков. В частности, команды оказывались сильно неравнозначны-

ми по времени выполнения (разное количество тактов), плохо конвейеризовывались, требовали сложного и длительного декодирования и выполнения.

Для повышения производительности стали использовать жесткую логику управления, что отразилось на регулярности и сложности кристаллов (нерегулярные кристаллы менее технологичны при изготовлении). На кристалле оставалось мало места для регистров общего назначения (РОН) и кэш-памяти.

Кроме того, исследования показали, что производители компиляторов и просто программисты не используют многие сложные инструкции, предпочитая использовать последовательность коротких.

Разработчики подошли к концепции более простого и технологичного процессора с некоторым возвратом назад к простым и коротким инструкциям. С конца 70-х до середины 80-х годов появляются проекты таких процессоров Стэнфордского университета и университета Беркли (Калифорния) – *MIPS* и *RISC*.

В основу архитектуры RISC (Reduced Instruction Set Computer – компьютер с сокращенным набором команд) положены, в частности, принципы отказа от сложных и многофункциональных команд, уменьшения их количества, а также концентрация на обработку всей информации преимущественно на кристалле процессора с минимальными обращениями к памяти.

Основные особенности архитектуры RISC:

- уменьшение числа команд (до 30–40);

- упрощение и унификация форматов команд;

- в системе команд преобладают короткие инструкции (например, часто в СК отсутствуют умножения);

- отказ от команд типа «память память» (например, MOVSB в x86);

- работа с памятью сводится к загрузке и сохранению регистров (поэтому другое название *RISC Load-Store Architecture*, т. е. архитектура типа «загрузка сохранение»);

- преимущественно реализуются трехадресные команды, например: add r1, r2, r3 значит, сложить r2 с r3 и поместить результат в r1;

- большой регистровый файл до 32-64 РОН;

- предпочтение отдается жесткой логике управления.

Достоинства архитектуры RISC:

- облегчается конвейерная, суперскалярная и другие виды параллельной обработки, планирование загрузки, переупорядочивание, предвыборка и т. д.;

- более эффективно используется площадь кристалла (больше памяти: POH, кэш);

- быстрее выполняется декодирование и исполнение команд, что приводит к повышению тактовой частоты.

Примерами семейств процессоров с RISC-архитектурой могут служить  $DEC\ Alpha$ ,  $SGI\ MIPS$ ,  $Sun\ SPARC$  и др. Большинство современных суперскалярных и VLIW-процессоров (в том числе и Intel) либо имеют архитектуру RISC, либо реализуют похожие на RISC принципы, либо поддерживают

*CISC*-инструкции, но внутри транслируют их в *RISC*-подобные команды для облегчения загрузки конвейеров и решения других задач.

## 1.7 Центральный процессор вычислительной машины

Процессор — центральное устройство компьютера. Он выполняет находящиеся в оперативной памяти команды программы и «общается» с внешними устройствами благодаря шинам адреса, данных и управления, выведенными на специальные контакты корпуса микросхемы.

К обязательным компонентам процессора относятся арифметико-логическое (исполнительное) устройство (АЛУ) и устройство управления (УУ).

Выполнение процессором команды предусматривает:

- арифметические действия;

- логические операции;

- передачу управления (условную и безусловную);

- перемещение данных из одного места памяти в другое;

- координацию взаимодействия различных устройств ЭВМ.

Выделяют четыре этапа обработки команды процессором:

- 1) выборка;

- 2) декодирование;

- 3) выполнение и запись результата.

В ряде случаев пока первая команда выполняется, вторая может декодироваться, а третья – выбираться.

Функции процессора:

- 1) обработка данных по заданной программе путем выполнения логических и арифметических операций;

- 2) программное управление работой устройств компьютера.

Процессор состоит из ячеек. В ячейках процессора данные не хранятся, а обрабатываются. Во время обработки они могут изменяться самыми разными способами. Ячейки процессора называются регистрами.

Регистр выполняет функцию кратковременного хранения числа или команды. Над содержимым некоторых регистров специальные электронные схемы могут выполнять некоторые манипуляции. Например, «вырезать» отдельные части команды для последующего их использования или выполнять определенные арифметические операции над числами. Основным элементом регистра является электронная схема, называемая триггером, которая способна хранить одну двоичную цифру (разряд).

Разные регистры процессора имеют разное назначение:

- регистры общего назначения используются для операций с данными (байтами, словами и двойными словами);

- адресные регистры служат для хранения в них адресов, по которым процессор находит данные в памяти;

- существуют специальные регистры для самопроверок процессора;

– биты флагового регистра служат как бы флажками, которые включаются или выключаются в особых случаях. Когда от меньшего числа отнимают большее, то занимают одну единицу в старшем разряде. На этот случай во флаговом регистре есть специальный флажок, который включается при таком событии. Существуют флажки, включающиеся при переполнении регистров или их обнулении, а также еще несколько специальных флажков.

Некоторые важные регистры имеют свои названия, например:

- сумматор регистр АЛУ, участвующий в выполнении каждой операции;

- счетчик команд регистр УУ, содержимое которого соответствует адресу очередной выполняемой команды. Служит для автоматической выборки программы из последовательных ячеек памяти;

- регистр команд регистр УУ для хранения кода команды на период времени, необходимый для ее выполнения. Часть его разрядов используется для хранения кода операции, остальные для хранения кодов адресов операндов.

У компьютеров четвертого поколения функции центрального процессора выполняет микропроцессор — сверхбольшая интегральная схема (СБИС), реализованная в едином полупроводниковом кристалле (кремния или германия) площадью меньше  $0,1~{\rm cm}^2$ .

Микропроцессоры различаются рядом важных характеристик:

- тактовой частотой обработки информации;

- разрядностью;

- интерфейсом с системной шиной;

- адресным пространством (адресацией памяти).

Тактовая частота обработки информации. Тактом называют интервал времени между началом подачи двух последовательных импульсов электрического тока, синхронизирующих работу различных устройств компьютера. Специальные импульсы для отсчета времени для всех электронных устройств вырабатывает тактовый генератор частоты, расположенный на системной плате. Его главный элемент представляет собой кристалл кварца, обладающий стабильностью резонансной частоты. Тактовая частота определяется как количество тактов в секунду и измеряется в мегагерцах (1 МГц = 1 млн тактов/с). Тактовая частота влияет на скорость работы, быстродействие микропроцессора. Переход к микропроцессору с большей тактовой частотой означает скорое повышение обработки информации.

Быстродействие процессора определяется количеством операций, выполняемых им в секунду.

Один из способов повышения быстродействия микропроцессора — использование кэш-памяти. Это позволяет избежать циклов ожидания в работе МП, пока информация из соответствующих схем памяти установится на системной шине данных компьютера. Таким образом, кэш-память функционально предназначена для согласования скорости работы сравнительно медленных устройств с относительно быстрым микропроцессором.

Для улучшения показателей при выполнении операций с плавающей запятой создано и используется специальное устройство — математический сопроцессор, выполненный в виде интегральной схемы, работающей во взаимодействии с центральным микропроцессором и предназначенной только для выполнения математических операций.

Разрядность процессора — это число одновременно обрабатываемых процессором битов, т. е. количество внутренних битовых (двоичных) разрядов — важнейший фактор производительности микропроцессора.

Процессор может быть 8-, 16-, 32- и 64-разрядным. Разрядность характеризует объем информации, перерабатываемый процессором компьютера за единицу времени.

Интерфейс с системной шиной — разрядность внутренней шины данных микропроцессора может не совпадать с количеством внешних выводов для линии данных. Например, микропроцессор с 32-разрядной внутренней шиной данных может иметь только 16 внешних линий данных. Это означает, что разрядность интерфейса с внешней шиной данных равна 16. Аналогичная ситуация может наблюдаться с другой частью системной шины — адресной шиной.

Выполнение процессором команды предусматривает наряду с арифметическими действиями и логическими операциями передачу управления и перемещение данных из одного места памяти в другое.

Поэтому важна не только разрядность внутренних шин процессора, но и его интерфейс с системной шиной.

Адресное пространство (адресация памяти) — одна из функций процессора, которая состоит в перемещении данных, в организации их обмена с ПУ и оперативной памятью. При этом процессор формирует код устройства, а для O3У — адрес ячейки памяти. Код адреса передается по адресной шине. Объем физически адресуемой микропроцессором оперативной памяти называется его адресным пространством, которое определяется разрядностью внешней шины адреса. Если N — разрядность адресной шины, то количество различных двоичных чисел, которые можно по ней передать, равно 2.

Число, передаваемое по адресной шине при обращении процессора к оперативной памяти, есть адрес ячейки ОЗУ (ее порядковый номер). Значит,  $2^N$  – это количество ячеек оперативной памяти, к которым, используя адресную шину, может обратиться (адресоваться) процессор, т. е.  $2^N$  – объем адресного пространства процессора. Следовательно, при 16-, 20-, 24- или 32-разрядной шине адреса создается адресное пространство соответственно  $2^{16}$  = 64 Кбайта,  $2^{20}$  = 1 Мбайт,  $2^{24}$  = 16 Мбайт,  $2^{32}$  = 4 Гбайта.

## 1.7.2 Суперскалярные архитектуры процессоров ЭВМ

Использование конвейера команд позволяет в лучшем случае снизить показатель производительности *CPI* до 1, т. е. на каждом такте с конвейера должна «сходить» новая обработанная команда. В этом случае производительность процессора должна увеличиться в четыре раза, при его длительности такта в 10 нс (тактовая частота 100 МГц) имеем производительность в 100 MIPS. Но, вопервых, у Celeron такой показатель равен примерно 250, а во-вторых, достижение показателя 1 CPI не всегда возможно из-за конфликтов при конвейеризации. В действительности в лучшем случае будет 1,5-2 CPI.

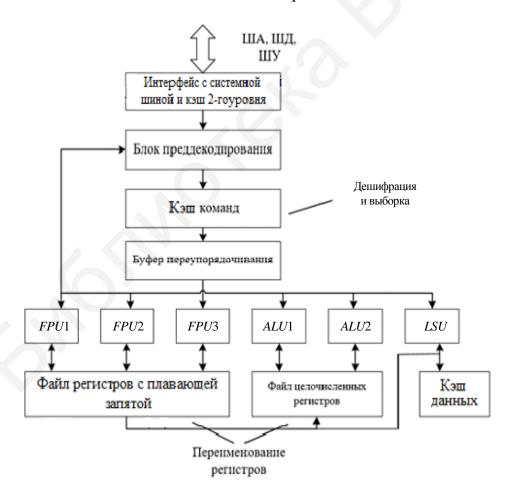

Для достижения такой высокой производительности в *Celeron* и других процессорах с архитектурой Р6 используется суперскалярная обработка, т. е. обработка с многопотоковым конвейером команд, когда процессор выполняет больше одной команды за такт.

Фактически в суперскалярном процессоре несколько потоков проходят через несколько исполнительных устройств, а остальные ступени так или иначе работают с одним потоком. Для согласования разных скоростей потоков декодирования, выборки, трансляции в RISC-подобные инструкции, переупорядочивания и потоков в исполнительных устройствах применяют различные очереди инструкций (буферы FIFO), которые есть у каждого из исполнительных устройств.

В процессорах с длинным командным словом (*Very Long Instruction Word*) (рисунок 14) используется альтернативный суперскалярной обработке принцип распараллеливания последовательного алгоритма.

Рисунок 14 – Структура процессора с длинным командным словом *VLIW*

В основном вся тяжесть планирования загрузки большого числа исполнительных устройств в таком процессоре (а у него блочное операционное устройство) ложится на программиста или оптимизирующий компилятор. В процессор поступают уже сформированные триады для всех исполнительных устройств, так что ему только остается выполнять эти длинные команды. В результате он не ограничен размером окна исполнения, так как и программист, и компилятор видят весь код программы и могут извлечь из него максимальный параллелизм.

Такой подход позволяет достичь принципиально более высокой производительности (например, тестирование процессоров *Itanium* с архитектурой IA-64, использующей принципы VLIW, указывает на 10-кратное ускорение при выполнении ряда вычислений).

Но такие процессоры обладают и рядом недостатков:

- загрузка исполнительных устройств в целом менее эффективная, так как не всегда можно сформировать достаточное количество команд для параллельного исполнения;

- сложности обработки условных переходов;

- сложность программирования и др.

Последнее обстоятельство ограничивает применение процессоров VLIW, даже Intel, в ПК, так как для этого придется кардинально переписывать все программное обеспечение, поскольку в существующем виде оно не даст прироста производительности на этих процессорах.

Сфера применения *VLIW*-процессоров пока ограничена серверами, производительными рабочими станциями, а также многопроцессорными ЭВМ.

Необходимо отметить, что в суперскалярных процессорах происходит очень сложное и нетривиальное преобразование последовательного потока команд исходной программы в параллельный поток триад «операция + операнды + назначение результата», параллельно продвигающихся по очередям команд в исполнительные устройства.

Процессор ограничен в возможностях такого преобразования, а также в возможностях спекулятивного исполнения (подготовки загрузки альтернативных ветвей ветвления) и прогнозирования ветвлений размером так называемого «окна исполнения», т. е. той частью программного кода, который процессор «видит» в процессе выполнения в данном такте. Все это ограничивает возможности распараллеливания потоков команд до величин порядка 6–8.

## 1.8 Тенденции развития вычислительной техники

Тенденции развития вычислительной техники следующие:

- переход от отдельных ЭВМ к многофункциональным вычислительным системам и комплексам с широким спектром характеристик, параметров и конфигураций;

- дальнейшее развитие систем телекоммуникаций;

- оптимальная организация использования ресурсов сети Интернет;

- оптимизация характеристик и параметров суперкомпьютеров и ПК;

- разработка и применение микропроцессоров с быстродействием не менее 1000 *MIPS* и встроенной памятью 16 Мбайт;

- разработка и применение встроенных беспроводных сетевых и видеоинтерфейсов;

- разработка и применение тонких крупноформатных дисплеев с высокой разрешающей способностью;

- разработка миниатюрных магнитных дисков огромной емкости, применение которых позволит сделать ненужным стирание старой информации;

- широкое использование широкополосных мультиканальных радио-, волоконно-оптических и оптических каналов обмена информацией между ЭВМ для обеспечения достаточно большой пропускной способности;

- широкое внедрение средств мультимедиа, например видео- и аудиосредств ввода и вывода информации, для решения задач в различных сферах человеческой деятельности;

- дальнейшее развитие компьютерных систем искусственного интеллекта и робототехники для их использования в различных областях человеческой деятельности.

## 1.9 Содержание задания №1

В таблице 1 представлены номера вопросов, составляющих контрольное задание для каждого варианта.

Таблица 1 – Номера вопросов для каждого из вариантов задания №1

| Номер варианта | Номера вопросов | Номер варианта | Номера вопросов |

|----------------|-----------------|----------------|-----------------|

| 1              | 15, 32          | 16             | 17, 47          |

| 2              | 8, 43           | 17             | 34, 56          |

| 3              | 5, 33           | 18             | 18, 41          |

| 4              | 9, 40           | 19             | 23, 42          |

| 5              | 6, 48           | 20             | 25, 37          |

| 6              | 11, 45          | 21             | 27, 36          |

| 7              | 30, 59          | 22             | 19, 32          |

| 8              | 3, 54           | 23             | 20, 38          |

| 9              | 7, 58           | 24             | 35, 53          |

| 10             | 4, 44           | 25             | 24, 57          |

| 11             | 29, 52          | 26             | 21, 51          |

| 12             | 13, 31          | 27             | 22, 55          |

| 13             | 2, 46           | 28             | 28, 50          |

| 14             | 14, 26          | 29             | 12, 39          |

| 15             | 10, 16          | 30             | 1, 60           |

## 1.10 Вопросы к заданию №1

- 1 Эволюция вычислительных машин.

- 2 Неймановская и гарвардская архитектуры, сравнение архитектур.

- 3 Принципы построения фон-неймановской архитектуры.

- 4 Поколения ЭВМ.

- 5 Конвергенция вычислительных систем и систем мобильной связи.

- 6 Элементы и узлы ЭВМ.

- 7 Мультиплексор, дешифратор, компаратор, сумматор. Назначение и функциональные возможности.

- 8 Операция сдвига, счетчик на синхронном триггере.

- 9 Реализация операции умножения целых чисел.

- 10 Форматы хранения информации. Системы счисления.

- 11 Форматы хранения графических изображений. Хранение векторных изображений.

- 12 Форматы хранения графических изображений. Хранение растровых изображений.

- 13 Цветовые модели. Модель *RGB*.

- 14 Цветовые модели. Модель Lab.

- 15 Цветовые модели. Модель *HSB*.

- 16 Цветовые модели. Модель СМҮК.

- 17 Периферийные устройства ЭВМ. Классификация периферийных устройств.

- 18 Иерархическая система подключения периферийных устройств к ЭВМ.

- 19 Периферийные устройства ЭВМ. Мониторы, классификация, назначение и принципы функционирования.

- 20 Периферийные устройства ЭВМ. Принтеры, классификация, назначение и принципы функционирования.

- 21 Периферийные устройства ЭВМ. Клавиатура, назначение и принципы функционирования.

- 22 Периферийные устройства ЭВМ. Манипулятор «мышь», назначение и принципы функционирования.

- 23 Периферийные устройства ЭВМ. Сканер, назначение и принципы функционирования.

- 24 Периферийные устройства ЭВМ. *USB*-накопитель на флэш-памяти, назначение и принципы функционирования.

- 25 Периферийные устройства ЭВМ. Цифровая камера, назначение и принципы функционирования.

- 26 Периферийные устройства ЭВМ. Микрофон и веб-камера, назначение и принципы функционирования.

- 27 Порты ЭВМ, их классификация, назначение и функциональные возможности.

- 28 Интерфейс компьютерной системы. Системная шина, назначение и принципы функционирования.

- 29 Интерфейс компьютерной системы. Локальная шина, назначение и принципы функционирования.

- 30 Формы представления данных. Форматы данных фиксированной длины.

- 31 Формы представления данных. Форматы данных переменной длины.

- 32 Семейство процессоров *Intel*. Микропроцессор *i*8080, архитектура и функциональные возможности.

- 33 Семейство процессоров *Intel*. Микропроцессор *i*8088, архитектура и функциональные возможности.

- 34 Семейство процессоров *Intel*. Микропроцессор *i*8086, архитектура и функциональные возможности.

- 35 Семейство процессоров *Intel*. Микропроцессор *i*80286, архитектура и функциональные возможности.

- 36 Семейство процессоров *Intel*. Микропроцессор *i*80386, архитектура и функциональные возможности.

- 37 Семейство процессоров *Intel*. Микропроцессор *i*80386*SX*, архитектура и функциональные возможности.

- 38 Семейство процессоров *Intel*. Микропроцессор *i*80386*DX*, архитектура и функциональные возможности.

- 39 Семейство процессоров *Intel*. Микропроцессор i486DX, архитектура и функциональные возможности.

- 40 Семейство процессоров *Intel*. Микропроцессор *i*486*SX*, архитектура и функциональные возможности.

- 41 Семейство процессоров *Intel*. Микропроцессор *i*80486*SX*, архитектура и функциональные возможности.

- 42 Семейство процессоров Intel. Микропроцессор i80386SL, архитектура и функциональные возможности.

- 43 Семейство процессоров *Intel*. Математический сопроцессор i80387SL, архитектура и функциональные возможности.

- 44 Конвейерное выполнение команды в процессоре ЭВМ. Блочное операционное устройство, назначение, архитектура и функциональные возможности.

- 45 Конвейерное выполнение команды в процессоре ЭВМ. Конвейерное операционное устройство, назначение, архитектура и функциональные возможности.

- 46 Архитектура системы команд *RISC*-процессоров, назначение и функциональные возможности.

- 47 Архитектура системы команд *CISC*-процессоров, назначение и функциональные возможности.

- 48 Центральный процессор вычислительной машины, назначение и принципы функционирования.

- 49 Суперскалярные архитектуры процессоров ЭВМ, назначение и функциональные возможности.

- 50 Процессор с длинным командным словом *VLIW*, назначение, структурные решения и функциональные возможности.

- 51 Алгоритм сжатия рисунков, функциональные возможности.

- 52 Коды *ASC*II и *Unicode* для символов, назначение и функциональные возможности.

- 53 Многоядерные вычислительные системы, назначение, архитектура и функциональные возможности.

- 54 Кластерные системы, назначение, архитектура и функциональные возможности.

- 55 Видеокарта, назначение, архитектура и функциональные возможности.

- 56 Видеопроцессор, назначение, архитектура и функциональные возможности.

- 57 Технология *DMA*, назначение и функциональные возможности.

- 58 Процессор *Itanium*, назначение, архитектура и функциональные возможности.

#### 2 Задание №2

Краткие сведения по теоретическим основам организации памяти современных ЭВМ и систем

## 2.1 Организация памяти вычислительной системы

## 2.1.1 Виды памяти вычислительной системы

**Компьютерная память** (устройство хранения информации, запоминающее устройство) — часть вычислительной машины, физическое устройство или среда для хранения данных, используемых в вычислениях, в течение определенного времени. Память в вычислительных устройствах имеет иерархическую структуру и обычно предполагает использование нескольких запоминающих устройств, имеющих различные характеристики.

Любая информация может быть измерена в битах и потому, независимо от того, на каких физических принципах и в какой системе счисления функционирует цифровой компьютер (двоичной, троичной, десятичной и т. п.), числа, текстовая информация, изображения, звук, видео и другие виды данных можно представить последовательностями битовых строк или двоичными числами. Это позволяет компьютеру манипулировать данными при условии достаточной емкости системы хранения.

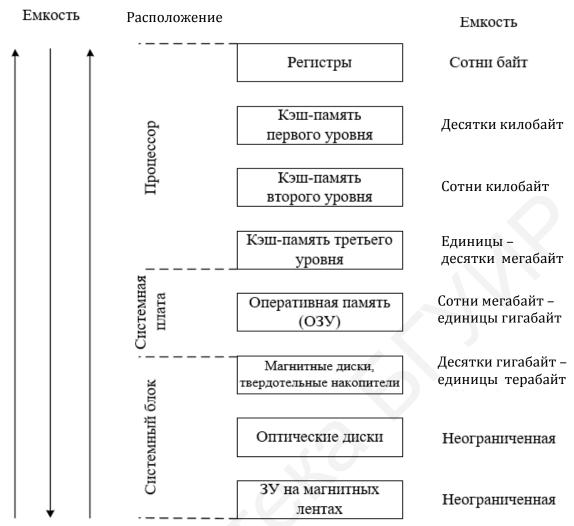

Для современных типов запоминающих устройств характерна следующая закономерность: чем больше емкость, тем ниже стоимость хранения бита, но больше время доступа.

При создании системы памяти ВМ приходится находить компромисс между параметрами стоимости, емкости и быстродействия. Построение памяти осуществляется по иерархическому принципу (рисунок 15).

Рисунок 15 – Иерархическая структура средств хранения информации

Техническая реализация памяти в ЭВМ осуществляется с помощью использования запоминающих устройств (ЗУ).

По устойчивости записи и возможности перезаписи ЗУ делятся:

- на постоянные ЗУ (ПЗУ), содержание которых не может быть изменено конечным пользователем (например, *BIOS*). ПЗУ в рабочем режиме допускает только считывание информации;

- записываемые ЗУ (ППЗУ), в которые конечный пользователь может записать информацию только один раз (например, CD-R);

- многократно перезаписываемые ЗУ (ПППЗУ) (например, *CD-RW*);

- оперативные ЗУ, обеспечивающие режим записи, хранения и считывания информации в процессе ее обработки.

По типу доступа ЗУ делятся:

- на устройства с последовательным доступом (например, магнитные ленты);

- устройства с произвольным доступом (RAM) (например, оперативная память);

- устройства с прямым доступом (например, жесткие магнитные диски);

- устройства с ассоциативным доступом (специальные устройства для повышения производительности).

**Энергонезависимая память** (от англ. *Non Volatile Random Access Memory* – NVRAM) — перезаписываемая или оперативная память в электронном устройстве, сохраняющая свое содержимое вне зависимости от подачи основного питания на устройство.

В общем случае энергонезависимая память – любое устройство или его часть, сохраняющие данные вне зависимости от подачи питающего напряжения.

**Постоянное запоминающее устройство** (**ПЗУ**) (от англ. *Read-Only Memory* -ROM) — энергонезависимая память, которая используется для хранения массива неизменяемых данных.

**Оперативная память** (также оперативное запоминающее устройство, **ОЗУ**) — часть системы памяти ЭВМ, в которую процессор может обратиться за одну операцию (*jump*, *move* и т. д.). Предназначена для временного хранения данных и команд, необходимых процессору для выполнения им операций. ОЗУ передает процессору данные непосредственно либо через кэш-память. Каждая ячейка оперативной памяти имеет свой индивидуальный адрес.

ОЗУ может изготавливаться как отдельный блок или входить в конструкцию однокристальной ЭВМ или микроконтроллера.

Сегнетоэлектрическая память (FRAM) (от англ. Ferroelectric RAM) — статическая оперативная память с произвольным доступом, ячейки которой сохраняют информацию, используя сегнетоэлектрический эффект. Ячейка памяти представляет собой две токопроводящие обкладки и пленку из сегнетоэлектрического материала. В центре сегнетоэлектрического кристалла имеется подвижный атом. Приложение электрического поля заставляет его перемещаться. В случае если поле «пытается» переместить атом в положение, например, соответствующее логическому нулю, а он в нем уже находится, то через сегнетоэлектрический конденсатор проходит меньший заряд, чем в случае переключения ячейки. На измерении проходящего через ячейку заряда и основано считывание. При этом процессе ячейки перезаписываются и информация теряется (требуется регенерация). Исследованиями в этом направлении занимаются фирмы Hitachi совместно с Ramtron, Matsushita с фирмой Symetrix. По сравнению с флэш-памятью ячейки FRAM практически не деградируют — гарантируется до 10<sup>10</sup> циклов перезаписи.

Память, реализованная на основе ЗУ, — записи, в которых стираются при снятии электропитания. К этому типу памяти относится память, реализованная на ОЗУ, — кэш-память.

## 2.1.2 Статическая оперативная память с произвольным доступом SRAM

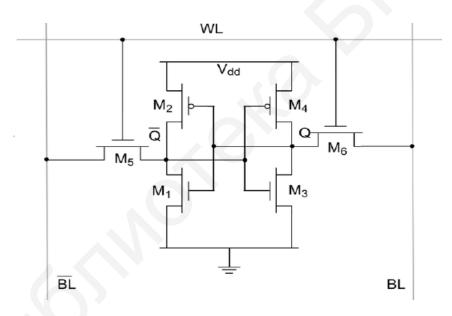

Статическая оперативная память с произвольным доступом SRAM (Static Random Access Memory — SRAM) — полупроводниковая оперативная память, строящаяся на триггерах, в которой каждый двоичный или троичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние сигнала без постоянной перезаписи. Тем не менее сохранять данные без перезаписи SRAM может только пока есть питание, т. е. SRAM является энергозависимым типом памяти. Произвольный доступ (Random Access Memory — RAM) — возможность выбирать для записи/чтения любой из битов (тритов) (чаще байтов (трайтов)), зависит от особенностей конструкции), в отличие от памяти с последовательным доступом (Sequental Access Memory — SAM).

#### Двоичная SRAM

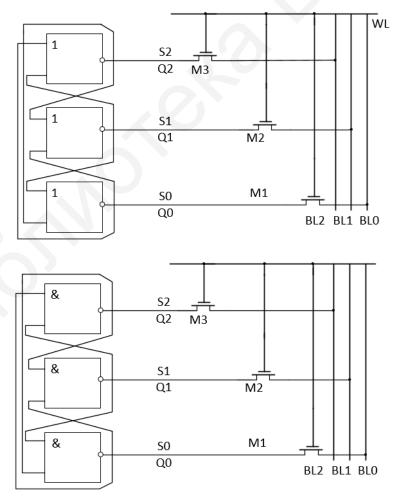

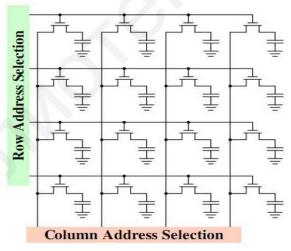

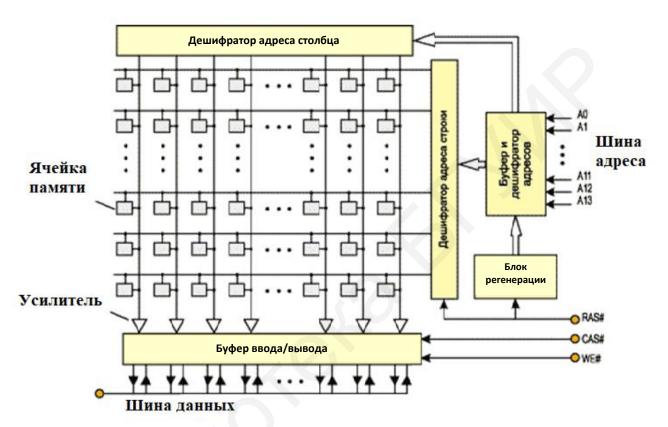

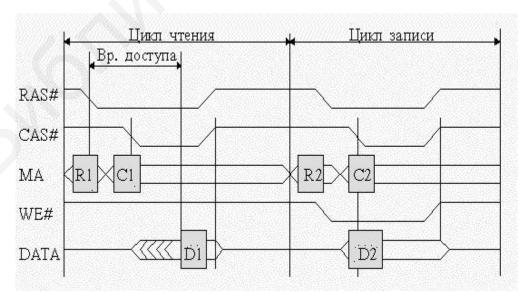

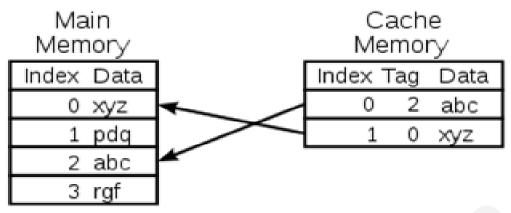

Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии состоит из двух перекрестно (кольцом) включенных инверторов и ключевых транзисторов для обеспечения доступа к ячейке (рисунок 16).

Рисунок 16 – Шеститранзисторная ячейка статической двоичной памяти (бит) *SRAM*

Часто для увеличения плотности упаковки элементов на кристалле в качестве нагрузки применяют поликремниевые резисторы. Недостатком такого решения является рост статического энергопотребления.

Линия WL (Word Line) управляет двумя транзисторами доступа.

Линии  $\overline{BL}$  и BL (Bit Line) — битовые линии, использующиеся и для записи данных, и для чтения данных.

Запись. При подаче нуля на линию BL или  $\overline{BL}$  параллельно включенные транзисторные пары (M5 и M1) и (M6 и M3) образуют логические схемы ИЛИ,

последующая подача единицы на линию WL открывает транзистор M5 или M6, что приводит к соответствующему переключению триггера.

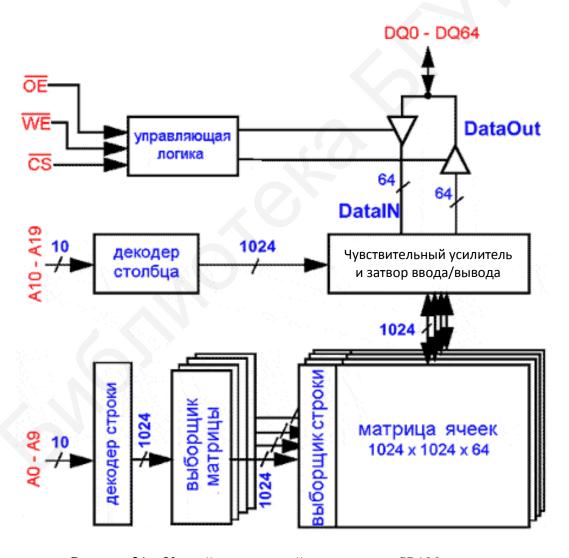

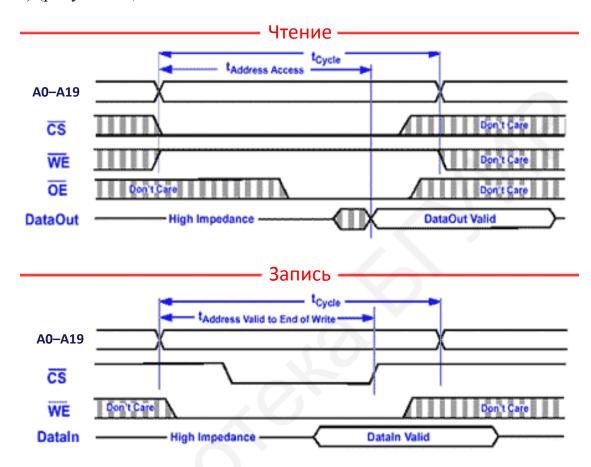

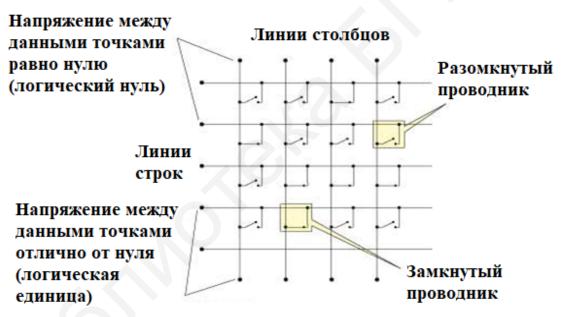

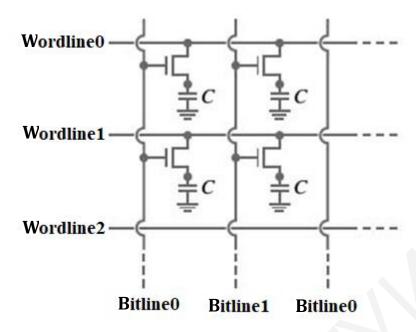

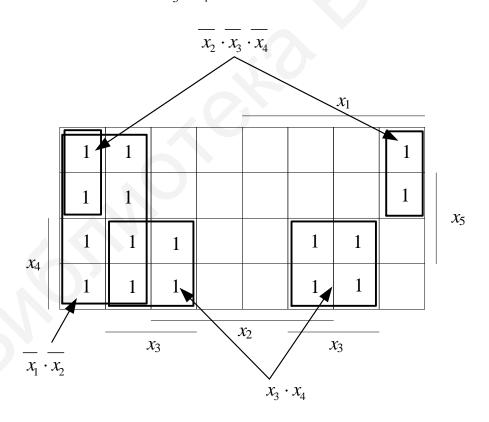

Чтение. При подаче единицы на линию WL открываются транзисторы M5 и M6, уровни, записанные в триггере, выставляются на линии BL и BL и попадают на схемы чтения.