# Министерство образования Республики Беларусь Учреждение образования Белорусский государственный университет информатики и радиоэлектроники

УДК 004.031.6

Бурак Антон Андреевич

Сопроцессор двумерного вейвлет-преобразования на основе лестничной факторизации

#### **АВТОРЕФЕРАТ**

на соискание степени магистра технических наук по специальности 1-40 80 01 «Компьютерная инженерия»

Бурак. А.А.

Научный руководитель: Петровский Н.А. к.т.н., доцент кафедры ЭВС

Нормоконтроль

Лихачёв Денис Сергеевич

Работа выполнена на кафедре электронных вычислительных средств учреждения образования "Белорусский государственный университет информатики и радиоэлектроники"

Научный руководитель: ПЕТРОВСКИЙ Николай Александрович,

кандидат технических наук, доцент кафедры электронных вычислительных средств учреждения образования "Белорусский государственный университет информатики

и радиоэлектроники"

Рецензент: СТРОГОВА Александра Сергеевна,

заместитель начальника главного управления науки-начальник отдела организации и сопровождения инновационной деятельности Белорусского

государственного университета.

Защита диссертации состоится 27 апреля 2023 года в 12:00 часов на экзаменационной заседании Государственной комиссии ПО зашите образования магистерских диссертаций В учреждении "Белорусский государственный университет информатики и радиоэлектроники" по адресу 220013, Минск, ул. П. Бровки, 6, корп. 1, ауд 3116, тел. 293-89-46, Е-mail: kafevs@bsuir.by

С диссертацией можно ознакомиться в библиотеке учреждения образования "Белорусский государственный университет информатики и радиоэлектроники".

## КРАТКОЕ ВВЕДЕНИЕ

Дискретное вейвлет-преобразование стало очень универсальным инструментом обработки сигналов за последнее десятилетие. Фактически, он эффективно использовался в приложениях обработки сигналов и изображений с тех пор, как Маллат предложил представление сигналов с множественным разрешением, основанное на вейвлет-разложении. Преимущество дискретного вейвлет-преобразования перед другими традиционными преобразованиями состоит в том, что оно выполняет анализ сигналов с множеством разрешений и локальной привязкой как по времени, так и по частоте. В настоящее время дискретное вейвлет-преобразование все чаще используется для сжатия изображений, поскольку оно поддерживает такие функции, как прогрессивная передача изображения, кодирование области интереса и т. д. Фактически, оно является основой стандарта сжатия изображений JPEG2000, который показал превосходную производительность по сравнению со стандартом JPEG. Дискретное вейвлет-преобразование традиционно реализовывался в виде структуры банка КИХ фильтров. Такие реализации требуют как большого количества арифметических вычислений, так и большого объема памяти, что нежелательно ни для высокоскоростных, ни для маломощных приложений обработки изображений/видео. Свелдс предложил новую математическую формулировку вейвлет-преобразования, основанную ДЛЯ пространственном построении вейвлетов. Схемы ДЛЯ вычисления, реализованные по этому принципу, называются лестничными схемами. Эта схема часто требует гораздо меньшего количества вычислений по сравнению с дискретным вейвлет-преобразованием на основе банка КИХ-фильтров и может быть использована в задачах требующих перфективной реконструкции изображений.

## ОБЩАЯ ХАРАКТЕРИСТИКА РАБОТЫ

Целью данной работы были анализ существующих подходов для разделимых двухмерных разделимых дискретных вейвлет преобразований на основе лестничной параметризации, разработка архитектур для вейвлетпреобразований 5/3, 9/7 и вейвлет преобразования на основе банка фильтров.

В работе показы архитектуры и FPGA реализации IP-компонентов целочисленного обратимого дискретного вейвлет преобразования 5/3, необратимого дискретного вейвлет преобразования 9/7, целочисленного обратимого умножителя кватернионов для 8-канального параунитарного банка фильтров на основе алгоритма CORDIC-II.

Основные результаты диссертационной работы докладывались и обсуждались на 4-х международных и республиканских научных конференциях:

57-я научная конференция аспирантов, магистрантов и студентов БГУИР – Минск, 2021;

24-я и 25-я международная конференция Цифровая обработка сигналов и ее приложения (DSPA-2022, DSPA-2023) – 2022, 2023 Москва;

Международная научная конференция: Информационные технологии и системы (ITS-2022) – Минск, 2022.

В результате работы получена архитектура разделимого целочисленного разделимого вейвлет преобразования 5/3 опубликован в сборнике докладов БГУИР [1–А.];. архитектура разделимого дискретного вейвлет 9/7, которая опубликована в сборнике РНТОРЭС имени А.С. Попова [2–А.]; разработана архитектура обратимого умножителя кватернионов и опубликован и опубликована в сборнике докладов ITS-2022 [3–А.]; разработана архитектура вейвлет преобразования на основе Q-ПУБФ с использованием алгоритма CORDIC-II и опубликована работа по применению умножителя кватернионов на основе алгоритма CORDIC-II в сборнике РНТОРЭС имени А.С. Попова [4–А.]. Представленные результаты прошли апробацию на международных научно-технических конференциях Российской Федерации и Республики Беларусь и получили экспертные отзывы от научных лидеров в данной области.

## КРАТКОЕ СОДЕРЖАНИЕ РАБОТЫ

Из-за экспоненциального роста необходимости обрабатываемых изображений наблюдается значительный интерес к алгоритмам сжатия изображений как с потерями, так и без. Одной из частей компрессии могут быть декореллирующие преобразования вследствие чего проблема поиска эффективных преобразований и их аппаратной реализации являются актуальной.

В работе рассмотрены аппаратные архитектуры ДЛЯ вейвлет преобразований из стандарта JPEG2000 такие как 5/3 и 9/7. Для каждой из них были разработаны HDL описания и Matlab модели для верификации HDL описания. Разработанные ІР-ядра были просинтезированы для системы на кристалле типа Xilinx Zynq; указаны аппаратные затраты, пропускная способность. Для данного вейвлет-преобразования был разработан стендовый проект в составе системы на кристалле типа Xilinx Zynq, в котором изображения для обработки будут поступать по интерфейсу HDMI. Далее цветное изображение конвертируется в изображение в градациях серого. Далее над данными производится вейвлет-преобразование. После обработки данные поступают на контроллер прямого доступа в память и записываются в буфер. Далее обработка изображения будет уже производиться на процессоре, а именно будет выполнена перестановка строк и столбцов для дальнейшего вывода коэффициентов. Аппаратные затраты проекта представлены в таблице 1. В составе стендового проекта производительности ІР-ядра вейвлет преобразования 5/3 достаточно ДЛЯ потокового видео разрешением 1280 на 720 пикселей с частотой 60 кадров в секунду в режиме реального времени. Аппаратные затраты для ІР-ядра дискретного вейвлет-преобразования 9/7 представлены в таблице 2; максимальная скорость обработки блоков 512х512 составила 1473,5 блоков/с.

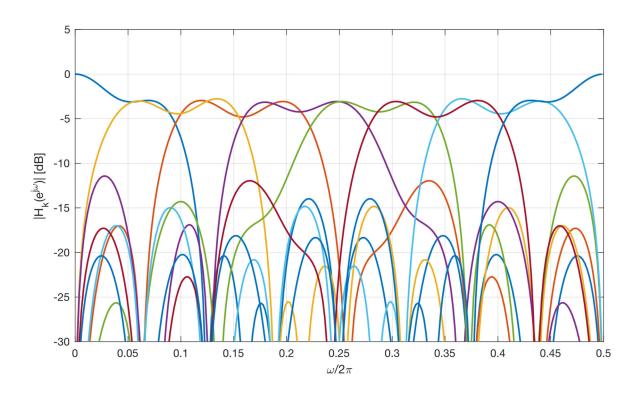

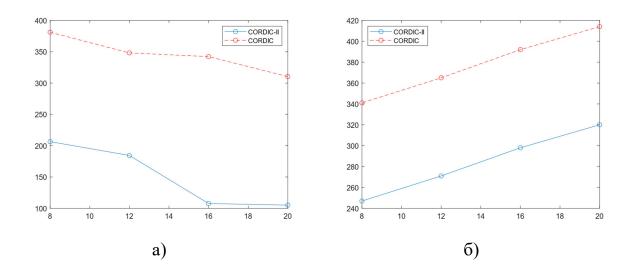

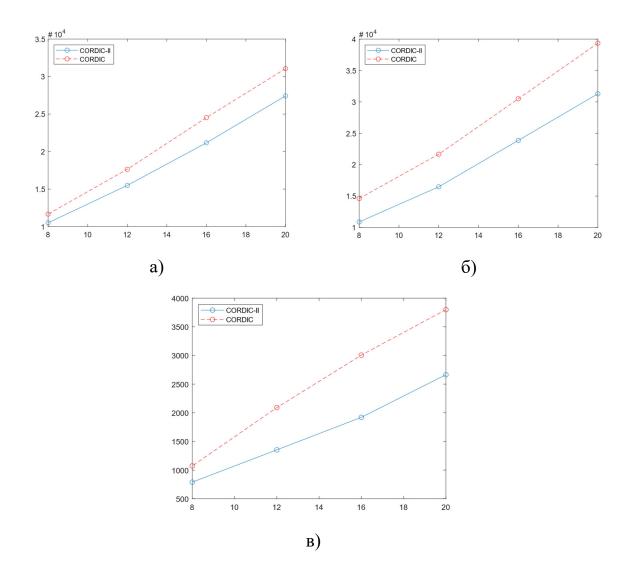

Реализовано IP-ядро вейвлет преобразование на основе Q-ПУБФ с использованием умножителя кватернионов базовым блоком которого являлся алгоритм CORDIC-II. Составлена Matlab модель для верификации IP-ядра. Разработан алгоритм преобразования коэффициентов Q-ПУБФ в углы поворота итераций алгоритма CORDIC-II и коэффициентов масштабирования посредством алгоритма CSD. Произведено сравнение Q-ПУБФ на основе алгоритмов CORDIC-II и CORDIC (таблица 3). Проанализированы импульсные характеристики Q-ПУБФ и на основе их построены АЧХ фильтров. АЧХ Q-ПУБФ разрядностью 16 с указанной эффективностью

кодирования CG представлена на рисунке 1. Графики латентности и максимальной рабочей частоты Q-ПУБФ представлены на рисунке 2. Графики аппаратных затрат представлены на рисунке 3.

Таблица 1 — Потребляемые ресурсы стендового проекта вейвлет преобразования 5/3 для кристалла xc7z010clg400-1

| Pecypc | Использовано | Доступно | Использовано, % |

|--------|--------------|----------|-----------------|

| LUT    | 8203         | 17600    | 46.61           |

| LUTRAM | 540          | 6000     | 9.0             |

| FF     | 14833        | 35200    | 42.14           |

| BRAM   | 17.5         | 60       | 29.17           |

| IO     | 44           | 100      | 44.0            |

| BUFG   | 5            | 32       | 15.63           |

| MMCM   | 2            | 2        | 100.0           |

| PLL    | 1            | 2        | 50.0            |

Таблица 2 — Потребляемые ресурсы процессором 2D вейвлет преобразования 9/7 для кристалла xc7z020clg400-1

| Pecypc  | Доступно | Использовано, | Использовано, % |

|---------|----------|---------------|-----------------|

|         |          | шт.           |                 |

| LUT     | 53200    | 1066          | 2,00            |

| LUTRAM  | 17400    | 544           | 3,13            |

| FF      | 106400   | 617           | 0,58            |

| BRAM    | 140      | 0,5           | 0,36            |

| DSP48E1 | 220      | 8             | 3,64            |

Таблица 4.9 — Аппаратные затраты, латентность и максимальная рабочая частота для Q-ПУБФ на основе алгоритмов CORDIC-II и CORDIC с разрядностью входных данных W=16 для кристалла Xilinx Zynq 7020 (xc7z020clg400-1)

| Ресурсы                   | CORDIC-II | CORDIC |

|---------------------------|-----------|--------|

| LUT                       | 21167     | 24527  |

| FF                        | 23868     | 30495  |

| LUTRAM                    | 1921      | 3006   |

| Латентность [тактов]      | 298       | 392    |

| Частота $(f_{clk})$ [МГц] | 107.7     | 342.2  |

Рисунок 1 — АЧХ 8 × 24 Q-ПУБФ с попарной симметрией частотных характеристик для разрядности W=16, эффективность кодирования  $CG_{16}=9.19$

Рисунок 2 — Графики сравнения  $8 \times 24 \ Q$ -ПУБФ на основе алгоритмов CORDIC-II и CORDIC (а —максимальной рабочей частоты Q-ПУБФ от разрядности входных данных; б — латентности в тактах от разрядности входных данных)

Рисунок 3 — Графики аппаратных затрат от разрядности входных данных для  $8 \times 24~Q$ -ПУБФ (а — LUT, б — FF, в — LUTRAM)

#### ЗАКЛЮЧЕНИЕ

В результате работы был проведен анализ существующих подходов по реализации 2-х мерных разделимых дискретных вейвлет-преобразований на основе лестничной факторизации. Были предложены следующие архитектуры:

- архитектура обратимого дискретного-вейвлет преобразования 5/3;

- архитектура необратимого дискретного вейвлет преобразования 9/7;

- архитектура вейвлет преобразования на основе Q-ПУБФ с использованием алгоритма CORDIC-II.

Для каждой из архитектур составлены модели в Matlab, проведена верефикация, разработаны IP-ядра, приведены аппаратные затраты и проанализированы максимальные частоты работы для ПЛИС серии Xilinx Zynq. Вейвлет-преобразования 5/3 и 9/7 соответствуют вейвлет-преобразованиям из стандарта сжатия изображений JPEG2000.

Для дискретного вейвлет-преобразования 5/3 разработан стендовый проект на отладочной плате Zybo, который принимает исходное изображение по HDMI, производит вейвлет-преобразование и выводит коэффициенты на экран.

Для вейвлет преобразования на основе Q-ПУБФ разработан Matlab алгоритм преобразования коэффициентов Q-ПУБФ в углы вращения и коэффициенты масштабирования для лестничной архитектуры умножителя кватернионов.

Предложена архитектура умножителя на кватернион константу, которая послужила блоком для реализации Q-ПУБФ. Сравнены умножители кватернионов на основе алгоритмов CORDIC и CORDIC-II. Приведены их аппаратные затраты максимальная рабочая частота и зависимость пропускной способности от разрядности входных данных.

Проведено сравнение Q-ПУБФ на основе алгоритма CORDIC-II и на основе алгоритма CORDIC. Так же построены АЧХ и проанализирована эффективность кодирования Q-ПУБФ на основе алгоритма CORDIC-II. Применение алгоритма CORDIC-II как в умножителе кватернионов, так и в Q-ПУБФ позволило уменьшить аппаратные затраты до 30%, уменьшить латентность до 40%. Недостатком предложенной архитектуры является меньшая максимальная рабочая частота в 1.5 – 3 раза. Из особенностей проведенных экспериментов для Q-ПУБФ стоит отметить, что полученные

зависимости эффективности кодирования CG от разрядности данных W имеют нелинейный характер и свидетельствует о необходимости модификации алгоритма синтеза коэффициентов банка фильтров с учетом особенностей итерационного процесса CORDIC-II, к примеру  $CG_{12}$  сопоставим с  $CG_{20}$ , однако лучше чем  $CG_{16}$  почти на 0.2 дБ.

Все предложенные архитектуры могут быть использованы в задачах трансформационного кодирования изображений.

#### СПИСОК ОПУБЛИКОВАННЫХ РАБОТ

- [1–A.] Бурак, А. А. Целочисленный сопроцессор вейвлет-преобразования для ПЛИС / А. А. Бурак // Компьютерные системы и сети: 57-я научная конференция аспирантов, магистрантов и студентов, Минск, 19-23 апреля 2021 г.: сборник тезисов докладов / Белорусский государственный университет информатики и радиоэлектроники. Минск, 2021. С. 8–9.

- [2–A.] Бурак, А. А. Параллельно-поточный процессор 2D вейвлет преобразования 9/7 на основе лестничной факторизации / А. А. Бурак, Н. А. Петровский // 24-я международная конференция DSPA-2022, Москва, 2022 г.: сборник докладов конференции DSPA-2022 / PHTOPЭC им. А.С. Попова. Москва, 2022. С. 216 220.

- [3–A.] Бурак, А. А. Умножитель кватернионов на основе блочно-лестничной факторизации с использованием алгоритма CORDIC-II / А. А. Бурак Н. А. Петровский // Международная научная конференция: Информационные технологии и системы 2022 / Белорусский государственный университет информатики и радиоэлектроники. Минск, 2022. С. 73–74.

- [4–A.] Бурак, А. А. ПЛИС/FPGA архитектура обратимого умножителя кватернионов на основе алгоритма CORDIC-II для банка фильтров / А. А. Бурак, Н. А. Петровский // 25-я международная конференция DSPA-2023, Москва, 2023 г.: сборник докладов конференции DSPA-2023 / РНТОРЭС им. А.С. Попова. Москва, 2023. 6 с.