## Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

Факультет телекоммуникаций

Кафедра защиты информации

С. Н. Петров

# ЦИФРОВЫЕ И МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА. МИКРОКОНТРОЛЛЕРЫ AVR. ЛАБОРАТОРНЫЙ ПРАКТИКУМ

Рекомендовано УМО по образованию в области информатики и радиоэлектроники в качестве учебно-методического пособия для направлений специальности 1-45 01 01-02 «Инфокоммуникационные технологии (сети инфокоммуникаций)», 1-45 01 01-05 «Инфокоммуникационные технологии (системы распределения мультимедийной информации)», 1-45 01 01-06 «Инфокоммуникационные технологии (лазерные информационно-измерительные системы)», 1-45 01 02-01 «Инфокоммуникационные системы (стандартизация, сертификация и контроль параметров)», 1-98 01 02 «Защита информации в телекоммуникациях»

УДК 004.31(076.5) ББК 32.973.26-018.2я73 П30

#### Рецензенты:

кафедра телекоммуникационных систем учреждения образования «Белорусская государственная академия связи» (протокол №9 от 06.04.2015);

начальник кафедры автоматизированных систем управления войсками учреждения образования «Военная академия Республики Беларусь», кандидат технических наук, доцент А. В. Хижняк

## Петров, С. Н.

ПЗО Цифровые и микропроцессорные устройства. Микроконтроллеры AVR. Лабораторный практикум: учеб.-метод. пособие / С. Н. Петров. – Минск: БГУИР, 2016. – 86 с.: ил.

ISBN 978-985-543-201-3.

Посвящено изучению 8-разрядных микроконтроллеров AVR семейства Mega. Рассмотрены программные средства разработки и отладки программ.

Содержит восемь лабораторных работ, каждая из которых включает краткие теоретические сведения, лабораторное задание, содержание отчета, контрольные вопросы и задания к каждой теме.

Лабораторные работы направлены на изучение архитектуры микроконтроллера, работы портов ввода/вывода, системы таймеров и прерываний, передачи данных по последовательному каналу связи, работы с периферийными устройствами. Для написания программ применяется язык ассемблера.

УДК 004.31(076.5) ББК 32.973.26-018.2я73

ISBN 978-985-543-201-3

© Петров С. Н., 2016

© УО «Белорусский государственный университет информатики и радиоэлектроники», 2016

# СОДЕРЖАНИЕ

| Введение                                                              | 4  |

|-----------------------------------------------------------------------|----|

| 1 Общие сведения о микроконтроллере Atmega 16                         | 5  |

| 1.1 Архитектура и структура микроконтроллера AVR Atmega 16            | 5  |

| 1.2 Порты ввода/вывода                                                | 8  |

| 1.3 Система прерываний                                                | 9  |

| 1.4 Таймеры/счетчики                                                  | 11 |

| 1.5 Последовательные порты                                            | 15 |

| 1.6 Организация памяти                                                | 21 |

| 1.7 Регистры управления                                               | 23 |

| 2 Система команд Atmega 16                                            | 26 |

| 2.1 Режимы адресации                                                  | 26 |

| 2.2 Команды Atmega 16                                                 | 30 |

| 2.3 Директивы ассемблера                                              | 40 |

| 3 Программное обеспечение лабораторного практикума                    | 45 |

| 3.1 Интегрированная среда разработки Atmel Studio                     | 45 |

| 3.2 Среда автоматизированного проектирования Proteus                  | 54 |

| 4 Лабораторный практикум                                              | 63 |

| Лабораторная работа №1. Изучение интегрированной среды разработки     |    |

| Atmel Studio для программирования микроконтроллеров AVR               | 63 |

| Лабораторная работа №2. Изучение принципов организации памяти         | 65 |

| Лабораторная работа №3. Изучение системы команд микроконтроллера      |    |

| Atmega 16.                                                            | 67 |

| Лабораторная работа №4. Изучение портов ввода/вывода микроконтроллера |    |

| Atmega 16.                                                            | 69 |

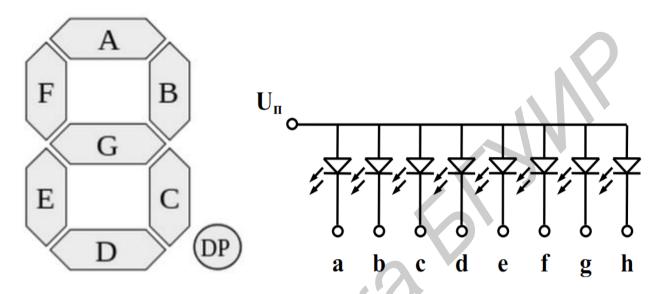

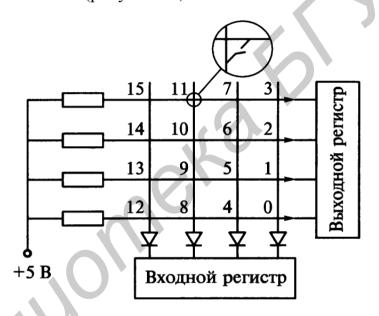

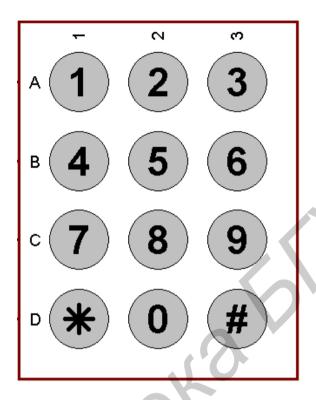

| Лабораторная работа №5. Изучение принципов работы с внешними          |    |

| устройствами, клавиатурой и семисегментным индикатором                | 72 |

| Лабораторная работа №6. Изучение таймеров и системы прерываний        | 75 |

| Лабораторная работа №7. Изучение принципов работы с последовательным  |    |

| интерфейсом                                                           | 79 |

| Лабораторная работа №8. Изучение принципов работы с внешними          |    |

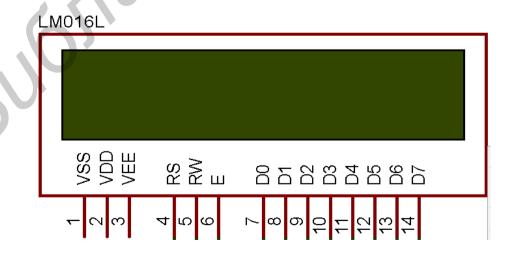

| устройствами, жидкокристаллической панелью                            | 82 |

| Литература                                                            | 85 |

#### Введение

Микропроцессорное устройство (МПУ) служит для выполнения арифметических, логических операций и операций управления, записанных в машинном коде. В данном учебно-методическом пособии рассматриваются вопросы изучения 8-разрядного микроконтроллера Atmega16 фирмы Atmel.

Особенностью устройств на базе МПУ является взаимодействие аппаратных узлов и программного обеспечения. Программная реализация алгоритма управления обеспечивается за счет циклического выполнения заданного набора команд. Программная реализация обеспечивает высокую степень гибкости, так как одно и то же МПУ путем замены управляющей программы может решать совершенно разные задачи или легко изменять набор решаемых задач.

Ядро AVR построено на технологии RISC и оптимизировано под кодирование на языке С. Это обеспечивает хорошее качество разработки с небольшими затратами времени по сравнению с разработкой программного обеспечения на ассемблере. Тем не менее, хотя написание программы на ассемблере занимает больше времени по сравнению с программами на языках высокого уровня, изучение основ программирования на ассемблере имеет ряд достоинств. Поскольку каждый ассемблер тесно связан набором команд процессора, изучение языка ассемблера дает возможность лучшего понимания деталей архитектуры, связи между аппаратным и программным уровнями, механизмов использования памяти, функционирования стека, вызова процедур. Следовательно, язык ассемблера может быть использован как инструмент для изучения архитектуры процессора.

Настоящее учебно-методическое пособие ориентировано на использование программ-симуляторов, имитирующих поведение МПУ под управлением программы. Интегрированная среда разработки (IDE) Atmel Studio 6 служит для разработки и отладки AVR-программ, в ее состав входят средства управления проектом, редактор текстов, симулятор, внутрисхемный эмулятор. Для знакомства со схемотехникой подключения к микроконтроллеру датчиков, устройств индикации, кнопок, переключателей и т. д. используется пакет аналого-цифрового моделирования Proteus 7.60 фирмы Labcenter Electronic.

Для закрепления материала по каждой теме предлагаются наборы заданий разного уровня сложности. Простые требуют незначительного изменения параметров или структуры алгоритма управления, более сложные требуют осмысленного объединения элементов алгоритмов из нескольких примеров.

### **1 ОБЩИЕ СВЕДЕНИЯ О МИКРОКОНТРОЛЛЕРЕ ATMEGA 16**

### 1.1 Архитектура и структура микроконтроллера AVR Atmega 16

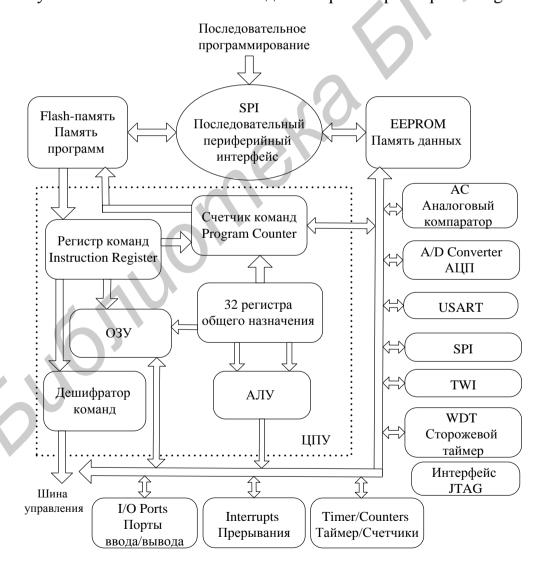

Микроконтроллер Atmega16 относится к семейству AVR (Advanced Virtual RISC) производства компании Atmel. Микроконтроллеры семейства AVR построены на гарвардской архитектуре, имеют 32 8-битных регистра общего назначения, в зависимости от модели поддерживают до 133 инструкций.

RISC (Reduced Instruction Set Computer) – архитектура микроконтроллера, в котором быстродействие увеличивается за счет упрощения инструкций, чтобы их декодирование было более простым, а время выполнения меньшим.

Гарвардская архитектура — архитектура, отличительным признаком которой является структура с разделенными устройствами памяти команд и данных и отдельными шинами команд и данных. Такая организация позволяет одновременно работать как с памятью программ, так и с памятью данных. Разделение шин доступа позволяет использовать для каждого типа памяти шины различной разрядности, причем способы адресации и доступа к каждому типу памяти также различны. Такая организация позволяет выполнять команды за один такт.

Еще одним решением, направленным на повышение быстродействия, является использование технологии конвейеризации. Конвейеризация заключается в том, что во время исполнения текущей команды производится выборка из памяти и дешифрация кода следующей команды. Причем длительность машинного цикла микроконтроллеров AVR составляет всего один период кварцевого резонатора.

Технические характеристики:

- flash-память программ объемом 16 Кбайт;

- оперативная память (статическое ОЗУ) объемом 1 Кбайт;

- память данных на основе ЭСППЗУ (EEPROM) объемом 256 байт (число циклов стирания/записи не менее 100 000);

- возможность программирования непосредственно в системе через последовательные интерфейсы SPI и JTAG;

- разнообразные способы синхронизации;

- статическая архитектура, минимальная тактовая частота равна нулю;

- арифметико-логическое устройство (АЛУ) подключено непосредственно к регистрам общего назначения (32 регистра);

- векторная система прерываний, поддержка очереди прерываний;

- наличие аппаратного умножителя;

- программное конфигурирование и выбор портов ввода/вывода;

- входные буферы с триггером Шмитта на всех выводах;

- на всех входах имеются индивидуально отключаемые внутренние подтягивающие резисторы сопротивлением  $20-50\ \mathrm{kOm};$

- 131 высокопроизводительная команда;

- производительность порядка 16 MIPS при тактовой частоте 16 МГц;

- рабочее напряжение 4,5 - 5,5 B, тактовая частота 0 - 16 МГц.

**Подтягивающий резистор** (pull-up resistor) позволяет избежать чтения с входа различных помех, что повышает надежность устройства в целом. Однако повышает энергопотребление. В тех случаях, когда мощность входного сигнала высока, подтягивающий резистор подключать нет необходимости.

При разомкнутой кнопке задачей подтягивающего резистора является «дотягивание» напряжения на ножке порта до уровня VCC. Отсюда и название этого сопротивления. Без этого сопротивления ножка порта остается висеть в воздухе (при разомкнутой кнопке), т. е. не соединена ни с GND, ни с VCC. Этого состояния следует избегать, т. к. всякие наводки могут привести к неправильному состоянию конкретного входа. Подтягивающий резистор обеспечивает, таким образом, логическую единицу при разомкнутой кнопке.

Подтягивающее сопротивление имеет смысл только для входа.

Подтягивающее сопротивление на входе управляется с помощью регистра PORT. Таким образом, регистр PORT имеет две функции. Если порт настроен как выход, то этот регистр задает логический уровень соответствующих битов. Если же порт настроен как вход, то PORT указывает на включенные/выключенные подтягивающие сопротивления.

### Встроенная периферия:

- два 8-разрядных таймера/счетчика с отдельным предварительным делителем, один с режимом сравнения;

- один 16-разрядный таймер/счетчик с отдельным предварительным делителем и режимами захвата и сравнения;

- счетчик реального времени с отдельным генератором;

- программируемый сторожевой таймер;

- аналоговый компаратор;

- четыре канала широтно-импульсного модулятора ШИМ (разрешение формируемого сигнала может составлять от 1 до 16 бит);

- 8-канальный 10-разрядный аналого-цифровой преобразователь АЦП последовательного приближения;

- 8 несимметричных каналов;

- байт-ориентированный 2-проводный последовательный интерфейс;

- полнодуплексный универсальный синхронный/асинхронный приемопередатчик (USART);

- последовательный двухпроводный интерфейс TWI (аналог I2C);

- последовательный синхронный интерфейс SPI (ведущий/ведомый).

### Структурная организация

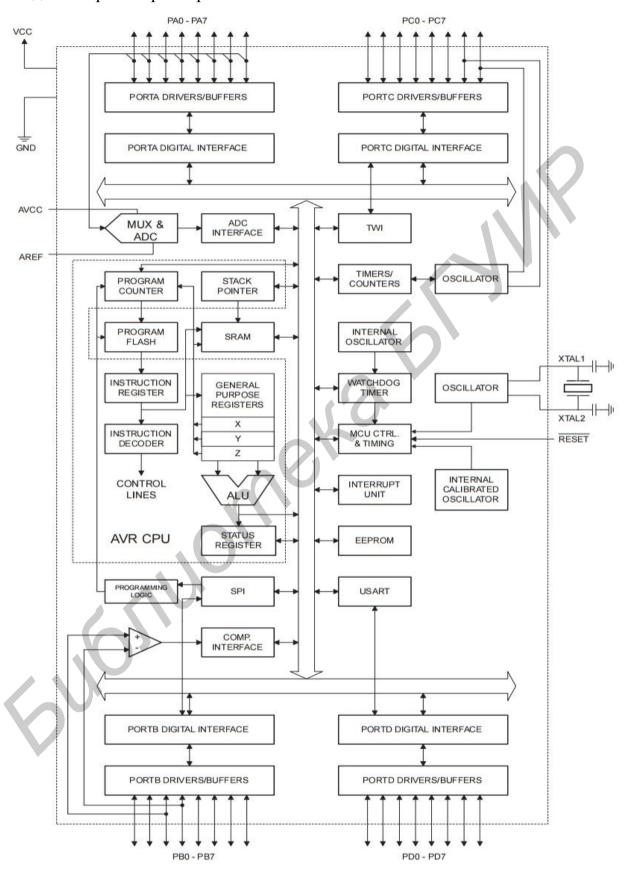

Арифметико-логическое устройство (АЛУ), выполняющее все вычисления, подключено непосредственно к 32 рабочим регистрам общего назначения (РОН), объединенным в регистровый файл. Благодаря этому любой РОН может использоваться практически во всех командах и как операнд-источник, и как операнд-приемник. Благодаря этому АЛУ выполняет одну операцию (чтение содержимого регистров, выполнение операции и запись результата обратно в регистровый файл) за один машинный цикл. Упрощенная архитектура ядра

AVR семейства Mega 16 показана на рисунке 1. Далее представлено описание выводов микроконтроллера.

Рисунок 1 – Структурная схема микроконтроллеров AVR семейства Mega

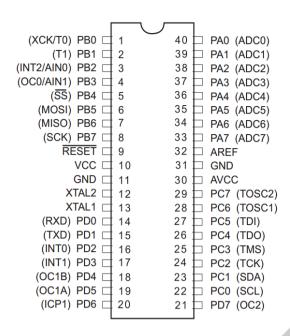

**Reset** – вход сигнала сброса. Низкий уровень импульса на этом выводе, который длиннее, чем минимальная длина импульса, сгенерирует сброс, даже если тактирование не запущено.

**XTAL1** — вход для инвертирующего усилителя генератора и вход для внутренней операционной схемы тактирования.

**XTAL2** – выход для инвертирующего усилителя генератора.

**AVCC** – вывод напряжения питания для порта А и АЦП. Он должен быть внешне соединен с VCC, даже если АЦП не используется. Если АЦП используется, он должен быть соединен с VCC через фильтр низких частот.

**AREF** – это аналоговый установочный вывод для АЦП.

VCC – цифровое напряжение питания.

**GND** – земля.

## 1.2 Порты ввода/вывода

Микроконтроллер имеет четыре 8-разрядных параллельных порта Px (x = A, B, C, D). Выводы портов тристабильны.

**Port A** (PA7 – PA0). Порт А выступает в качестве аналоговых входов на АЦП. Порт А также служит в качестве 8-битного двунаправленного порта ввода/вывода, в случае когда АЦП не используется. Выводы порта могут обеспечить внутренние нагрузочные резисторы (выбираемые для каждого бита). Выходные буферы порта А имеют симметричные характеристики привода с высокой способностью стока и истока. Когда выводы РА0-РА7 используются как входы и на них небольшая внешняя нагрузка, они будут источниками тока, если нагрузочные резисторы активированы.

**Port B** (PB7 – PB0). Порт В – это двунаправленный порт ввода/вывода с внутренними нагрузочными резисторами (выбранными для каждого бита). Выходные буферы порта В имеют симметричные характеристики привода с высокой способностью стока и истока.

**Port C** (PC7 – PC0). Порт С – это двунаправленный порт ввода/вывода с внутренними нагрузочными резисторами (выбранными для каждого бита). Выходные буферы порта С имеют симметричные характеристики привода с высокой способностью стока и истока. Если включен интерфейс JTAG нагрузочные резисторы на выводах PC5(TDI), PC3(TMS) и PC2(TCK) будут активированы даже если произойдет сброс. Порт С используется для подключения интерфейса JTAG.

**Port D** (PD7 – PD0). Порт D – это двунаправленный порт ввода/вывода с внутренними нагрузочными резисторами (выбранными для каждого бита). Выходные буферы порта D имеют симметричные характеристики привода с высокой способностью стока и истока

Помимо функций ввода или вывода информации все порты имеют альтернативные функции. При использовании альтернативных функций выводов, регистры DDRx и PORTx должны быть установлены в соответствии с описанием альтернативных функций.

Каждый порт микроконтроллера AVR имеет восемь разрядов, каждый из которых привязан к определенной ножке корпуса. Каждый порт имеет три специальных регистра **DDRx**, **PORTx** и **PINx** (где х соответствует букве порта A, B, C или D). Назначение регистров представлено ниже.

**DDRx** – (Data Direction Register) настройка разрядов порта х на вход или выход. Отдельно взятый бит этого регистра отвечает за настройку отдельно взятого вывода этого порта.

**PORTx** – управление состоянием выходов порта х (если соответствующий разряд настроен как выход) или подключением внутреннего подтягивающего резистора (если соответствующий разряд настроен как вход).

**PIN**x – чтение логических уровней разрядов порта х.

Регистр DDRх выбирает направление работы каждой отдельной ножки порта. Если в разряд регистра DDRх записана логическая 1, то соответствующая ножка будет сконфигурирована как выход. Нуль означает, что порт сконфигурирован как вход (состояние по умолчанию, которое устанавливается после сброса или включения питания).

Регистр PORTx управляет состоянием выводов порта «х». В зависимости от выбранного направления работы (вход или выход) порта или отдельно взятого вывода значение, записанное в регистр PORTx того же порта, может присваивать выводу различные состояния.

Если в разряд DDRх записан 0 и в соответствующий разряд PORTх также записан 0, то порт сконфигурирован как вход с высоким входным сопротивлением, что соответствует отключенному выходному состоянию (третье состояние). Если в разряд PORTх записана логическая 1 и в соответствующий разряд DDRх записана логическая 1, то порт сконфигурирован как выход и на выходе будет логическая 1. То есть биты PORTх управляют состоянием выходного порта при условии, что в соответствующий порту разряд DDRх записана логическая 1.

### 1.3 Система прерываний

Система прерываний (Interrupts) — одна из важнейших частей микроконтроллера. Все микроконтроллеры AVR имеют многоуровневую систему прерываний. Прерывание прекращает нормальный ход программы для выполнения приоритетной задачи, определяемой внутренним или внешним событием.

При помощи источников прерываний реализуется механизм синхронизации между процессором и периферийным устройством, т. е. процессор начнет прием данных и других действий над периферийным устройством только тогда, когда устройство будет к этому готово, путем генерации запроса на обработку прерывания (Interrupt ReQuest, IRQ) в зависимости от значения некоторого флага (состояние устройства / функции / события).

Прерывание (Interrupt) – сигнал, сообщающий процессору о наступлении какого-либо события. При этом выполнение текущей последовательности команд приостанавливается и управление передается процедуре обработки прерывания, соответствующей данному событию, после чего исполнение кода продолжается ровно с того места, где он был прерван (возвращение управления).

Процедура обработки прерывания (Interrupt Service Routine, ISR) — это функция/подпрограмма, которую следует выполнить при возникновении определенного события. Главное отличие этой процедуры от простых функций состоит в том, что вместо обычного возврата из функции (команда RET) используется возврат из прерывания (команда RETI, RETurn from Interrupt).

За каждым прерыванием закреплен вектор (ссылка), указывающий на процедуру обработки прерывания. Все векторы прерываний располагаются в самом начале памяти программ и вместе формируют таблицу векторов прерываний (Interrupt vectors table).

Каждому прерыванию соответствует определенный бит активации прерывания (Interrupt Enable bit). Таким образом, чтобы использовать определенное прерывание, следует записать в его бит активации прерывания логическую 1. Далее микроконтроллер не начнет обработку этих прерываний, пока в бит всеобщего разрешения прерываний (Global Interrupt Enable bit в регистре состояния SREG) не будет записана логическая 1. Чтобы запретить все прерывания в бит всеобщего разрешения прерываний следует записать логический 0.

В Atmega 16 предусмотрен 21 источник прерываний. Эти прерывания и сброс имеют различные векторы в области памяти программ. Каждому из прерываний присвоен отдельный бит, разрешающий данное прерывание при установке бита в 1, если бит I регистра состояния SREG разрешает общее обслуживание прерываний.

Для каждого события может быть установлен приоритет. Понятие приоритет означает, что выполняемая подпрограмма прерывания может быть прервана другим событием только при условии, что оно имеет более высокий приоритет, чем текущее. В противном случае центральный процессор перейдет к обработке нового события только после окончания обработки предыдущего.

Самые младшие адреса памяти программ определены как векторы сброса и прерываний. Полный список векторов прерываний приведен в таблице 1. Этот список определяет и приоритет различных прерываний. Меньшие адреса соответствуют более высокому уровню приоритета. Самый высокий уровень у RESET (сброс), следующий приоритет у INT0 — внешнего запроса прерывания 0 и т. д.

Таблица 1 – Векторы прерываний Atmega 16

| Номер вектора | Адрес | Источник     | Описание прерывания                         |

|---------------|-------|--------------|---------------------------------------------|

| 1             | \$000 | RESET        | Вывод сброса и сброс от сторожевого таймера |

| 2             | \$002 | INT0         | Внешнее прерывание 0                        |

| 3             | \$004 | INT1         | Внешнее прерывание 1                        |

| 4             | \$006 | TIMER2 COMP  | Совпадение таймера/счетчика 2               |

| 5             | \$008 | TIMER2 OVF   | Переполнение таймера/счетчика 2             |

| 6             | \$00A | TIMER1 CAPT  | Захват таймера/счетчика 1                   |

| 7             | \$00C | TIMER1 COMPA | Совпадение таймера/счетчика 1               |

| 8             | \$00E | TIMER1 COMPB | Совпадение таймера/счетчика 1               |

| 9             | \$010 | TIMER1 OVF   | Переполнение таймера/счетчика 1             |

| 10            | \$012 | TIMER0 OVF   | Переполнение таймера/счетчика 0             |

| 11            | \$014 | SPI, STC     | Полная последовательная передача            |

| 12            | \$016 | USART, RXC   | Usart, Rx complete                          |

| 13            | \$018 | USART, UDRE  | Usart регистр данных пустой                 |

| 14            | \$01A | USART, TXC   | Usart, Tx complete                          |

| 15            | \$01C | ADC          | Аналого-цифровой преобразователь            |

| 16            | \$01E | EE_RDY       | EEPROM Ready                                |

| 17            | \$020 | ANA_COMP     | Аналоговый компаратор                       |

| 18            | \$022 | TWI          | Двухпроводной последовательный интерфейс    |

| 19            | \$024 | INT2         | Внешнее прерывание 2                        |

| 20            | \$026 | TIMER0 COMP  | Совпадение таймера/счетчика 0               |

| 21            | \$028 | SPM_RDY      | Загрузка программной памяти готова          |

### 1.4 Таймеры/счетчики

Таймеры/счетчики (TIMER/COUNTERS) можно использовать для точного формирования временных интервалов, подсчета импульсов микроконтроллера, формирования последовательности импульсов, тактирования приемопередатчика последовательного канала связи. В режиме ШИМ (PWM) таймер/счетчик может представлять собой широтно-импульсный модулятор и использоваться для генерирования сигнала с программируемыми частотой и скважностью. Таймеры/счетчики способны вырабатывать запросы прерываний, переключая процессор на их обслуживание по событиям и освобождая его от необходимости периодического опроса состояния таймеров. Поскольку основное применение микроконтроллеры находят в системах реального времени, таймеры/счетчики являются одним из наиболее важных элементов.

B MK Atmega 16 есть три таймера/счетчика 8-битных два Timer/Counter2) 16-битный (Timer/Counter1). (Timer/Counter0, И ОДИН Восьмибитные таймеры/счетчики Т0 и Т2 могут использоваться для отсчета временных интервалов или как счетчики внешних событий, также у них имеется по одному блоку сравнения, позволяющему реализовать 1-канальный генератор ШИМ-сигнала.

Каждый из таймеров/счетчиков содержит специальные регистры. Например, таймер TC0 содержит:

- счетный регистр TCNT0;

- регистр сравнения OCR0 (Output Compare Register);

- конфигурационный регистр TCCR0 (Timer/Counter Control Register).

Три регистра относятся ко всем трем таймерам Atmega16:

- конфигурационный регистр TIMSK (Timer/Counter Interrupt Mask Register);

- статусный регистр TIFR (Timer/Counter Interrupt Flag Register);

- регистр специальных функций SFIOR (Special Function IO Register).

**TCNTn** (n – число 0, 1 или 2) – счетный регистр. Когда таймер работает, по каждому импульсу тактового сигнала значение TCNT0 изменяется на единицу. В зависимости от режима работы таймера счетный регистр может или увеличиваться, или уменьшаться. Регистр TCNT0 можно как читать, так и записывать (для задания начального значения) (рисунок 2).

| бит                | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| чтение/запись      | R/W |

| начальное значение | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Рисунок 2 – Структура регистра TCNT0

**OCRn** – регистр сравнения, в который возможно записать какое-либо число (рисунок 3). Его значение постоянно сравнивается со счетным регистром TCNT0, и в случае совпадения таймер может выполнять какие-то действия, например, вызывать прерывание, менять состояние вывода OC0 и т. д. в зависимости от режима работы.

| бит                | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| чтение/запись      | R/W |

| начальное значение | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Рисунок 3 – Структура регистра OCRn

**TCCR0** – конфигурационный регистр таймера/счетчика Т0 определяет источник тактирования таймера, коэффициент предделителя, режим работы таймера/счетчика Т0 и поведение вывода ОС0. Очень важный регистр (рисунок 4).

| бит           | 7    | 6     | 5     | 4     | 3     | 2    | 1    | 0    |

|---------------|------|-------|-------|-------|-------|------|------|------|

|               | FOC0 | WGM00 | COM01 | COM00 | WGM01 | CS02 | CS01 | CS00 |

| чтение/запись | W    | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  |

| начальное     |      |       |       |       |       |      |      |      |

| значение      | 0    | 0     | 0     | 0     | 0     | 0    | 0    | 0    |

Рисунок 4 – Структура регистра TCCR0

Биты **CS02**, **CS01**, **CS00** (**Clock Select**) – определяют источник тактовой частоты для таймера T0 и задают коэффициент предделителя. Все возможные состояния описаны в таблице 2.

Таблица 2 – Выбор тактовой частоты таймера ТО

| CS02 | CS01 | CS00 | Описание                                                        |

|------|------|------|-----------------------------------------------------------------|

| 0    | 0    | 0    | Источника тактирования нет, таймер остановлен                   |

| 0    | 0    | 1    | Тактовая частота микроконтроллера                               |

| 0    | 1    | 0    | Тактовая частота микроконтроллера /8                            |

| 0    | 1    | 1    | Тактовая частота микроконтроллера /64                           |

| 1    | 0    | 0    | Тактовая частота микроконтроллера /256                          |

| 1    | 0    | 1    | Тактовая частота микроконтроллера /1024                         |

| 1    | 1    | 0    | Внешний источник на выводе Т0. Срабатывание по заднему фронту   |

| 1    | 1    | 1    | Внешний источник на выводе Т0. Срабатывание по переднему фронту |

Биты **WGM10**, **WGM00** (**Wave Generator Mode**) определяют режим работы таймера/счетчика Т0. Всего их может быть четыре – нормальный режим (normal), сброс таймера при совпадении (СТС) и два режима широтно-импульсной модуляции (FastPWM и Phase Correct PWM). Все возможные значения описаны в таблице 3.

Таблица 3 – Выбор режима работы таймера/счетчика ТО

| WGM01 | WGM00 | Режим работы таймера/счетчика |

|-------|-------|-------------------------------|

| 0     | 0     | Normal                        |

| 0     | 1     | PWM, Phase Correct            |

| 1     | 0     | CTC                           |

| 1     | 1     | Fast PWM                      |

Биты **COM01**, **COM00** (Compare Match Output Mode) определяют поведение вывода OC0. Если хоть один из этих битов установлен в 1, то вывод OC0 перестает функционировать как обычный вывод общего назначения и подключается к схеме сравнения таймера счетчика T0. Однако при этом он должен быть еще настроен как выход. Поведение вывода OC0 зависит от режима работы таймера/счетчика T0. В режимах normal и CTC вывод OC0 ведет себя одинаково, а вот в режимах широтно-импульсной модуляции его поведение отличается.

Последний бит регистра TCCR0 — это бит **FOC0** (Force Output Compare). Этот бит предназначен для принудительного изменения состояния вывода ОС0. Он работает только для режимов Normal и СТС. При установке бита FOC0 в единицу состояние вывода меняется соответственно значениям битов COM01, COM00. Бит FOC0 не вызывает прерывания и не сбрасывает таймер в СТС-режиме.

**TIMSK** (Timer/Counter Interrupt Mask Register) – регистр масок прерываний по таймерам/счетчикам (рисунок 5). Общий регистр для всех трех таймеров Atmega 16 содержит флаги разрешения прерываний. Таймер Т0 может

вызывать прерывания при переполнении счетного регистра TCNT0 и при совпадении счетного регистра с регистром сравнения OCR0. Соответственно для таймера T0 в регистре TIMSK зарезервированы два бита — это TOIE0 и OCIE0. Остальные биты относятся к другим таймерам.

| бит           | 7     | 6     | 5      | 4      | 3      | 2     | 1     | 0     |

|---------------|-------|-------|--------|--------|--------|-------|-------|-------|

|               | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0 | TOIE0 |

| чтение/запись | W     | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   |

| начальное     |       |       |        |        |        |       |       |       |

| значение      | 0     | 0     | 0      | 0      | 0      | 0     | 0     | 0     |

Рисунок 5 – Структура регистра TIMSK

**ТОІЕ0** – значение бита 0 запрещает прерывания по событию переполнение, а 1 – разрешает.

**ОСІЕ0** – значение 0 запрещает прерывания по событию совпадение, а 1 – разрешает.

Естественно прерывания будут вызываться, только если установлен бит глобального разрешения прерываний – бит I регистра SREG.

**TIFR** (Timer/Counter0 Interrupt Flag Register) – регистр флагов прерываний таймеров (рисунок 6).

| бит                | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    |

|--------------------|------|------|------|-------|-------|------|------|------|

|                    | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 |

| чтение/запись      | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  |

| начальное значение | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |

Рисунок 6 – Структура регистра TIFR

Общий для всех трех таймеров-счетчиков регистр. Содержит статусные флаги, которые устанавливаются при возникновении событий. Для таймера T0 — это переполнение счетного регистра TCNT0 и совпадение счетного регистра с регистром сравнения OCR0.

Если в эти моменты в регистре TIMSK разрешены прерывания и установлен бит I в регистре SREG, то микроконтроллер вызовет соответствующий обработчик.

Флаги автоматически очищаются при запуске обработчика прерывания. Также это можно сделать программно, записав 1 в соответствующий флаг.

**TOV0** – устанавливается в 1 при переполнении счетного регистра.

**ОСF0** – устанавливается в 1 при совпадении счетного регистра с регистром сравнения.

**SFIOR** (Special Function IO Register) – регистр специальных функций ввода/вывода (рисунок 7). Один из его разрядов сбрасывает 10-разрядный двоичный счетчик, который делит входную частоту для таймера Т0 и таймера

T1. Сброс осуществляется при установке бита **PSR10** (Prescaler Reset Timer/Counter1 и Timer/Counter0) в 1.

| бит                | 7     | 6     | 5     | 4 | 3    | 2   | 1    | 0     |

|--------------------|-------|-------|-------|---|------|-----|------|-------|

|                    | ADTS2 | ADTS1 | ADTS0 | - | ACME | PUD | PSR2 | PSR10 |

| чтение/запись      | R/W   | R/W   | R/W   | R | R/W  | R/W | R/W  | R/W   |

| начальное значение | 0     | 0     | 0     | 0 | 0    | 0   | 0    | 0     |

Рисунок 7 – Структура регистра SFIOR

Сторожевой таймер (WatchDog Timer, WDT) предназначен для предотвращения аварийных последствий от случайных сбоев программы. Он имеет свой собственный RC-генератор, работающий на частоте 1 МГц. Как и для основного внутреннего RC-генератора, значение 1 МГц является приближенным и зависит прежде всего от величины напряжения питания.

Идея использования сторожевого таймера состоит в регулярном его сбрасывании под управлением программы или внешнего воздействия, до того как закончится его выдержка времени и не произойдет сброс процессора. Если программа работает нормально, то команда сброса сторожевого таймера должна регулярно выполняться, предохраняя поцессор от сброса.

Если микропроцессор случайно вышел за пределы программы (например от сильной помехи) либо зациклился на каком-либо участке программы, команда сброса сторожевого таймера, скорее всего, не будет выполнена в течение достаточного времени и произойдет полный сброс процессора, инициализирующий все регистры и приводящий систему в рабочее состояние.

## 1.5 Последовательные порты

Универсальный синхронный/асинхронный приемопередатчик (Universal Synchronous/Asynchronous Receiver and Transmitter, UART или USART) — удобный и простой последовательный интерфейс для организации информационного канала обмена данными между микроконтроллером и внешним миром. Способен работать в дуплексном режиме (одновременная передача и прием данных). Поддерживает протокол стандарта RS-232, что обеспечивает возможность организации связи с персональным компьютером.

Модули USART, реализованные в микроконтроллерах семейства, могут обнаруживать следующие внештатные ситуации: переполнение; ошибка кадрирования; ошибка контроля четности.

Для уменьшения вероятности сбоев в модуле реализована функция фильтрации помех. Для взаимодействия с программой предусмотрены три прерывания, запрос на генерацию которых формируется при наступлении следующих событий: «передача завершена», «регистр данных передатчика пуст» и «прием завершен».

Модуль состоит из трех основных частей: блока тактирования, блока передатчика и блока приемника.

Блок тактирования модулей USART содержит схему синхронизации (для работы в синхронном режиме) и контроллер скорости передачи.

Блок передатчика включает одноуровневый буфер, сдвиговый регистр, схему формирования бита четности и схему управления. Блок приемника, в свою очередь, содержит схемы восстановления тактового сигнала и данных, схему контроля четности, двухуровневый буфер, сдвиговый регистр, а также схему управления.

Буферные регистры приемника и передатчика располагаются по одному адресу пространства ввода/вывода и обозначаются как регистр данных UDR. В этом регистре хранятся младшие 8 бит принимаемых и передаваемых данных. При чтении регистра UDR выполняется обращение к буферному регистру приемника, при записи — к буферному регистру передатчика. В модулях USART буфер приемника является двухуровневым (FIFO-буфер), изменение состояния которого происходит при любом обращении к регистру UDR. В связи с этим не следует использовать регистр UDR в качестве операндов команд типа «чтение/модификация/запись» (SBI и CBI). Кроме того, следует быть аккуратными при использованием команд проверки SBIC и SBIS, поскольку они также изменяют состояние буфера приемника.

Для управления модулями USART используются три регистра: UCSRA, UCSRB и UCSRC (таблицы 4–7).

Таблица 4 – UCSRA (регистр управления)

| № бита      | 7   | 6   | 5    | 4  | 3   | 2   | 1               | 0               |

|-------------|-----|-----|------|----|-----|-----|-----------------|-----------------|

| Имя бита    | RXC | TXC | UDRE | FE | DOR | UPE | U2X             | MPCM            |

| Доступность | R   | R\W | R    | R  | R   | R   | $R\backslash W$ | $R\backslash W$ |

Таблица 5 – Описание разрядов регистра UCSRA

| Разряд | Название | Описание                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | RXC      | Флаг завершения приема. Флаг устанавливается в 1 при наличии                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |          | непрочитанных данных в буфере приемника (регистр данных UDR). Сбрасывается флаг аппаратно после опустошения буфера (в UART – после прочтения регистра данных). Если разряд RXCIE регистра UCSRB установлен, то при установке флага генерируется запрос на прерывание – «прием завершен»                                                                                                                                                                         |

| 6      | TXC      | Прерывание — «прием завершен»  Флаг завершения передачи. Флаг устанавливается в 1 после передачи всех разрядов посылки из сдвигового регистра передатчика при условии, что в регистр данных UDR не было загружено нового значения. Если разряд TXCIE регистра UCSRB (UCSRnB) установлен, то при установке флага генерируется прерывание «передача завершена». Флаг сбрасывается аппаратно при обработке прерывания или программно — записью в него логической 1 |

| Разряд | Название | Описание                                                            |  |  |  |  |  |  |

|--------|----------|---------------------------------------------------------------------|--|--|--|--|--|--|

| 5      | UDRE     | Флаг опустошения регистра данных. Данный флаг устанавливается в 1   |  |  |  |  |  |  |

|        |          | ри пустом буфере передатчика (после пересылки байта из регистра     |  |  |  |  |  |  |

|        |          | анных UDR в сдвиговый регистр передатчика). Установленный флаг      |  |  |  |  |  |  |

|        |          | значает, что в регистр данных можно загружать новое значение. Если  |  |  |  |  |  |  |

|        |          | разряд UDRIE регистра UCR (UCSRB) установлен, генерируется запрос   |  |  |  |  |  |  |

|        |          | на прерывание – «регистр данных пуст». Флаг сбрасывается аппаратно  |  |  |  |  |  |  |

|        |          | при записи в регистр данных                                         |  |  |  |  |  |  |

| 4      | FE       | Флаг ошибки кадрирования. Флаг устанавливается в 1 при обнаружении  |  |  |  |  |  |  |

|        |          | ошибки кадрирования, если первый стоп-бит принятой посылки равен 0. |  |  |  |  |  |  |

|        |          | Флаг сбрасывается при приеме стоп-бита, равного 1                   |  |  |  |  |  |  |

| 3      | DOR      | Флаг переполнения. В USART флаг устанавливается в 1, если в момент  |  |  |  |  |  |  |

|        |          | обнаружения нового старт-бита в сдвиговом регистре приемника        |  |  |  |  |  |  |

|        |          | находится последнее принятое слово, а буфер приемника полон. В      |  |  |  |  |  |  |

|        |          | UART флаг устанавливается в 1, если новый кадр будет помещен в      |  |  |  |  |  |  |

|        |          | сдвиговый регистр приемника до того, как из регистра данных будет   |  |  |  |  |  |  |

|        |          | считано предыдущее слово. Флаг сбрасывается при пересылке           |  |  |  |  |  |  |

|        |          | принятых данных из сдвигового регистра приемника в буфер            |  |  |  |  |  |  |

| 2      | PE       | Флаг ошибки контроля четности. Флаг устанавливается в 1, если в     |  |  |  |  |  |  |

|        |          | данных, находящихся в буфере приемника, выявлена ошибка контроля    |  |  |  |  |  |  |

|        |          | четности                                                            |  |  |  |  |  |  |

| 1      | U2X      | Удвоение скорости обмена. Если этот разряд установлен в 1,          |  |  |  |  |  |  |

|        |          | коэффициент деления предделителя контроллера скорости передачи      |  |  |  |  |  |  |

|        |          | уменьшается с 16 до 8, удваивая тем самым скорость асинхронного     |  |  |  |  |  |  |

|        |          | обмена по последовательному каналу. В USART разряд U2X              |  |  |  |  |  |  |

|        | MDCM     | используется только при асинхронном режиме работы                   |  |  |  |  |  |  |

| 0      | MPCM     | Режим мультипроцессорного обмена. Разряд МРСМ используется в        |  |  |  |  |  |  |

|        |          | режиме мультипроцессорного обмена. Если он установлен в 1, ведомый  |  |  |  |  |  |  |

|        |          | микроконтроллер ожидает приема кадра, содержащего адрес             |  |  |  |  |  |  |

Таблица 6 – Описание разрядов регистра UCSRB

| Разряд | Название | Описание                                                               |  |  |  |  |  |  |

|--------|----------|------------------------------------------------------------------------|--|--|--|--|--|--|

| 7      | RXCIE    | Разрешение прерывания по завершении приема. Если разряд установлен     |  |  |  |  |  |  |

|        |          | 1, то при установке флага RXC регистра UCSRA генерируется              |  |  |  |  |  |  |

|        |          | прерывание «прием завершен» (если флаг I регистра SREG установлен в 1) |  |  |  |  |  |  |

| 6      | TXCIE    | Разрешение прерывания по завершении передачи. Если данный разряд       |  |  |  |  |  |  |

|        |          | установлен в 1, то при установке флага ТХС регистра UCSRA              |  |  |  |  |  |  |

|        |          | генерируется прерывание «передача завершена» (если флаг I регистра     |  |  |  |  |  |  |

|        |          | SREG установлен в 1)                                                   |  |  |  |  |  |  |

| 5      | UDRIE    | Разрешение прерывания при очистке регистра данных UART. Если           |  |  |  |  |  |  |

|        |          | данный разряд установлен в 1, то при установке флага                   |  |  |  |  |  |  |

|        |          | UDRE регистра UCSRA генерируется прерывание – «регистр данных          |  |  |  |  |  |  |

|        |          | пуст» (если флаг I регистра SREG установлен в 1)                       |  |  |  |  |  |  |

| 4      | RXEN     | Разрешение приема. При установке этого разряда в 1 разрешается         |  |  |  |  |  |  |

|        |          | работа приемника USART/UART и переопределяется                         |  |  |  |  |  |  |

|        |          | функционирование вывода RXD (RXDn). При сбросе разряда RXEN            |  |  |  |  |  |  |

|        |          | работа приемника запрещается, а его буфер сбрасывается. Значения       |  |  |  |  |  |  |

|        |          | флагов ТХС, DOR/OR и FE при этом становятся недействительными          |  |  |  |  |  |  |

| Разряд | Название | Описание                                                            |  |  |  |  |  |  |

|--------|----------|---------------------------------------------------------------------|--|--|--|--|--|--|

| 3      | TXEN     | Разрешение передачи. При установке этого разряда в 1 разрешается    |  |  |  |  |  |  |

|        |          | абота передатчика UART и переопределяется функционирование          |  |  |  |  |  |  |

|        |          | ывода TXD. Если разряд сбрасывается в 0 во время передачи,          |  |  |  |  |  |  |

|        |          | выключение передатчика произойдет только после завершения           |  |  |  |  |  |  |

|        |          | передачи данных, находящихся в сдвиговом регистре и буфере          |  |  |  |  |  |  |

| 2      | UCSZ2    | Формат посылок. Этот разряд используется для задания размера        |  |  |  |  |  |  |

|        |          | передаваемых слов данных. В модулях USART он используется           |  |  |  |  |  |  |

|        |          | овместно с разрядами UCSZ1:0 регистра UCSRC. В модулях UART,        |  |  |  |  |  |  |

|        |          | сли разряд CHR9 установлен в 1, осуществляется передача и прием     |  |  |  |  |  |  |

|        |          | девятиразрядных данных, если сброшен – восьмиразрядных              |  |  |  |  |  |  |

| 1      | RXB8     | 8-й разряд принимаемых данных. При использовании девятиразрядных    |  |  |  |  |  |  |

|        |          | слов данных этот разряд содержит значение старшего разряда          |  |  |  |  |  |  |

|        |          | принятого слова. В случае USART содержимое этого разряда должно     |  |  |  |  |  |  |

|        |          | быть считано до прочтения регистра данных UDR                       |  |  |  |  |  |  |

| 0      | TXB8     | 8-й разряд передаваемых данных. При использовании девятиразрядных   |  |  |  |  |  |  |

|        |          | слов данных содержимое этого разряда является старшим разрядом      |  |  |  |  |  |  |

|        |          | передаваемого слова. Требуемое значение должно быть занесено в этот |  |  |  |  |  |  |

|        |          | разряд до загрузки байта данных в регистр UDR                       |  |  |  |  |  |  |

Таблица 7 – Описание разрядов регистра UCSRC

| Разряд | Название | Описание                                                               |  |  |  |  |  |  |

|--------|----------|------------------------------------------------------------------------|--|--|--|--|--|--|

| 7      | URSEL    | выбор регистра. Этот разряд определяет, в какой из регистров модуля    |  |  |  |  |  |  |

|        |          | роизводится запись. Если разряд установлен в 1, обращение              |  |  |  |  |  |  |

|        |          | производится к регистру UCSRC. Если же разряд сброшен в 0,             |  |  |  |  |  |  |

|        |          | обращение производится к регистру UBRRH                                |  |  |  |  |  |  |

| 6      | UMSEL    | Режим работы USART. 0 – модуль USART работает в асинхронном            |  |  |  |  |  |  |

|        |          | режиме; 1 – модуль USART работает в синхронном режиме                  |  |  |  |  |  |  |

| 5      | UPM1     | Режим работы контроля и формирования четности. Разряды определяют      |  |  |  |  |  |  |

| 4      | UPM0     | функционирование схем контроля и формирования четности                 |  |  |  |  |  |  |

| 3      | USBS     | Этот разряд определяет количество стоп-битов, посылаемых               |  |  |  |  |  |  |

|        |          | передатчиком. Разряд в «0» – передатчик посылает 1 стоп-бит, если в 1, |  |  |  |  |  |  |

|        |          | то 2 стоп-бита. Для приемника содержимое этого разряда безразлично     |  |  |  |  |  |  |

| 2      | UCSZ1    | Формат посылок. Совместно с разрядом UCSZ2 эти разряды                 |  |  |  |  |  |  |

| 1      | UCSZ0    | определяют количество разрядов данных в посылках (размер слова)        |  |  |  |  |  |  |

| 0      | UCPOL    | Полярность тактового сигнала. Значение этого разряда определяет        |  |  |  |  |  |  |

|        |          | момент выдачи и считывания данных на выводах модуля. Используется      |  |  |  |  |  |  |

|        |          | только в синхронном режиме. В асинхронном режиме разряд сброшен в 0    |  |  |  |  |  |  |

## Скорость приема/передачи USART

В асинхронном режиме, а также в синхронном режиме при работе в качестве ведущего скорость приема и передачи данных задается контроллером скорости передачи, функционирующим как делитель системного тактового сигнала с программируемым коэффициентом деления. Коэффициент определяется содержимым регистра контроллера UBRR (таблица 8). В блок приемника сформированный сигнал поступает сразу, а в блок передатчика – через дополнительный делитель, коэффициент деления которого (2, 8 или 16) зависит от режима работы модуля USART/UART. Регистр UBRR является

12-разрядным и физически размещается в двух регистрах ввода/вывода UBRRH и UBRRL.

При работе в асинхронном режиме скорость обмена определяется не только содержимым регистра UBRR, но и состоянием разряда U2X регистра UCSRA. Если этот разряд установлен в 1, коэффициент деления предделителя уменьшается в два раза, а скорость обмена соответственно удваивается. При работе в синхронном режиме этот разряд должен быть сброшен.

Скорость обмена определяется следующими формулами:

- асинхронный режим (обычный, U2Xn = 0) BAUD = fCK/16(UBRR + 1);

- асинхронный режим (ускоренный, U2Xn = 1) BAUD = fCK/8(UBRR + 1);

- синхронный режим ведущего BAUD = fCK/2(UBRR + 1).

Здесь BAUD – скорость передачи в бодах; fCK – тактовая частота микроконтроллера; UBRR – содержимое регистра контроллера скорости передачи (0–4095).

Таблица 8 – Определение размера слова данных

| UCSZ2 | UCSZ1 | UCSZ0 | Размер слова данных |

|-------|-------|-------|---------------------|

| 0     | 0     | 0     | 5 бит               |

| 0     | 0     | 1     | 6 бит               |

| 0     | 1     | 0     | 7 бит               |

| 0     | 1     | 1     | 8 бит               |

| 1     | 0     | 0     | Зарезервировано     |

| 1     | 0     | 1     | Зарезервировано     |

| 1     | 1     | 0     | Зарезервировано     |

| 1     | 1     | 1     | 9 бит               |

Последовательный периферийный трехпроводный интерфейс SPI (Serial Peripheral Interface) предназначен для организации обмена данными между двумя устройствами. С его помощью может осуществляться обмен данными между микроконтроллером и различными устройствами, такими, как цифровые потенциометры, ЦАП/АЦП, FLASH-ПЗУ и др. Кроме того, через интерфейс SPI может осуществляться программирование микроконтроллера.

Двухпроводной последовательный интерфейс TWI (Two-wire Serial Interface) является полным аналогом базовой версии интерфейса I2C (двухпроводная двунаправленная шина). Этот интерфейс позволяет объединить вместе до 128 различных устройств с помощью двунаправленной шины, состоящей из линии тактового сигнала (SCL) и линии данных (SDA).

**Аналого-цифровой преобразователь** (A/D CONVERTER) служит для получения числового значения напряжения, поданного на его вход. Этот результат сохраняется в регистре данных АЦП. Какой из выводов микроконтроллера будет являться входом АЦП, определяется числом, занесенным в соответствующий регистр.

Расположение выводов микроконтроллера (цоколевка) в варианте исполнения корпуса DIP показано на рисунке 8. Упрощенная архитектура ядра микроконтроллеров AVR семейства Меда показана на рисунке 9.

Рисунок 8 – Расположение выводов микроконтроллера Atmega 16

Рисунок 9 – Упрощенная архитектура ядра микроконтроллеров семейства Меда

**Аналоговый компаратор** (Analog Comparator, AC) сравнивает напряжения на двух выводах микроконтроллера. Результатом сравнения будет логическое значение, которое может быть прочитано из программы. Выход аналогового компаратора можно включить на прерывание от аналогового компаратора. Пользователь может установить срабатывание прерывания по нарастающему или спадающему фронту или по переключению.

**Четырехпроводной интерфейс JTAG** используется для тестирования печатных плат, внутрисхемной отладки, программирования микроконтроллеров. Многие микроконтроллеры семейства Mega имеют совместимый с IEEE Std 1149.1 интерфейс JTAG или debugWIRE для встроенной отладки. Кроме того, все микроконтроллеры Mega с flash-памятью емкостью 16 Кбайт и более могут программироваться через интерфейс JTAG.

**Тактовый генератор** вырабатывает импульсы для синхронизации работы всех узлов микроконтроллера. Внутренний тактовый генератор AVR может запускаться от нескольких источников опорной частоты (внешний генератор, внешний кварцевый резонатор, внутренняя или внешняя RC-цепочка). Минимальная допустимая частота ничем не ограничена (вплоть до пошагового режима). Максимальная рабочая частота определяется конкретным типом микроконтроллера.

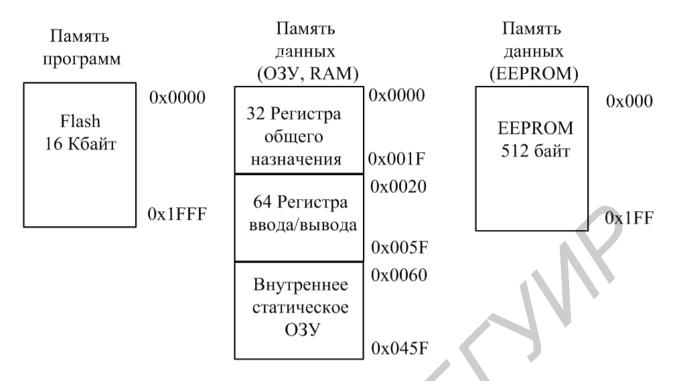

### 1.6 Организация памяти

Память МК с гарвардской архитектурой разделяется на две различные области – память программ (Program Memory) и память данных (Data Memory). Эти области разделены на два непересекающихся адресных пространства, имеют разное назначение, размер и тип ячеек. Разделение адресных пространств обеспечивается системой команд и способами адресации.

**Память программ** (ПП) служит для хранения кодов программы и констант. Физическим носителем ПП выступает энергонезависимое постоянное запоминающее устройство (ПЗУ) типа FlashROM. Память программ располагается только в кристалле. Объем памяти микроконтроллера Atmega 16 составляет  $16 \times 1024$  16-битных слов. Это и определяет разрядность регистра счетчика команд (РС, Program Counter), используемого для адресации памяти программ. Размер счетчика команд составляет 12 бит в зависимости от объема адресуемой памяти.

Память программ логически разделена на две части: область прикладной программы область загрузчика. В последней может располагаться специальная (загрузчик), позволяющая микроконтроллеру программа самостоятельно управлять загрузкой и выгрузкой прикладных программ. Если же возможность самопрограммирования у микроконтроллера не используется, прикладная программа может располагаться и в области загрузчика. Карта памяти микроконтроллера Atmega 16 приведена на рисунке 10.

Рисунок 10 – Карта памяти микроконтроллера Atmega 16

По адресу 0x0000 памяти программ находится вектор сброса. Выполнение программы начинается с этого адреса после инициализации (сброса) микроконтроллера (по этому адресу должна размещаться команда перехода к инициализационной части программы). Начиная с адреса 0x0002 памяти программ, располагается таблица векторов прерываний.

**Память данных** имеет байтовую организацию и адресное пространство объемом до 64 Кбайт (16-битный адрес). Память данных микроконтроллера разделена на три части:

- регистровая память;

- оперативная память (статическое ОЗУ);

- энергонезависимое ЭСППЗУ (EEPROM).

**Регистровая память** включает 32 регистра общего назначения (РОН), объединенных в файл, и служебные регистры ввода/вывода (РВВ). В обеих областях регистров ввода/вывода располагаются различные служебные регистры (регистр управления микроконтроллера, регистр состояния), а также регистры управления периферийными устройствами, входящими в состав микроконтроллера. РОН — наиболее интенсивно используемая память для размещения данных и указателей.

Статическое ОЗУ объемом 1 Кбайт используют для хранения переменных помимо РОН. Микроконтроллер имеет возможность подключения внешнего статического ОЗУ объемом до 64 Кбайт. В адресном пространстве ОЗУ также расположены все регистры микроконтроллера, под них отведены младшие 96 (256) адресов, остальные адреса отведены под ячейки статического ОЗУ.

**EEPROM-память** используют для долговременного хранения различной информации, которая может изменяться в процессе функционирования готовой

системы (калибровочные константы, серийные номера, ключи). Ее объем составляет 512 Кбайт. Эта память расположена в отдельном адресном пространстве, а доступ к ней осуществляется с помощью определенных регистров ввода/вывода.

Стек — это особая область памяти данных, используемая процессором для временного хранения адресов возврата из подпрограмм, промежуточных результатов вычислений и т. д. В Atmega 16 стек реализован программно. Он размещается в памяти данных и должен начинаться от максимального адреса RAM. По мере заполнения стека его граница смещается к младшим адресам (стек растет вверх, адрес в указателе стека уменьшается). Предельное минимальное значение указателя стека для микроконтроллера Atmega 16 — 0х60, поскольку дальше начинается область SFR (Special Function Registers, регистры специального назначения).

В качестве указателя стека используется пара регистров ввода/вывода SPH и SPL, расположенных по адресам 0x3E (0x5E) и 0x3D (0x5D) соответственно.

Так как после подачи напряжения питания (или после сброса) в регистрах содержится нулевое значение, в самом начале программы указатель стека необходимо проинициализировать, записав в него значение верхнего адреса памяти данных. Например:

ldi r16, low(RAMEND) ;Загрузим в рабочий регистр младший байт значения out SPL, rl6 ;Инициализируем указатель стека ldi r16, high(RAMEND) оит SPH, rl6 ;Инициализируем указатель стека

При вызове подпрограмм адрес команды, расположенной за командой вызова, сохраняется в стеке. Значение указателя стека при этом уменьшается на 2 или 3 в зависимости от размера счетчика команд. При возврате из подпрограммы этот адрес извлекается из стека и загружается в счетчик команд. Значение указателя стека соответственно увеличивается на 2 (3). То же происходит и во время прерывания. При генерации прерывания адрес следующей команды сохраняется в стеке, а при возврате из подпрограммы обработки прерывания он восстанавливается из стека. Стек доступен и программно. Для работы со стеком имеются две команды: команда занесения в стек (PUSH) и команда извлечения из стека (POP).

## 1.7 Регистры управления

Регистр состояния (статуса или признаков) программ SREG содержит флаги, показывающие текущее состояние микроконтроллера (таблица 9). После сигнала сброса инициализируется нулями. Каждый из восьми разрядов (битов) регистра называется флагом, который может быть установлен в 1 (в этом случае считается, что флаг установлен) или сброшен в 0 (в этом случае считается, что флаг сброшен). Большинство флагов сбрасывается или устанавливается автоматически в зависимости от результатов выполненной операции.

Таблица 9 – SREG (регистр состояния программ)

| № бита      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Имя бита    | I   | T   | Н   | S   | V   | N   | Z   | C   |

| Доступность | R/W |

Флаг I (бит 7) — общее разрешение прерываний (Global Interrupt). Для разрешения прерываний этот флаг должен быть установлен в 1. Если флаг сброшен, то прерывания запрещены независимо от состояния битов регистра масок прерываний. Флаг сбрасывается аппаратно после входа в прерывание и восстанавливается командой RETI.

Флаг Т (бит 6) — хранение копируемого бита (Transfer or Copy). Этот разряд можно использовать как ячейку для временного хранения информации размерностью в один бит. Бит регистра используется в качестве источника или приемника командами копирования битов BLD (Bit LoaD) и BST (Bit STore).

Флаг H (бит 5) — флаг половинного переноса (Half Carry). Этот флаг устанавливается в 1, если произошел перенос из младшей половины байта (тетрады) или заем из старшей половины байта при выполнении некоторых арифметических операций.

**Флаг S** (бит 4) — флаг знака (Sign). Этот флаг равен результату операции «Исключающее ИЛИ» (XOR) между флагами N и V. Этот флаг устанавливается в 1, если результат выполнения арифметической операции меньше нуля.

**Флаг V** (бит 3) — флаг переполнения дополнительного кода (Two's complement Overflow). Этот флаг устанавливается в 1 при переполнении числа в дополнительном коде. Используется при работе со знаковыми числами, представленными в дополнительном коде. В дополнительном коде записываются отрицательные числа.)

**Флаг N** (бит 2) — флаг отрицательного значения (Negaive). Этот флаг устанавливается в 1, если старший бит результата операции равен 1. Указывает на отрицательный результат арифметической или логической операции.

**Флаг Z** (бит 1) – флаг нуля (Zero). Этот флаг устанавливается в 1, если результат выполнения операции равен нулю.

**Флаг С** (бит 0) – флаг переноса (Carry). Этот флаг устанавливается в 1, если в результате выполнения операции произошел выход за границы байта (результат занимает 9 бит).

Биты регистра управления микроконтроллера **MCUCR** управляют выполнением основных функций (таблица 10).

Таблица 10 – MCUCR (регистр управления микроконтроллером)

| № бита      | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|-------------|-----|-----|-----|-----|-------|-------|-------|-------|

| Имя бита    | SM2 | SE  | SM1 | SM0 | ISC11 | ISC10 | ISC01 | ISC00 |

| Доступность | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

Биты регистра MCUCR отвечают за выбор режимов энергопотребления и условия генерации внешних прерываний (таблицы 11 и 12).

**Бит SE** – разрешение перехода в режим пониженного энергопотребления. Установка этого бита в 1 разрешает перевод микроконтроллера в режим пониженного энергопотребления. Переключение осуществляется по команде SLEEP.

**Биты SM2, SM1, SM0** – выбор режима пониженного энергопотребления. Состояние этих битов определяет, в какой режим перейдет микроконтроллер после выполнения команды SLEEP.

Таблица 11 – Режимы энергопотребления

| SM2 | SM2 | SM2 | Режим энергопотребления                        |  |  |

|-----|-----|-----|------------------------------------------------|--|--|

| 0   | 0   | 0   | Idle (режим холостого хода)                    |  |  |

| 0   | 0   | 1   | ADC Noise Reduction (режим снижения шумов АЦП) |  |  |

| 0   | 1   | 0   | Power Down (режим микропотребления)            |  |  |

| 0   | 1   | 1   | Power Save (экономичный режим),                |  |  |

| 1   | 1   | 0   | Standby (режим ожидания)                       |  |  |

Биты **ISC11**, **ISC00** – определяют условия генерации внешних прерываний.

Таблица 12 – Условия генерации внешних прерываний

|                   |                   | трорывании                            |

|-------------------|-------------------|---------------------------------------|

| ISCn1, $n = 0, 1$ | ISCn0, $n = 0, 1$ | Условие                               |

| 0                 | 0                 | По низкому уровню на выходе INTn      |

| 1                 | 0                 | По спадающему фронту на выходе INTn   |

| 1                 | 1                 | По нарастающему фронту на выходе INTn |

|                   |                   |                                       |

### 2 СИСТЕМА КОМАНД АТМЕСА 16

### 2.1 Режимы адресации

Формат команды описывает структуру машинного слова команды. Часть битов выделяют под код операции («что делать»), это обязательная часть любой команды. Остальные биты указывают операнды («над чем это делать»), т. е. данные, адрес ячейки данных или адрес перехода. Различают команды безоперандные, одно- и двухоперандные.

В двухоперандных командах обработки данных один из операндов называется источником [source], его содержимое не изменяется, другой – приемником [destination], в него заносится результат операции. Если команда имеет два операнда, то сначала указывают приемник, затем источник. Между приемником и источником обязательно должна стоять запятая (с любым числом пробелов до или после нее или вообще без них). Например, выражение sub r16, r17 означает, что из содержимого r16 нужно вычесть содержимое r17, а результат окажется в r16.

Команда = Операция + Операнд.

Способы адресации определяют способы указания (представления) операндов.

Реализованы следующие способы адресации для охвата всей памяти:

- прямая;

- регистровая;

- непосредственная;

- битовая;

- косвенная;

- косвенная со смещением;

- косвенная с предварительным декрементом;

- косвенная с последующим инкрементом.

При **прямой адресации** числовая константа в команде обозначает адрес ячейки памяти, содержимое которой является операндом команды. Данный способ адресации может применяться при обращении к любой ячейке адресного пространства SRAM. Имеются всего две команды: LDS и STS, каждая длиной в два слова (32 разряда). Первое слово содержит код операции и адрес регистра общего назначения, второе — 16-разрядный адрес ячейки, к которой направлено обращение. Например, LDS R16, 0x0200 — занести в регистр R16 значение, хранящееся в ячейке памяти с адресом 0x0200.

**Регистровая адресация** подразумевает, что операнд адресуется именем регистра.

Регистровая адресация с одним регистром. При этом способе адресации данные находятся в регистре Rd. Примером команд, использующих этот метод адресации, являются команды для работы со стеком (PUSH, POP) и обмена тетрадами в регистре (SWAP).

Регистровая адресация с двумя регистрами. Данный способ адресации применяется в командах, которые используют два регистра общего назначения: Rd и Rr. Этот вид адресации используют команды пересылки данных из регистра в регистр и большинство команд арифметических операций, а также ряд команд логических операций. При этих операциях результат сохраняется в регистре Rd. Например, ADD R16, R17.

Адресация регистра ввода/вывода. Этот вид адресации используют для выполнения обмена данных между регистром ввода/вывода, расположенным в адресном пространстве ввода/вывода, и одним из регистров общего назначения по командам IN и OUT. Например, OUT DDRA, R16 – занести в регистр DDRA значение, хранящееся в регистре R16.

**Непосредственная адресация.** Данные указываются непосредственно в виде константы в самой команде, а не в виде адреса. Непосредственная адресация используется командой пересылки константы в регистр LDI, а также некоторыми командами арифметических и логических операций. Например, LDI R16, 255 — занести в регистр R16 число 255.

**Битовая адресация.** Этот вид адресации позволяет указать один из восьми битов любого из 32 регистров общего назначения или первой половины регистров ввода/вывода с номерами 0-31, а также регистра SREG. Для этого нужно указать имя регистра общего назначения Ri (i=0...31) либо имя регистра ввода/вывода Pi (i=0-31), либо имя SREG и номер бита b (b=0-7). Командами SBI и CBI осуществляется установка в 1 и сброс в 0 указанного бита регистра ввода/вывода, командами BLD, BST — обмен значениями бита T из регистра SREG и адресованного бита из регистра общего назначения.

Помимо этого есть группа команд битовых операций, обеспечивающая установку и сброс битов регистра состояния SREG. При записи мнемоники команд допускается использование символических (штатных) имен регистров ввода/вывода и имен битов. Существует группа команд условного перехода, где в качестве условия используется либо значение бита в регистре общего назначения (SBRC, SBRS), либо значение бита в регистре ввода/вывода (SBIC, SBIS). Например, sbic PINA, 7 – пропустить следующую команду, если бит 7 в регистре PINA равен нулю.

**Косвенная адресация памяти данных (indirect addressing).** Последние шесть регистров общего назначения (регистры R26-R31) используются как регистры-указатели для косвенной адресации. Для этого они объединяются в три 16-разрядных регистра X, Y и Z (рисунок 11).

При косвенной адресации обращение направлено к ячейке памяти, адрес которой находится в 16-разрядном индексном регистре X, Y или Z. В роли этих регистров выступают пары регистров R26, R27 (регистр X), R28, R29 (регистр Y) и R30, R31 (регистр Z). Иначе говоря, операндом является содержимое ячейки памяти, адрес которой записан в индексном регистре. Применяется для адресации в массивах и переменных указателях.

| Регистр Х | R27 (XH) | R26 (XL) |

|-----------|----------|----------|

| Регистр Ү | R29 (YH) | R28 (YL) |

| Регистр Z | R31 (ZH) | R30 (ZL) |

Рисунок 11 – Регистры-указатели X, Y и Z

Существует несколько разновидностей косвенной адресации.

**Косвенная адресация памяти данных со смещением** (indirect addressing with displacement). При этом способе адрес ячейки памяти определяется путем суммирования содержимого индексного регистра У или Z с 6-разрядным смещением, задаваемым в команде. Этот способ адресации используют команды LDD (пересылка байта из ячейки памяти SRAM в регистр Rd) и STD (пересылка байта из регистра Rr в ячейку SRAM). Позволяет получить доступ ко всем элементам в структуре путем указания на первый элемент структуры (через адрес указателя) и добавления смещения к адресу указателя (смещение указывает на нужное поле в структуре), причем значение указателя не изменяется. Также этот режим доступа используется для доступа к переменным в программном стеке и для доступа к ячейкам массива.

**Косвенная адресация памяти данных с предекрементом** (indirect addressing with pre-decrement). При этом способе адресации содержимое индексного регистра X, Y или Z сначала уменьшается на 1, а затем производится обращение к памяти по полученному адресу. Этот способ адресации используют команды LD (пересылка байта данных из памяти в регистр Rd) и ST (пересылка байта данных из регистра Rr в память), всего шесть команд — по две для каждого регистра. Применяется для эффективного доступа к элементам массива и к переменным указателя, когда нужен декремент указателя до доступа.

Косвенная адресация памяти данных с постинкрементом (indirect addressing with post-increment). При этом способе адресации содержимое индексного регистра X, Y или Z сначала используется в качестве адреса обращения к памяти данных, а затем увеличивается на 1. Этот способ адресации используют команды LD (пересылка байта данных из памяти в регистр Rd) и ST (пересылка байта данных из регистра Rr в память), всего шесть команд – по две для каждого регистра. Применяется для эффективного доступа к элементам массива и к переменным указателя, когда нужен инкремент указателя после доступа.

**Относительная адресация памяти программ.** При этом способе адрес вычисляют путем сложения содержимого программного счетчика РС и константы к задаваемой в команде. Относительную адресацию используют команды относительного перехода (RJMP) и относительного вызова подпрограммы (RCALL), многочисленная группа команд условных переходов.

### Структура программы на ассемблере

AVR-ассемблер не различает регистр букв.

Обязательным полем в строке является команда или директива.

Любая строка может начинаться с метки, которая является набором символов, заканчивающимся двоеточием. Метки используются для указания места, в которое передается управление при переходах, а также для задания имен переменных (позволяет перейти на эту строку из другого места программы). Метка не может начинаться с числа и совпадать с названием команды или регистра. Метка всегда заканчивается символом двоеточие (:). Метка может не находиться в одной строке с командой.

Комментарии отделяются от исполняемой строки символом «;» или символом «\\». Текст после точки с запятой (;) и до конца строки игнорируется компилятором.

Haпример label: .EQU var1=100; Устанавливает var1 равным 100.

Написание грамотных комментариев позволяет упростить понимание кода на ассемблере для самого автора программы (через какое-то время) и для других людей, работающих с этим кодом. Комментарий должен описывать, что было сделано и для чего это было сделано.

Входная строка может иметь одну из следующих форм:

метка: директива операнды; комментарий

метка: инструкция операнды; комментарий

; комментарий

### Форматы представления чисел

В некоторые команды можно включать числовые значения. Числа по умолчанию считаются десятичными. Существуют следующие форматы представления чисел:

- десятичный (принят по умолчанию): 10, 255;

- шестнадцатеричный (два варианта записи): как в языке Си (0xFF3) или как в языке Pascal (\$FF3). Не допускается форма записи типа FF3h;

- двоичный: 0b00001010, 0b111111111;

- восьмеричный (начинаются с нуля): 010, 077.

### Выражения

При записи команд на ассемблере могут использоваться выражения, по которым в процессе ассемблирования программы вычисляются значения. Операндами выражений могут быть:

- числа (десятичные, шестнадцатеричные и двоичные);

- метки;

- коды символов ASCII ('A') и строки ASCII;

- символические имена, представляющие переменные, определенные директивой .SET, и константы, определенные директивой .EQU;

- текущее значение счетчика команд (РС).

Помимо операндов в выражения могут входить функции, например:

- Low (выражение) возвращает младший байт выражения;

- High (выражение) возвращает старший байт выражения;

- $Exp2 (N) возвращает <math>2^{N}$ ;

- $Log 2 (N) возвращает целую часть <math>log_2 N$ .

При записи выражений можно использовать операции отношения.

### Операторы

Компилятор поддерживает ряд операторов, которые перечислены в таблице 13 (чем выше положение в таблице, тем выше приоритет оператора). Выражения могут заключаться в круглые скобки, такие выражения вычисляются перед выражениями за скобками.

Таблица 13 – Операторы AVR-ассемблера

| Приоритет | Символ     | Описание                 |

|-----------|------------|--------------------------|

| 14        | !          | Логическое отрицание     |

| 14        | ~          | Побитное отрицание       |

| 14        | -          | Минус                    |

| 13        | *          | Умножение                |

| 13        | /          | Деление                  |

| 12        | +          | Суммирование             |

| 12        | -          | Вычитание                |

| 11        | <<         | Сдвиг влево              |

| 11        | >>         | Сдвиг вправо             |

| 10        | <          | Меньше чем               |

| 10        | <=         | Меньше или равно         |

| 10        | >          | Больше чем               |

| 10        | >=         | Больше или равно         |

| 9         | =          | Равно                    |

| 9         | ! <b>=</b> | Не равно                 |

| 8         | &          | Побитное И               |

| 7         | ٨          | Побитное исключающее ИЛИ |

| 6         |            | Побитное ИЛИ             |

| 5         | &&         | Логическое И             |

| 4         |            | Логическое ИЛИ           |

Пример использования оператора побитного отрицания (~):

ldi r16, ~0xf0; Загрузить в регистр r16 число 0x0f.

Пример использования оператора суммирования (+):

ldi r30, c1+c2; Загрузить в регистр r30 сумму переменных c1 и c2.

## 2.2 Команды Atmega 16

Система команд Atmega 16 содержит 131 инструкцию. Как и для большинства других МК, этот набор можно условно разделить на четыре основные группы:

- арифметико-логические, включая сдвиги (собственно вычисления);

- передачи данных между ячейками памяти МК;

- ветвлений (переходов) в программе (формируют структуру программы);

- работы с битами.

По формату обрабатываемых данных различают команды, оперирующие с байтами и битами. Отдельные команды работают с 2-байтными числами.

Ниже при описании команд использованы следующие обозначения:

Rd – регистр-приемник, место, куда сохраняется результат выполнения команды;

Rr — регистр-источник в двухоперандных командах. Его значение после выполнения команды не изменяется;

Rdl – пара регистров R24, R26, R28, R30. Для инструкций ADIW и SBIW;

P, b -разряд b (b = 0, ..., 7) порта P;

Rr(b) – разряд b(b = 0, ..., 7) регистра Rr;

Х, Ү, Z – регистры косвенной адресации;

n – номер бита в регистре (от 0 до 7);

s – номер разряда в регистре SREG (от 0 до 7);

РС – содержимое программного счетчика;

К – восьмиразрядная константа данных. Используется в операциях с регистрами общего назначения R16–R31;

k – шестнадцатиразрядная адресная константа;

q – 6-разрядное смещение при работе с памятью данных;

STACK – область памяти SRAM, адресуемая указателем стека SP;

C, Z, N, V, S, H, T, I – биты регистра состояния SREG;

d, r = 0...31 во всех случаях (кроме специально отмеченных);

\_\_\_ инверсия;

• – логическое И;

V – логическое ИЛИ;

⊕ – исключающее ИЛИ.

**Команды передачи данных.** К этой группе относятся команды, которые переносят данные из одной области памяти в другую (включая регистры). Команды этой группы приведены в таблице 14.

Таблица 14 – Команды передачи данных

| Тиозищи Т |          | переда пі даппы |               |                      |       |       |

|-----------|----------|-----------------|---------------|----------------------|-------|-------|

| Мнемоника | Операнды | Описание        | Англоязычная  | Содержание           | Флаги | Циклы |

|           |          |                 | версия        | операции             |       |       |

| MOV       | Rd, Rr   | Перемещение     | Move          | Rd ←Rr               | -     | 1     |

|           |          | между           | Between       |                      |       |       |

|           |          | регистрами      | Registers     |                      |       |       |

| MOVW      | Rd, Rr   | Скопировать     | Copy Register | Rd+1:Rd ←            | -     | 1     |

|           |          | пару регистров  | Word          | Rr+1:R               |       |       |

| LDI       | Rd, K    | Загрузить       | Load          | $Rd \leftarrow K$    | -     | 1     |

| *         |          | непосредственно | Immediate     |                      |       |       |

|           |          | значение        |               |                      |       |       |

| LD        | Rd, X    | Загрузить       | Load Indirect | $Rd \leftarrow (X)$  | -     | 2     |

|           |          | косвенно        |               |                      |       |       |

| LD        | Rd, X+   | Загрузить       | Load Indirect | $Rd \leftarrow (X),$ | -     | 2     |

|           |          | косвенно,       | and Post-Inc. | $X \leftarrow X + 1$ |       |       |

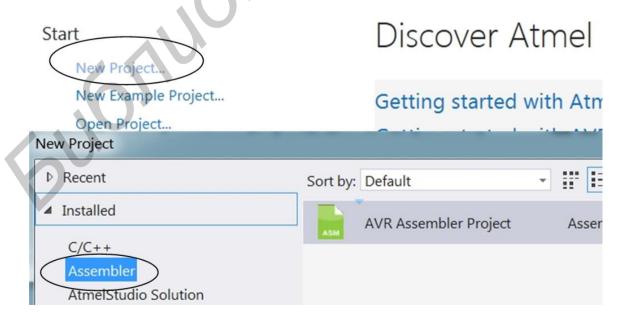

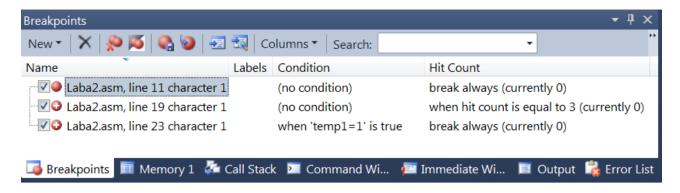

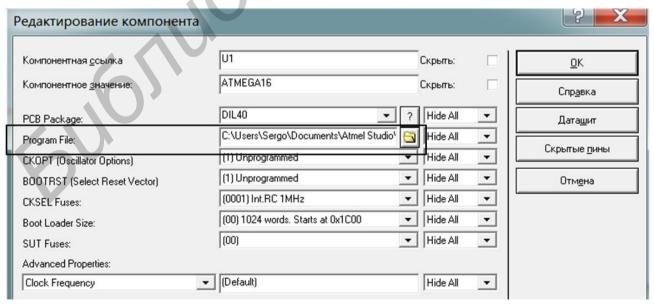

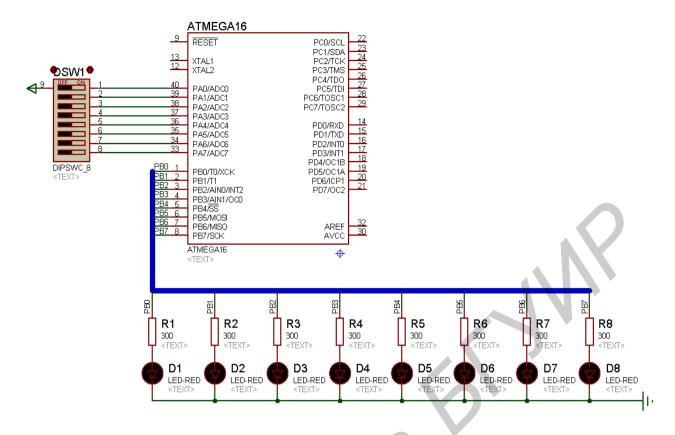

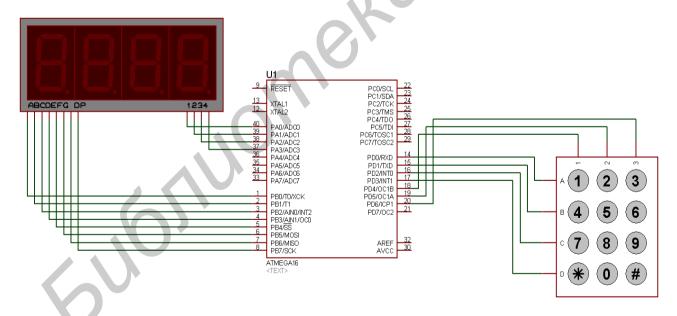

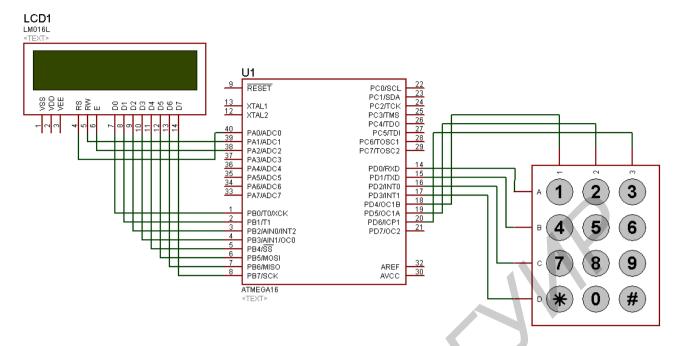

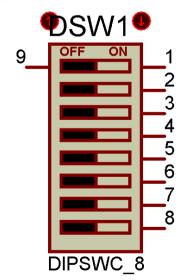

|           |          | инкрементировав |               |                      |       |       |